开关在CPU上的位置请参考图6-60。开关1为禁止向CPU写入,禁止控制指令开关,将其置于OFF侧为禁止解除。5)单击“关闭”按钮,关闭“清除PLC内存”对话框,完成CPU内存的清空操作。......

2023-06-16

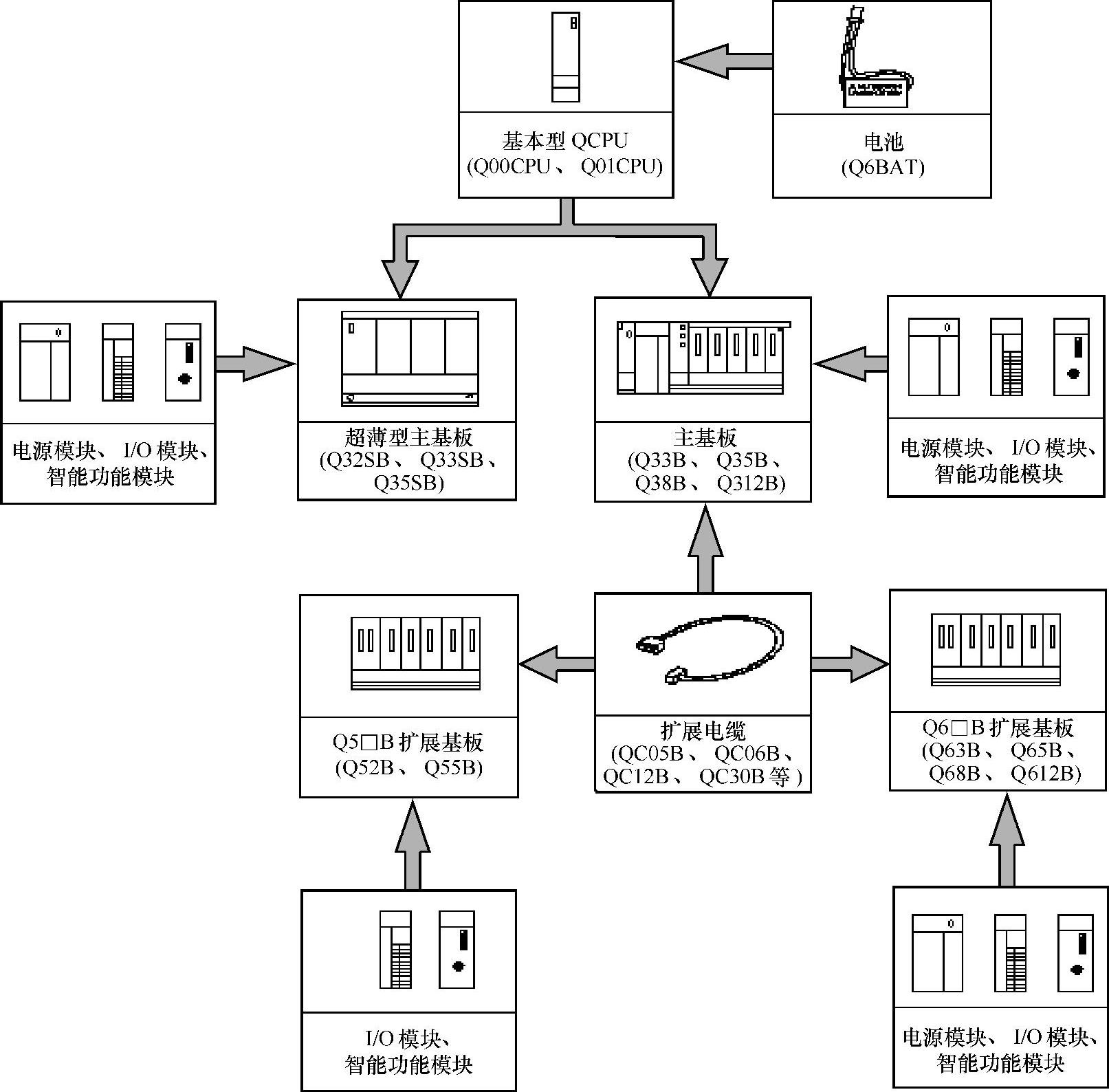

前面详细地说明了组成系统的各个基本要素:基板、电源模块、CPU模块、I/O模块、智能功能模块。本节将要叙述的系统配置是以基本型CPU和高性能型CPU系统结构来说明的。

1.基本型CPU

(1)采用Q00J型CPU的系统构成(见图2-10)

图2-10 采用Q00J型CPU的系统构成

Q00J型CPU是CPU模块、电源模块、主基板(5插槽)一体的CPU。最多安装2级的扩展基板,最多可以安装16块I/O模块、智能功能模块,I/O点数为256(X/Y0~X/YFF),不支持USB编程通信。

(2)采用Q00/Q01型CPU的系统构成(见图2-11)

图2-11 Q00/Q01型CPU的系统构成

Q00/Q01型CPU是安装在主基板上的单个CPU模块,最多安装4级扩展基板,最多能安装24块I/O模块和智能功能模块,I/O点数为1024,也不支持USB编程通信。

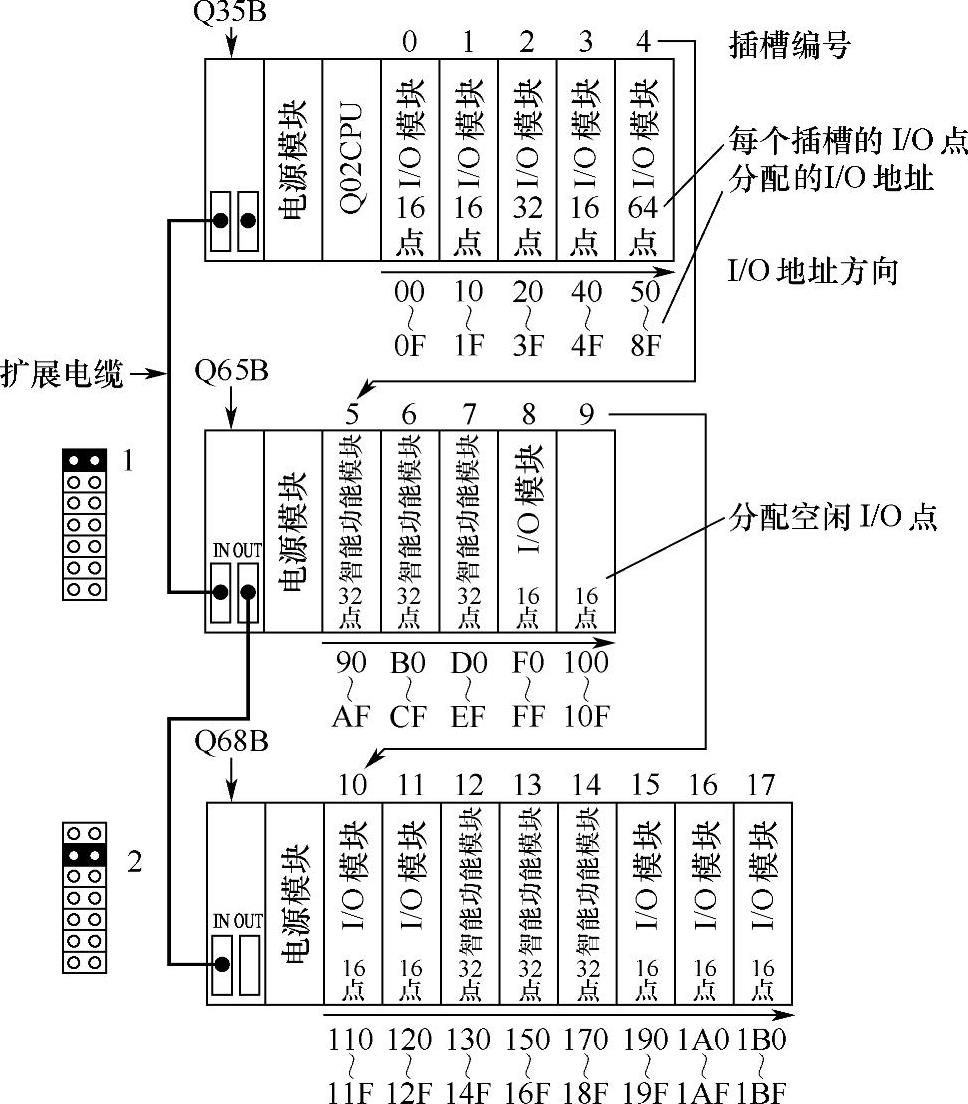

(3)扩展连接

采用Q00型CPU的Q系列PLC的扩展连接如图2-12所示。图2-12所示为选用Q68B型8插槽扩展基板与Q65B型5插槽扩展基板进行2级扩展的连接实例。

Q00J型/00型/01型PLC进行扩展连接时应注意以下6点:

1)扩展电缆的总延长距离在13.2m以内。

2)超薄型主基板上不可连接扩展基板。

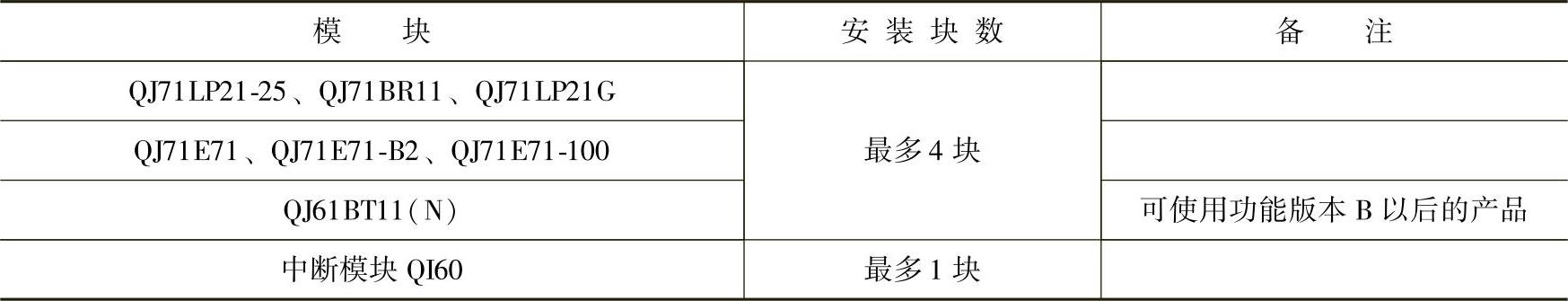

3)有安装块数限制的模块见表2-9。

图2-12 采用Q00型CPU的Q系列PLC的扩展连接图

表2-9 有安装块数限制的模块(一)

4)扩展级数的设置采用升序,防止同一编号的重复使用。

5)基板与GOT连接时,GOT也算是一级。

6)基本型CPU不支持USB编程通信。

2.高性能型CPU

(1)高性能型Q系列PLC的基本系统构成(见图2-13)

高性能型PLC的CPU是安装在主基板上的单个CPU模块,与基本型PLC的CPU相比,可以控制最多4096点I/O点。如果和CC-Link等远程I/O网络并用,那么可以控制最多8192点I/O点。

最多可以连接7级扩展基板,可以使用合计64个I/O插槽,支持USB编程通信(Q02除外)。

此外,与基本型的主要区别是它可以使用扩展基板连接A1S系列模块(A1S PLC是小A系列PLC,它已逐步停产并由Q系列PLC替换,具体可参考第15章A系列PLC如何转化成Q系列PLC)。

图2-13 高性能型Q系列PLC的基本系统构成图

(2)扩展连接

以高性能型Q02CPU的Q系列PLC的扩展连接为例如图2-14所示。

图2-14所示为选用Q68B型8插槽扩展基板与Q65B型5插槽扩展基板进行2级扩展的连接实例。

Q02(H)/Q06H/Q012H/Q25H进行扩展连接时应注意以下8点:

1)主基板、扩展基板上可以安装的I/O模块/智能功能模块总数为64。

2)扩展基板的Q6□B/Q5□B和QA1SB6□B/QA65B可自由组合,但合计最多7块(含主基板最多8块)。

3)Q6□B/Q5□B/QA1S6□B/QA65B可以自由组合,但是Q6□B/Q5□B的扩展号请务必要设置为比QA1S6□B/QA65B扩展号更大的编号。

4)扩展的总延长距离在13.2m以内。

5)高性能型Q系列PLC能够自动地识别所连接的主基板、扩展基板的插槽数,并进行I/O号的分配。

图2-14 采用高性能型Q02CPU的Q系列PLC的扩展连接图

6)Q02CPU不支持USB编程通信。

7)有安装块数限制的模块见表2-10。

表2-10 有安装块数限制的模块(二)

8)远程I/O站用的MELSECNET/H模块(QJ72BR15、QJ72LP25-25、QJ72LP25G)应安装在主基板的CPU插槽中。

有关三菱电机中大型可编程序控制器应用指南的文章

开关在CPU上的位置请参考图6-60。开关1为禁止向CPU写入,禁止控制指令开关,将其置于OFF侧为禁止解除。5)单击“关闭”按钮,关闭“清除PLC内存”对话框,完成CPU内存的清空操作。......

2023-06-16

S7-1200 PLC有一个内部电源,为CPU、信号模块、信号扩展板、通信模块提供电源,并且也可以为用户提供24 V电源。传感器24 V电源与外部24 V电源应当供给不同的设备,否则将会产生冲突。如果S7-1200 PLC系统的一些24 V电源输入端互联,此时可用一个公共电路连接多个M端子。某工程项目经统计I/O点数为20个DI,直流24 V输入,10个DO中继电器输出8个,两个DC输出,一路模拟量输入一路模拟量输出,选用S7-1200 PLC,CPU选型如下。表2-3 电源功率的计算......

2023-06-15

在多CPU系统中,多CPU控制各自的相应模块,互相之间需要进行信息的交换。图10-5 多CPU系统的自动刷新原理假设系统的CPU1在B0~B1F之间设定了32点的自动刷新,CPU2在B20~B3F之间执行32点的自动刷新,如图10-6所示。图10-6 多CPU设置那么在CPU1的END处理期间,执行的处理过程为图10-5中的1.和4.,即:1)CPU1的B0~B1F传输软元件数据被传送到CPU1的自动刷新区(1.)。图10-7 多CPU系统FROM/TO指令图10-7表述的意思如下:1)用TO指令写入数据到PLC1的用户区(1.)。......

2023-06-16

下面用一个实例来介绍如何组建多CPU系统,以及如何利用CPU间的自动刷新功能进行数据的传送。图10-11 多CPU系统的自动刷新示意图PLC顺序控制CPU侧的设置如下:1)图10-12所示为设置M软元件的自动刷新范围。运动控制CPU侧的设置如下:打开运动控制CPU对应的程序编写软件MT Developer,进入多CPU设置画面,进行相应的设置。当Q02HCPU的M3为ON时,退出SFC程序。......

2023-06-16

诊断缓冲区包含由CPU或具有诊断功能的模块所检测到的事件和错误等。诊断缓冲区中记录以下事件:CPU的每次模式切换,如上电、切换到STOP模式、切换到RUN模式等,以及每次诊断中断。最上面的条目包含最新发生的事件。诊断缓冲区条目由以下部分组成:编号、日期和时间以及事件等,如图4-32所示。事件1记录了最近时刻的事件,依次查看各个事件,综合这些事件信息对CPU停机的原因进行分析判断。......

2023-06-15

当进行多CPU系统的配置时,需要注意以下4点:1)一个多CPU系统最多可以放置4个CPU,其中必须要有一个PLC顺序控制CPU。2)各CPU之间不能留有空槽位。在进行多CPU系统的配置时,一般可以按照以下步骤进行:1.硬件配置在基板上把CPU按规定分别插好,然后把用到的各种模块也插到基板上。图10-3 多CPU的I/O分配图10-4 多CPU系统的I/O详细设置画面......

2023-06-16

Step3.创建图16.3.4b所示的边倒圆特征1。图16.3.5 拉伸特征2图16.3.5 拉伸特征2图16.3.6 定义草图平面图16.3.6 定义草图平面图16.3.7 截面草图图16.3.7 截面草图Step5.创建图16.3.8所示的零件特征——拉伸3。Step6.创建图16.3.10所示的零件特征——拉伸4。选择下拉菜单命令,系统弹出“拉伸”对话框;选取XY基准平面为草图平面,绘制图16.3.......

2023-06-22

CPU的主要任务是保证程序的正确执行。图4-17内核结构图为了得到最大程度的性能以及并行性,AVR采用了Harvard结构,具有独立的数据和程序总线。CPU在执行一条指令的同时读取下一条指令。图4-19CPU 32个通用工作寄存器的结构2.通用寄存器寄存器文件针对AVR增强型RISC指令集做了优化。为了获得需要的性能和灵活性,寄存器文件支持以下的输入/输出方案,图4-19所示为CPU 32个通用工作寄存器的结构。......

2023-06-26

相关推荐