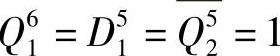

图8-26 习题8.53电路8.54 图8-27为由集成运放组成三点式振荡器原理电路,为满足相位平衡条件,试在集成运放框内填入同相和反相输入端标志。解:电路振荡频率调节范围6.59~20.7kHz。......

2023-11-24

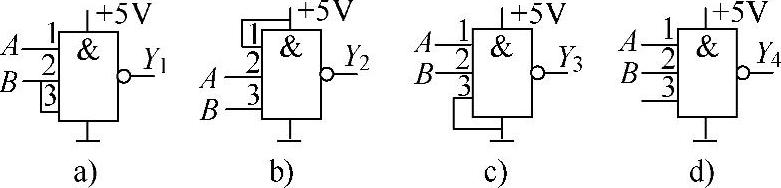

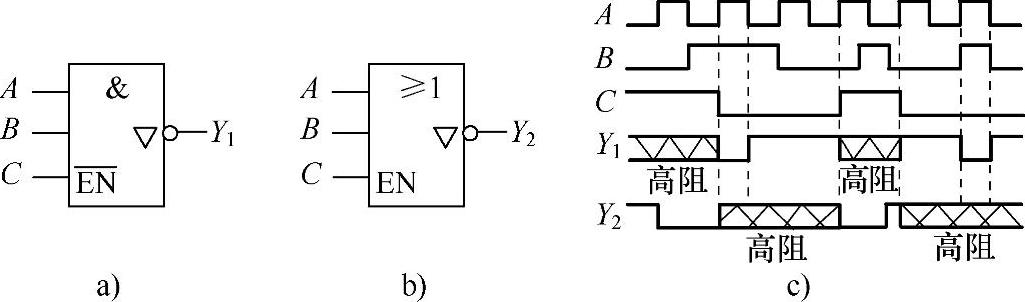

7.54 已知74LS系列三输入端与非门电路如图7-30所示,其中两个输入端分别接输入信号A、B,另一个输入端为多余引脚。试分析电路中多余引脚的接法是否正确?

解:TTL集成门电路多余输入端悬空时,相当于接高电平。与非门输入端中有一端接地时,有0出1,与非门关闭,其输出恒为1。因此,图7-30a、b、d均正确;图7-30c错。

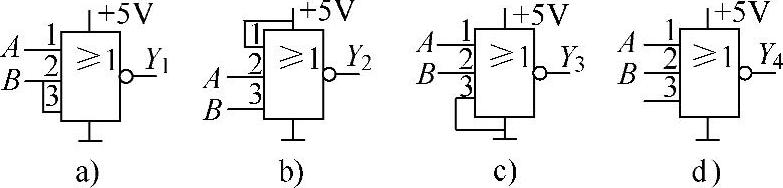

7.55 已知74LS系列三输入端或非门电路如图7-31所示,其中两个输入端分别接输入信号A、B,另一个输入端为多余引脚。试分析电路中多余引脚接法是否正确?

图7-30 习题7.54电路

图7-31 习题7.55电路

解:TTL集成电路多余输入端悬空时相当于接高电平。或非门输入端中有一端接高电平时,有1出0,或非门关闭,其输出恒为0。因此,图7-31a、c正确;图7-31b、d错。

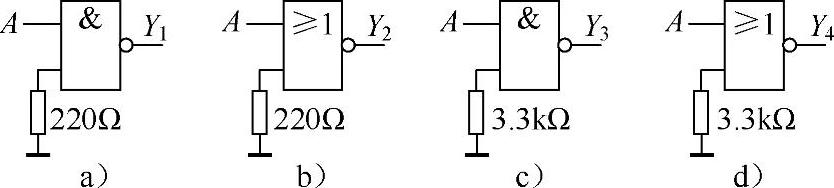

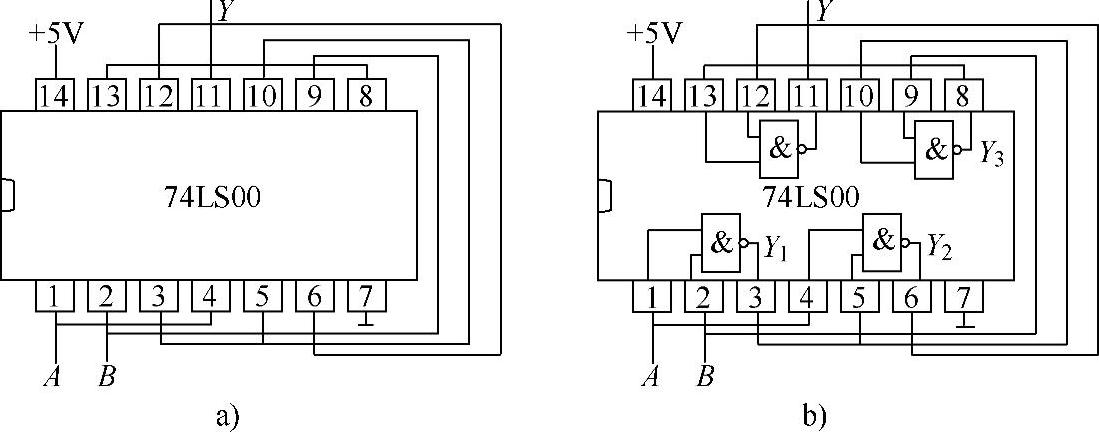

7.56 已知图7-32电路中TTL门电路的ROFF=0.8kΩ,RON=2.5kΩ,试写出输出端Y1~Y4函数表达式。

解:TTL门电路输入端负载电阻RI>RON时,相当于接高电平;RI<ROFF时,相当于接低电平。

图7-32 习题7.56电路

图7-32a、b:RI=220Ω<ROFF=0.8kΩ。因此,相当于接低电平。Y1=1,Y2=A。

图7-32c、d:RI=3.3kΩ>RON=2.5kΩ。因此,相当于接高电平。 ,Y4=0。

,Y4=0。

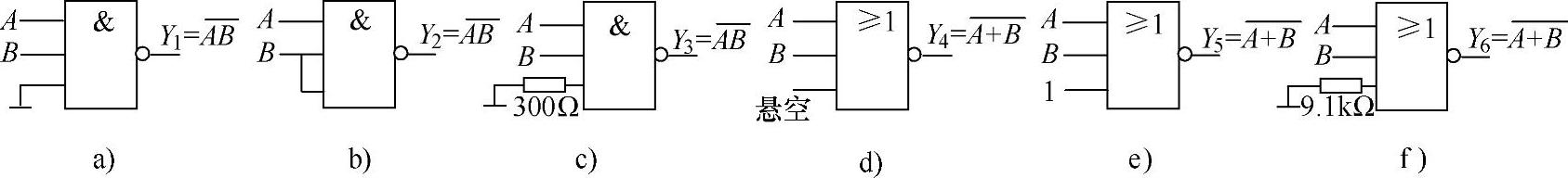

7.57 已知74LS系列三输入端门电路如图7-33所示,A、B为有效输入信号,另一个输入端为多余引脚。若要求电路输出Y1~Y6按图所求,试判断电路接法是否正确?若有错,试予以改正。

图7-33 习题7.57电路

解:TTL门电路输入端接地,相当于接低电平;输入端悬空,相当于接高电平;输入端接电阻RI>RON(74LS系列门电路RON≈6.3kΩ),相当于接高电平;输入端接电阻RI<ROFF(74LS系列门电路ROFF≈4.2kΩ),相当于接低电平。因此:

图7-33b正确。

图7-33a、c、d、e、f错。图7-33a、c可将多余输入端悬空;图7-33d、e、f可将多余输入端接地。

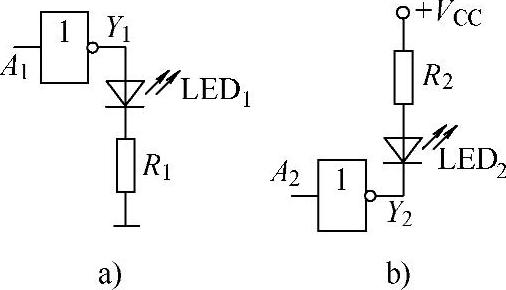

7.58 已知发光二极管驱动电路如图7-34所示,图中反相器为74LS04,设LED正向压降为1.7V,电流大于1mA时发光,最大电流为10mA,VCC=5V,试分析R1、R2的阻值范围。

图7-34 习题7.58电路

解:图7-34a中,LED1通过R1接地,因此Y1为高电平时LED1亮,A1应为低电平。74LS04输出高电平UOH=3.4V,最小值UOHmin=2.7V,为此:

因此,170Ω<R1<1kΩ。

图7-34b中,LED2通过R2接+5V,因此Y2为低电平时LED2亮,A2应为高电平。74LS04输出低电平UOL=0.35V,最大值UOLmax=0.5V,为此:

因此,295Ω<R2<2.8kΩ。

7.59 已知下列74LS系列与非门器件开门电平和关门电平,试求其噪声容限。

(1)UON=1.4V,UOFF=1.1V。

(2)UON=1.6V,UOFF=1V。

解:高电平噪声容限UNH=UOHmin-UIHmin=UOHmin-UON。

低电平噪声容限UNL=UILmax-UOLmax=UOFF-UOLmax。

74LS系列与非门UOHmin=2.7V,UOLmax=0.5V,因此:

(1)UNH=(2.7-1.4)V=1.3V。UNL=(1.1-0.5)V=0.6V。

(2)UNH=(2.7-1.6)V=1.1V。UNL=(1-0.5)V=0.5V。

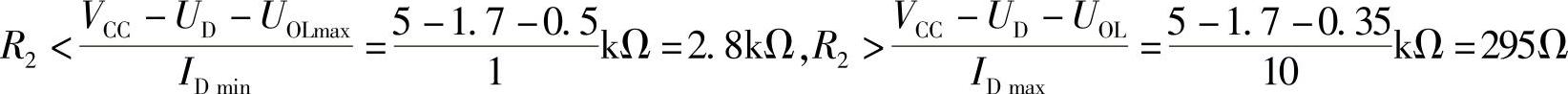

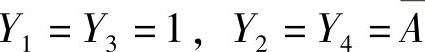

7.60 已知三态门电路和输入电压波形如图7-35所示,试画出输出电压波形。

解:图7-35a为带三态门的与非门电路,当E 低电平有效时,电路按与非门输出(有0出1,全1出0);

低电平有效时,电路按与非门输出(有0出1,全1出0); 高电平时,电路输出端呈高阻态(相当于断开)。画出输出端波形如图7-35b所示。

高电平时,电路输出端呈高阻态(相当于断开)。画出输出端波形如图7-35b所示。

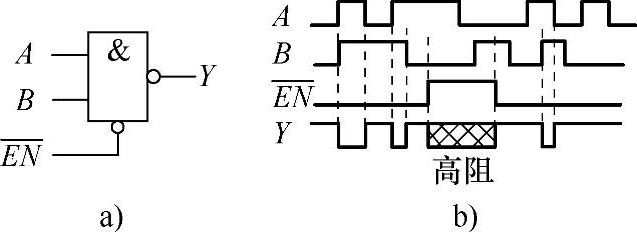

7.61 已知TTL74LS系列门电路如图7-36所示,试写出输出端Y的逻辑表达式。

图7-35 习题7.60电路和波形

图7-36 习题7.61电路

解:图7-36中的两个与非门为OC门,其中一端悬空相当于接高电平,电路连接方式为线与状态。因此:

7.62 若图7-30中与非门改成74HC系列或CMOS4000系列,再判电路接法是否正确?

解:74HC系列或CMOS4000系列均属CMOS器件。其特点是输入端不能悬空,否则将引入干扰(CMOS器件输入阻抗极大),因此,图7-30a、b正确;图7-30c、d错。

7.63 已知CMOS门电路如图7-32所示,试重新写出输出端Y1~Y4函数表达式。

解:CMOS门电路输入端相当于开路,虽在输入端内部加接保护二极管,但不存在TTL门电路的开门电阻和关门电阻效应。因此,图7-32中,多余输入端接电阻均相当于接低电平。 。

。

7.64 已知CMOS三输入端门电路如图7-33所示,试重新判断电路接法是否正确?若有错,试予以改正。

解:CMOS门电路多余输入端不能悬空,必须根据需要接高电平(接正电源电压)或接低电平(接地)。接电阻时相当于接低电平。因此:

图7-33b、f正确。

图7-33a、c、d、e错。图7-33a、c应将多余输入端接正电源电压;图7-33d、e应将多余输入端接地。

7.65 已知CMOS三态门电路和输入波形如图7-37所示,试写出Y1和Y2的逻辑表达式,并画出Y1Y2波形。

解:图7-37a:C=0, ;C=1,Y1高阻。

;C=1,Y1高阻。

图7-37b:C=0,Y2高阻,C=1, 。画出Y1Y2波形如图7-37c所示。

。画出Y1Y2波形如图7-37c所示。

图7-37 习题7.65电路和波形

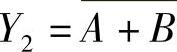

7.66 已知74LS00连接电路如图7-38a所示,A、B为输入信号,试写出输出端Y的逻辑表达式。

图7-38 习题7.66电路

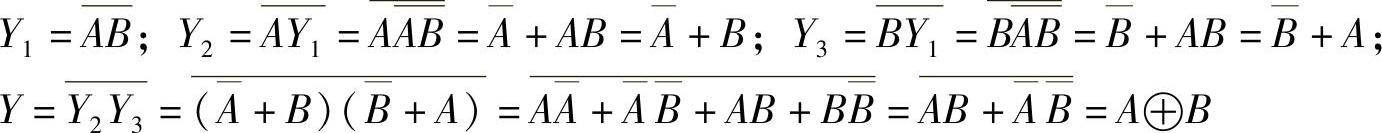

解:74LS00为TTL二输入4与非门,其逻辑电路连接可用图7-38b表示,因此:

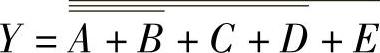

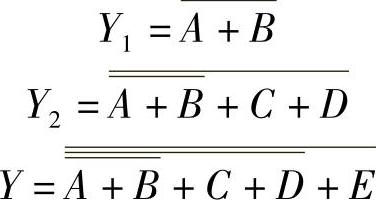

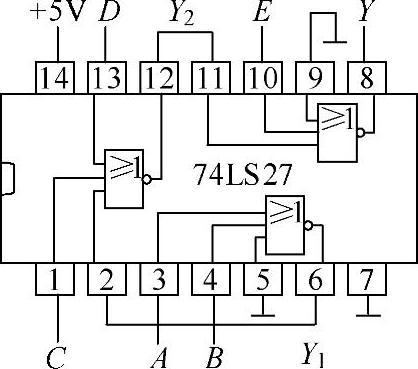

7.67 试用74LS27实现逻辑函数 。要求按图7-39中74LS27芯片引脚画出连接线路。

。要求按图7-39中74LS27芯片引脚画出连接线路。

解:画出连接线路如图7-39所示。其中:

7.68 已知逻辑电路如图7-40所示,试分析其逻辑功能。

图7-39 习题7.67电路

图7-40 习题7.68逻辑电路

解:(1)写出逻辑函数表达式。

(2)列出真值表如表7-6所示。

(3)分析逻辑功能,从表7-6可知该电路为3人多数表决电路。

表7-6 题7.68真值表

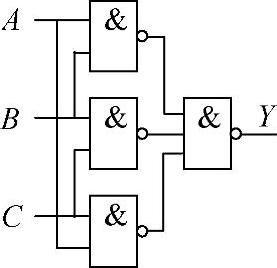

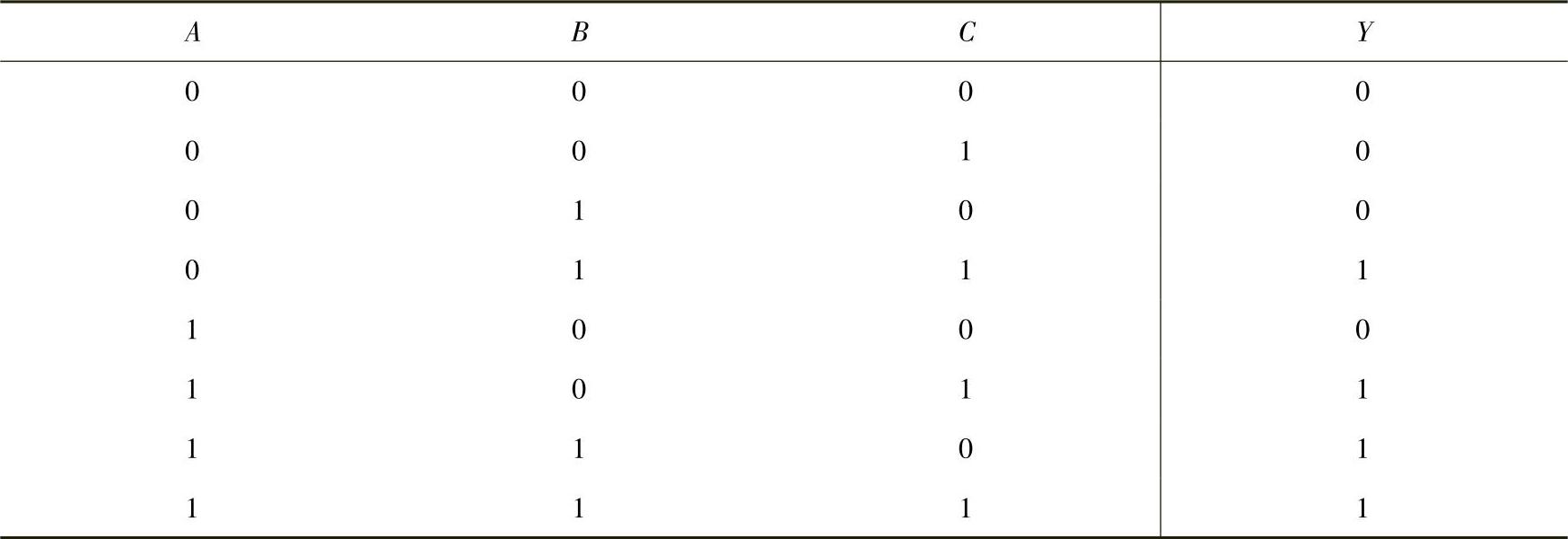

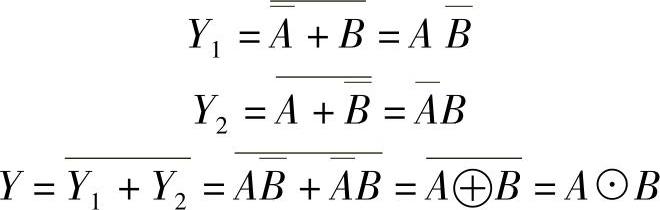

7.69 试分析图7-41所示电路逻辑功能。

解: 若对门电路熟悉,可直接得出该逻辑电路为同或门。

若对门电路熟悉,可直接得出该逻辑电路为同或门。

图7-41 习题7.69逻辑电路

若对门电路不熟悉,则可进一步列出真值表来分析判断。

7.70 已知逻辑电路如图7-42所示,试求其输出端 、EO、

、EO、 、

、 、

、 电平值。

电平值。

解:74LS148为8-3线优先编码器,编码控制端EI=0,编码有效。由于高优先权输入端I ,因此

,因此 (反码输出,原码为110=6),

(反码输出,原码为110=6), ,EO=1。

,EO=1。

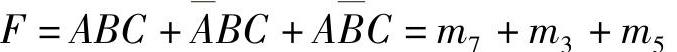

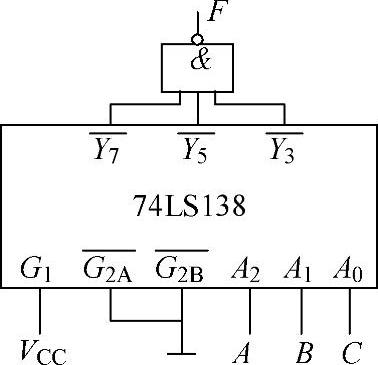

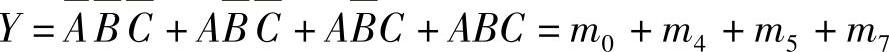

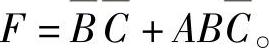

7.71 试应用74LS138和门电路实现逻辑函数: 。

。

解:

画出逻辑电路如图7-43所示,74LS138的 通过一个与非门输出;输入信号ABC接地址输入端A2A1A0(A是高位),控制端全部有效,即G1接VCC,

通过一个与非门输出;输入信号ABC接地址输入端A2A1A0(A是高位),控制端全部有效,即G1接VCC, 、

、 接地。

接地。

图7-42 习题7.70逻辑电路

图7-43 习题7.71逻辑电路

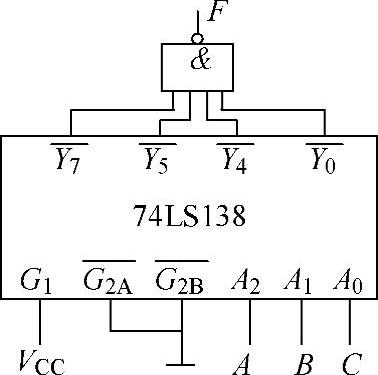

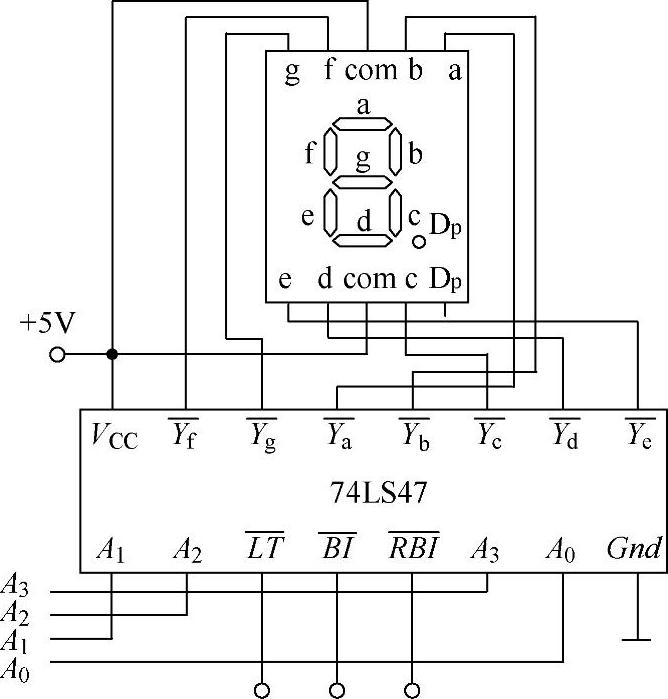

7.72 试应用74LS138和门电路实现逻辑函数:

解:

画出逻辑电路如图7-44所示。

7.73 试应用74LS138和门电路实现逻辑函数:

解:

画出逻辑电路如图7-45所示。

图7-44 习题7.72逻辑电路

图7-45 习题7.73逻辑电路

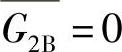

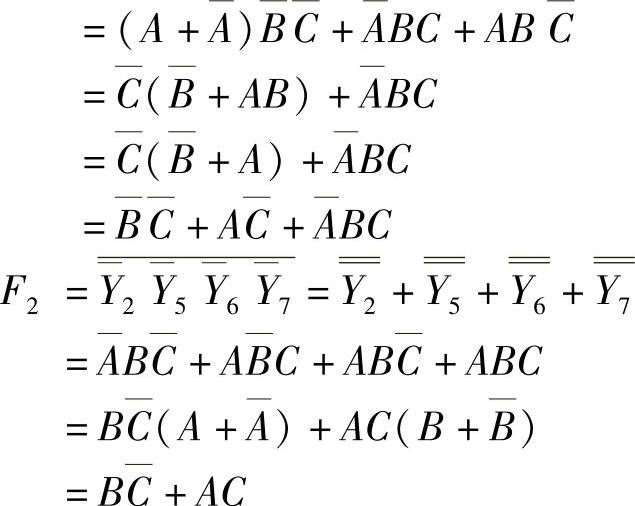

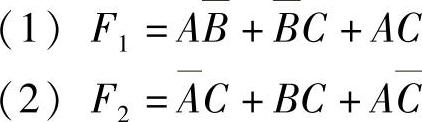

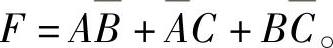

7.74 已知逻辑电路如图7-46所示,试写出F1F2最简与或表达式。

图7-46 习题7.74逻辑电路

解:74LS138为3-8线译码器,A2A1A0为地址输入端,G1、 、

、 为控制端,

为控制端, 为输出端。根据图7-46,G1=1,

为输出端。根据图7-46,G1=1,

,控制端有效,芯片处于译码状态。应有:

,控制端有效,芯片处于译码状态。应有:

7.75 试用一片74LS138辅以门电路同时实现下列函数。

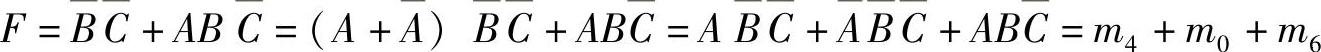

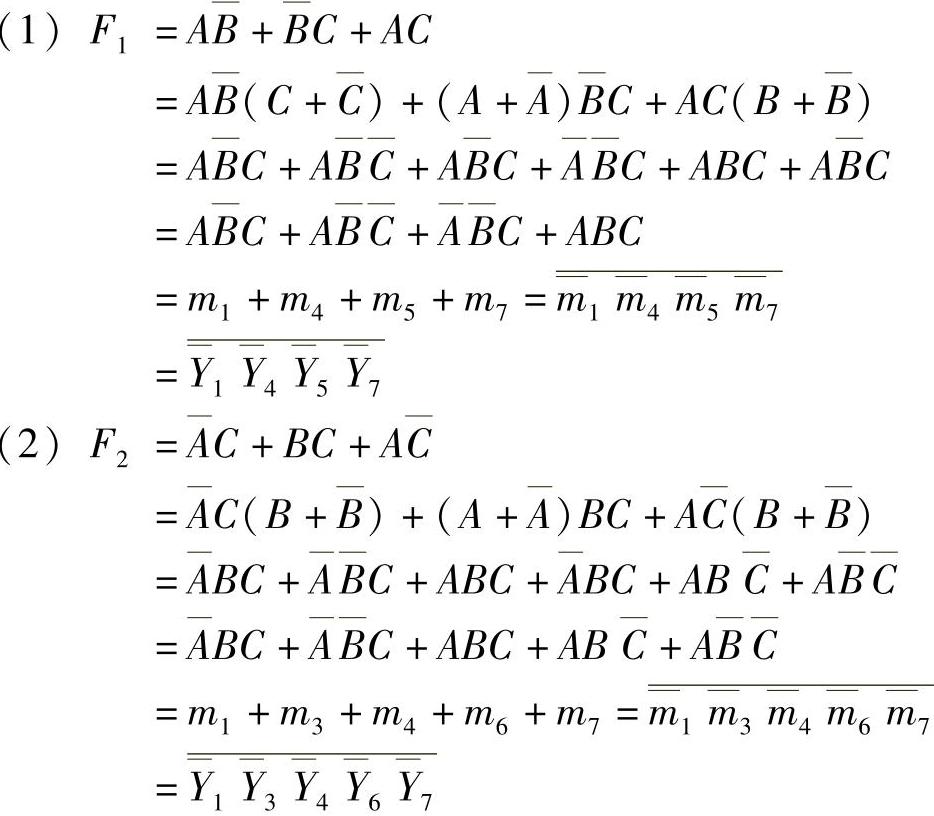

解:先将其变换为最小项表达式:

据此,画出本题所求逻辑电路如图7-47所示。

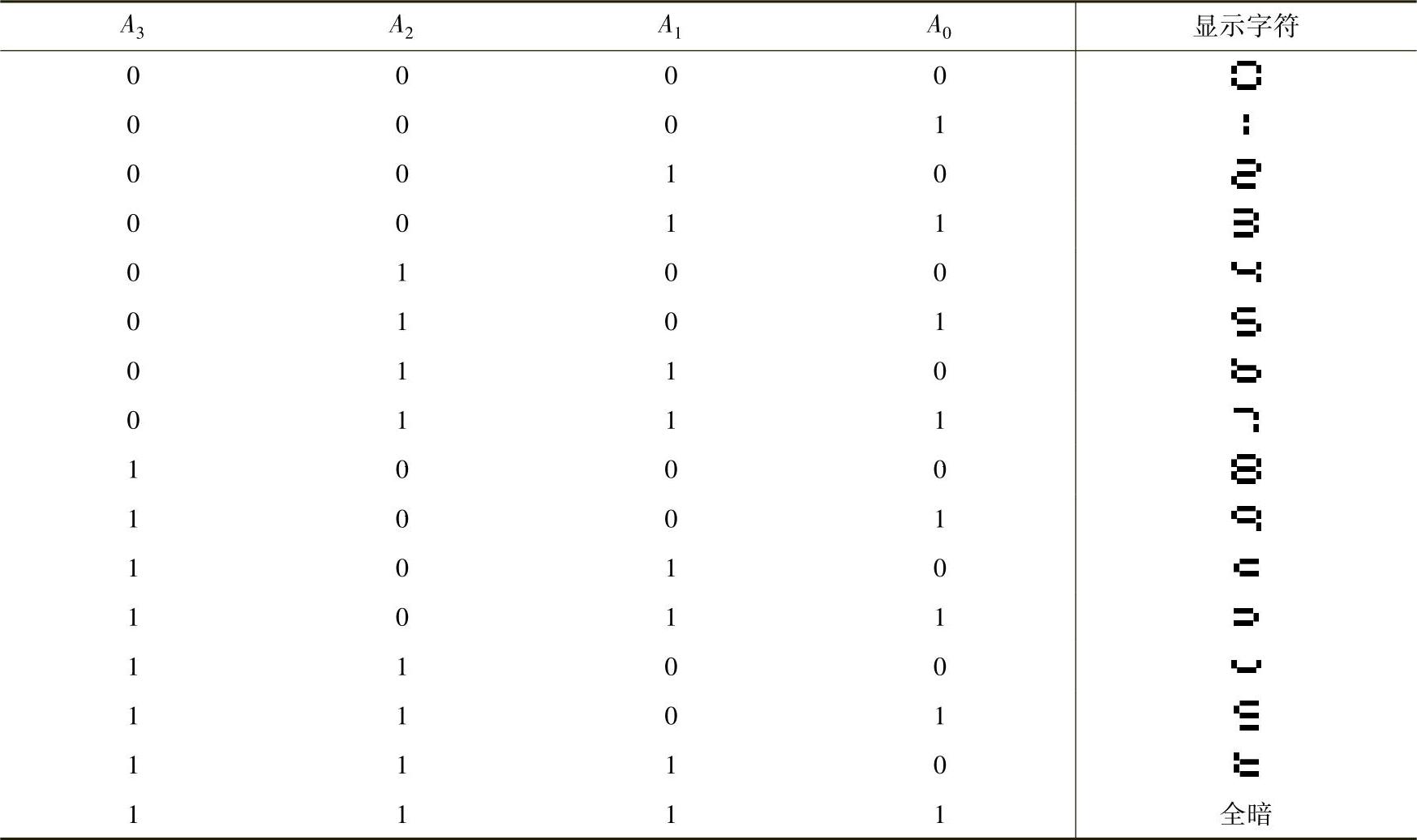

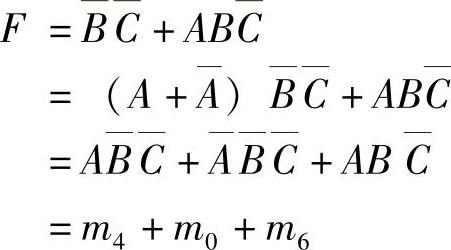

7.76 试用一片74LS47和一位共阳LED数码管组成译码显示电路。要求:

(1)按图7-48在面包板上连接电路。

(2) (接地),

(接地), (接+5V),观察显示情况。

(接+5V),观察显示情况。

(3) ,A3~A0依次接0000~1111,观察显示情况,并填写表7-7。

,A3~A0依次接0000~1111,观察显示情况,并填写表7-7。

(4)若需使数字显示闪烁,应如何处理?

解:(1)按图7-48在面包板上连接电路。

图7-47 习题7.75逻辑电路

(2)显示 。

。 为灯测试,

为灯测试, 为消隐,

为消隐, T有效

T有效 无效时,全亮。

无效时,全亮。

(3)A3~A0依次接0000~1111时,显示情况如表7-7所示。

(4)若需使数字显示闪烁,将 端接一脉冲方波,可使显示闪烁。脉冲方波频率即闪烁频率,方波频率不能过高,以人的视觉能感受为宜。实验时,BI端可轮流接地和接+5V,或用开关通断切换。

端接一脉冲方波,可使显示闪烁。脉冲方波频率即闪烁频率,方波频率不能过高,以人的视觉能感受为宜。实验时,BI端可轮流接地和接+5V,或用开关通断切换。

表7-7 习题7.76数据表

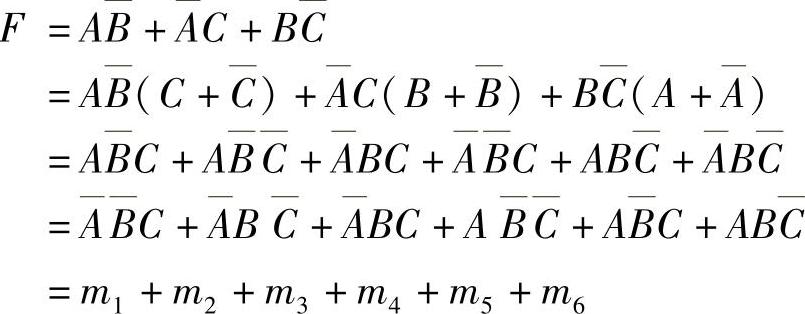

7.77 试应用数据选择器74LS151实现逻辑函数。

解:

画出逻辑电路如图7-49所示。74LS151地址端A2A1A0依次接ABC;选通端ST接地;输出端Y接F;数据端D0~D7接法:最小项未出现项,相应D端接地;出现项,相应D端接+VCC。显然,用74LS151比题7.73用74LS138构成的逻辑电路要简单。

图7-48 一位74LS47译码显示电路

图7-49 习题7.77逻辑电路

7.78 试应用数据选择器74LS151实现组合逻辑函数:

解:

画出组合逻辑电路如图7-50所示。

7.79 3人多数表决实验。试分别按图7-51和图7-52两种方法在面包板上连接电路。表决输入端接+5V表示赞成,接地表示否决(每一输入端不能悬空,悬空表示接高电平)。表决通过,表决指示灯亮;否则灯暗。观察表决实验结果是否符合要求?

图7-50 习题7.78逻辑电路

图7-51 74LS1383人多数表决电路

图7-52 74LS1513人多数表决电路

解:见图7-51,用3-8线译码器74LS138和4输入端双与非门74LS22;见图7-52,用8选1数据选择器74LS151;按图分别连接电路。

A2A1A0有任意3端或2端接+5V,表决指示灯亮,其余情况(全部接地或只有一端接+5V),灯暗。

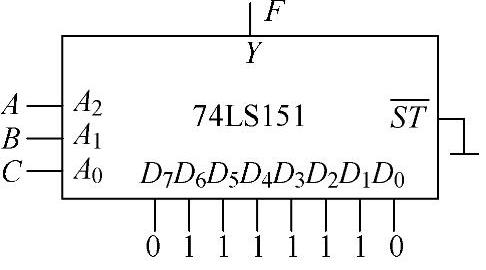

7.80 已知CMOS4位超前进位加法器CC4008引脚图如图7-53所示,其功能与74LS283相同。试用两片CC4008按图7-54在面包板上连接线路,组成8位二进制加法器。并按表7-8分别置入AB两个加数实验数据,其中1接5V,0接地。用万用表逐位测试两片CC4008S3~S0和CO对地电压数据,并填入表7-8。

解:按图7-54连接线路,实验测试数据填入表7-8。

图7-53 CC4008引脚图

图7-54 两片CC4008组成8位加法器

表7-8 8位加法器实验数据

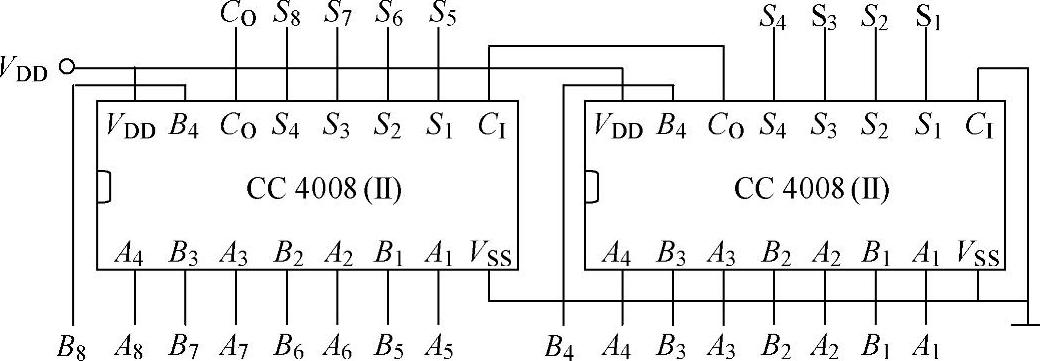

7.81 已知上升沿JK触发器CP、J、K波形如图7-55a所示,试画出JK触发器输出端Q波形(设初态Q=0)。

解:画出JK触发器输出端Q波形如图7-55b所示。

①CP1上升沿,JK=10,Q=1。

②CP2上升沿,JK=01,Q=0。

③CP3上升沿,JK=11, 。

。

④CP4上升沿,JK=01,Q=0。

⑤CP5上升沿,JK=01,Q=0。

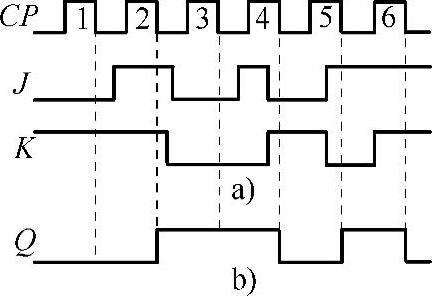

7.82 已知下降沿触发JK触发器CP、J、K波形如图7-56a所示,试画出其输出端Q波形(设初态Q=0)。

解:画出JK触发器输出端Q波形如图7-56b所示。

图7-55 习题7.81波形

图7-56 习题7.82波形

①CP1下降沿,JK=01,Q=0。

②CP2下降沿,JK=11,Q=1(取反)。

③CP3下降沿,JK=00,Q=1(不变)。

④CP4下降沿,JK=01,Q=0。

⑤CP5下降沿,JK=10,Q=1。

⑥CP6下降沿,JK=11,Q=0(取反)。

7.83 已知边沿型JK触发器CP、J、K输入波形如图7-57a所示,试分别按上升沿触发和下降沿触发画出其输出端Q波形(设初态Q为0)。

解:上升沿触发输出波形Q′如图7-57b所示。

①CP1上升沿,JK=01,Q′=0。

②CP2上升沿,JK=00,Q′=0(不变)。

③CP3上升沿,JK=11,Q′=1(取反)。

④CP4上升沿,JK=10,Q′=1。

⑤CP5上升沿,JK=11,Q′=0(取反)。

⑥CP6上升沿,JK=00,Q′=0(不变)。

⑦CP7上升沿,JK=10,Q′=1。

图7-57 习题7.83波形图

下降沿触发输出波形Q″如图7-57c所示。

①CP1下降沿,JK=01,Q″=0。

②CP2下降沿,JK=10,Q″=1。

③CP3下降沿,JK=11,Q″=0(取反)。

④CP4下降沿,JK=10,Q″=1(虽然在CP4=1期间,K有一个窄脉冲,但下降沿时JK=10,K窄脉冲不起作用)。

⑤CP5下降沿,JK=00,Q″=1(不变)。

⑥CP6下降沿,JK=01,Q″=0。

⑦CP7下降沿,JK=00,Q″=0(不变)。

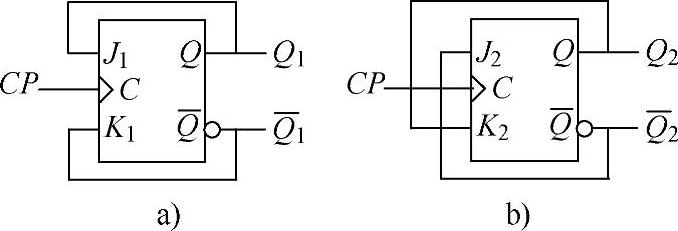

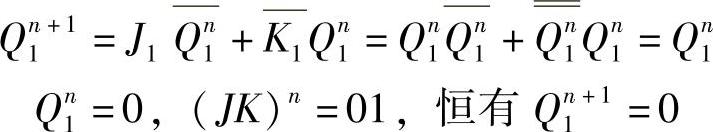

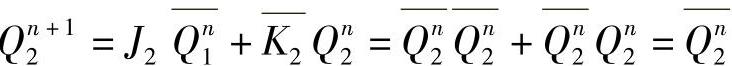

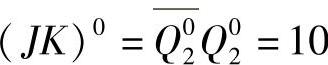

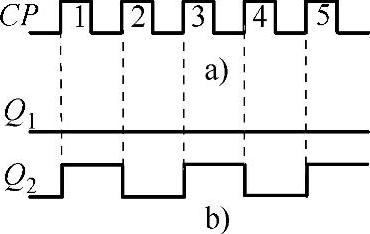

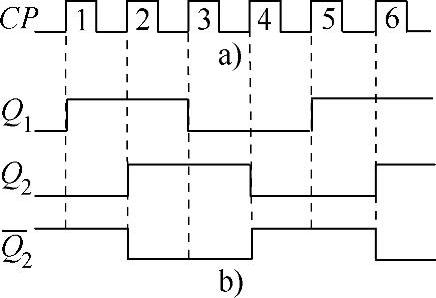

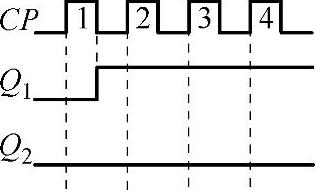

7.84 已知电路如图7-58所示,CP波形如图7-59a所示,设初态Q1=Q2=0,试画出Q1Q2波形。

图7-58 习题7.84电路

解:(1)见图7-58a。

(2)见图7-58b。

构成T′触发器,对CP二分频。

若分析每一CP上升沿后Q2波形,可得:

①CP1上升沿,Q02=0, ,Q12=1。

,Q12=1。

②CP2上升沿,Q12=1, ,Q22=0。

,Q22=0。

③CP3上升沿,Q22=0, ,Q32=1。

,Q32=1。

④CP4上升沿,Q32=1, ,Q42=0。

,Q42=0。

⑤CP5上升沿,Q42=0, ,Q52=1。

,Q52=1。

据此,画出Q1Q2波形如图7-59b所示。

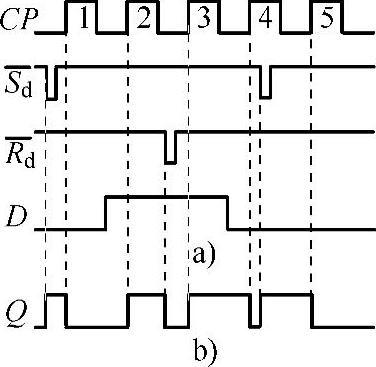

7.85 已知D触发器CP、 、

、 和D波形如图7-60a所示,试画出输出端Q波形(设初态Q=0)。

和D波形如图7-60a所示,试画出输出端Q波形(设初态Q=0)。

解:参阅例7-8。

图7-59 习题7.84波形

图7-60 习题7.85波形图

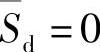

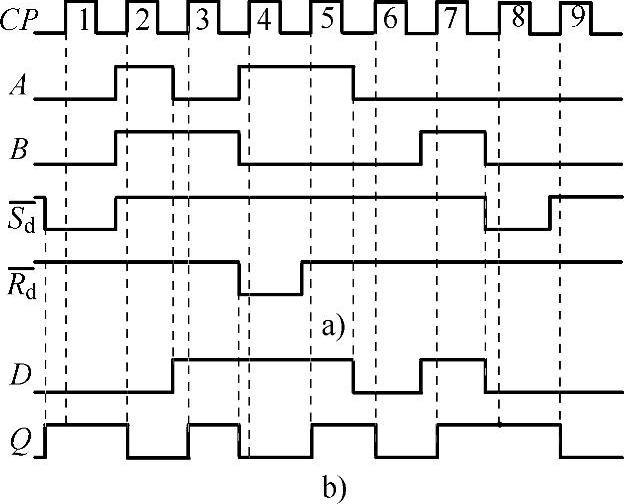

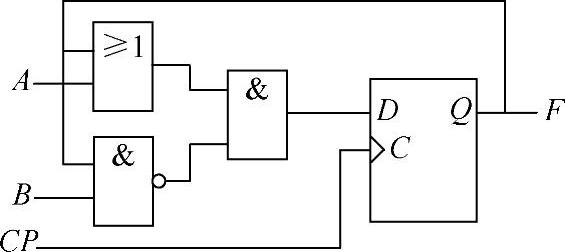

7.86 已知电路如图7-61所示,输入信号CP、A、B、Sd、Rd波形如图7-62a所示,试画出D端和Q端波形(设初态D=0、Q=0)

解:D=A⊕B,AB相同出0,相异出1。先画出D端波形如图7-62b所示。

Q端波形:①初始Q=0; ,Q=1。

,Q=1。

②CP1上升沿, ,Q=1,与D=0无关。

,Q=1,与D=0无关。

(www.chuimin.cn)

(www.chuimin.cn)

图7-61 习题7.86电路

③CP2上升沿,D=0,Q=0。

④CP3上升沿,D=1,Q=1。

⑤CP4之前, ,Q=0;CP4上升沿,由于

,Q=0;CP4上升沿,由于 ,D=1不起作用。

,D=1不起作用。

⑥CP5上升沿,D=1,Q=1。

⑦CP6上升沿,D=0,Q=0。

⑧CP7上升沿,D=1,Q=1。

⑨CP8之前, ,Q=1;CP8上升沿,由于

,Q=1;CP8上升沿,由于 ,D=0不起作用。

,D=0不起作用。

⑩CP9上升沿,D=0,Q=0。

据此画出Q端波形如图7-62b所示。

7.87 已知D触发器电路如图7-63所示,CP波形如图7-64a所示,试画出Q1、Q2波形(设初态Q01=Q02=0)。

图7-62 习题7.86波形图

图7-63 习题7.87电路

解:初态Q01=Q02=0,则D01=Q02=1

①CP1上升沿, ;Q21=D02=Q01=0,

;Q21=D02=Q01=0, 。

。

②CP2上升沿, ;Q22=D21=Q11=1,

;Q22=D21=Q11=1, 。

。

③CP3上升沿, ;Q32=D22=Q21=1,

;Q32=D22=Q21=1, 。

。

④CP4上升沿, ;Q42=D32=Q31=0,

;Q42=D32=Q31=0, 。

。

⑤CP5上升沿, ;Q52=D42=Q41=0,

;Q52=D42=Q41=0, 。

。

⑥CP6上升沿, ;Q62=D52=Q51=1,

;Q62=D52=Q51=1, 。

。

据此,画出Q1、Q2、 波形图如图7-64b所示。

波形图如图7-64b所示。

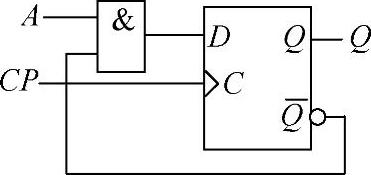

7.88 已知电路如图7-65所示,试判断其逻辑功能。

解:

图7-64 习题7.87波形

图7-65 习题7.88电路

与JK触发器状态方程 相比相同。因此该电路功能为JK触发器,A为J端,B为K端。

相比相同。因此该电路功能为JK触发器,A为J端,B为K端。

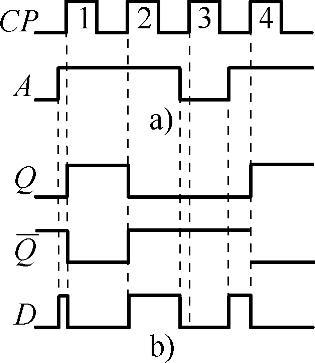

7.89 已知电路如图7-66所示,输入波形CP和A,如图7-67a所示。设D触发器初态Q=0,试画出Q端波形。

图7-66 习题7.89电路

图7-67 习题7.89波形

解:从图7-66得:

①CP1前, 。

。

②CP1上升沿,Q1=D0=1, ,

, 。

。

③CP2上升沿,Q2=D1=0, ,

, 。

。

后A2=0, 。

。

④CP3上升沿,Q3=D2=0, ,

, 。

。

后A3=1, 。

。

⑤CP4上升沿,Q4=D3=1, ,

, 。

。

据此,画出Q波形如图7-67b所示。

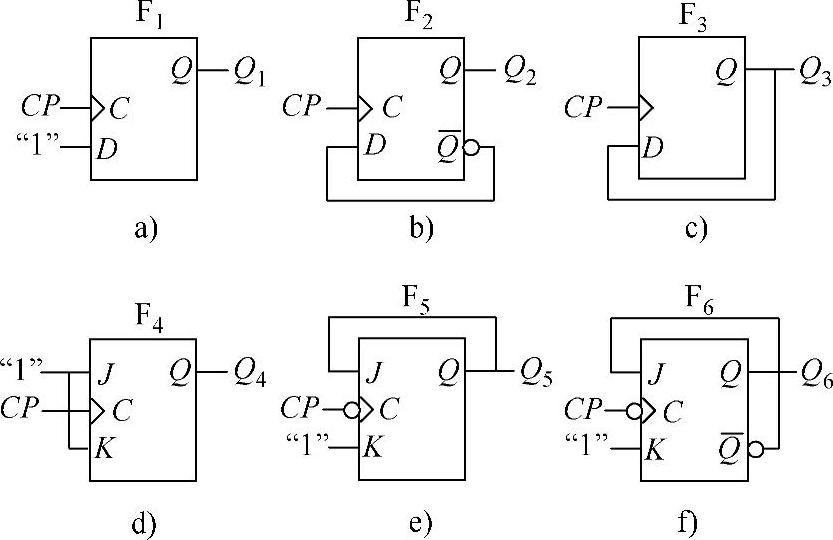

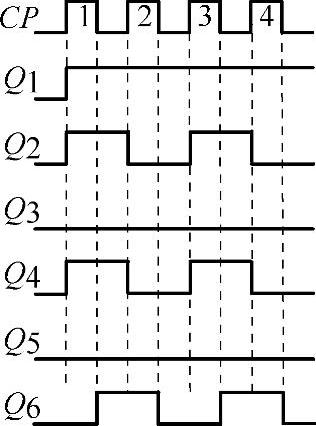

7.90 已知电路如图7-68所示,CP脉冲如图7-69所示,试画出Q端波形(设Q1~Q6初态均为0)。

解:(1)图7-68a,由于D=1,CP1上升沿,Q=1并保持。

(2)图7-68b,D与 连接,构成T′触发器,对CP二分频。

连接,构成T′触发器,对CP二分频。

(3)图7-68c,D=Q=0,始终保持。

(4)图7-68d,J=K=1,构成T′触发器,对CP二分频。

(5)图7-68e,J=0,K=1,Q=0,始终保持。

(6)图7-68f, ,K=1,构成T′触发器,对CP二分频,但为CP下降沿触发。

,K=1,构成T′触发器,对CP二分频,但为CP下降沿触发。

据此,画出图7-68a、b、c、d、e、f电路波形如图7-69所示。

图7-68 习题7.90电路

图7-69 习题7.90波形

7.91 已知电路如图7-70所示,CP脉冲如图7-71所示,试分别画出Q端波形(设初态Q1=Q2=0)。

解:(1)图7-70a,JK触发器,CP下降沿触发,初态JK=11,CP1下降沿,Q=1;次态JK=10,始终保持Q=1。

(2)图7-70b,D触发器,虽D=1,但强置端R ,

, ,恒Q=0。

,恒Q=0。

据此,画出Q1、Q2波形图如图7-71所示。

图7-70 习题7.91电路

图7-71 习题7.91波形

7.92 已知电路分别如图7-72和图7-73所示,设初始Q1=Q2=0,试画出Q1Q2波形。

解:参阅例7-9。

图7-72 习题7.92电路

图7-73 习题7.92电路

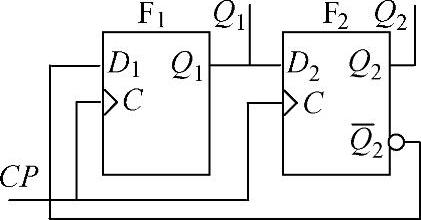

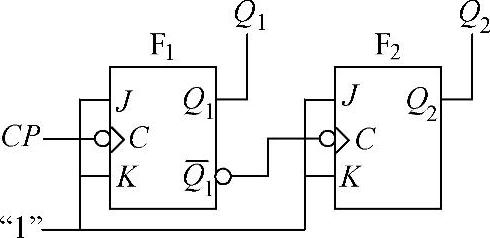

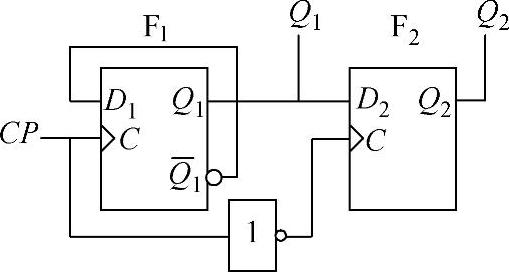

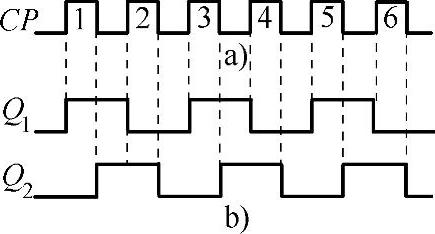

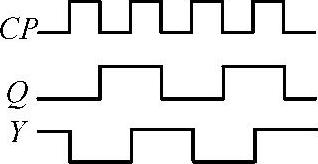

7.93 已知由74LS74组成的电路如图7-74所示,CP波形如图7-75a所示,试画出Q1Q2波形。

解:74LS74为双D触发器,按图7-74,F1组成T′触发器,对CP二分频。F2对Q1作D触发器,但时钟脉冲为 ,即在CP下降沿触发。据此,画出Q1Q2波形如图7-75b所示。

,即在CP下降沿触发。据此,画出Q1Q2波形如图7-75b所示。

图7-74 习题7.93电路

图7-75 习题7.93波形

7.94 已知电路如图7-76所示,CP波形如图7-77a所示,试画出Q、 、A、B波形。

、A、B波形。

解:图7-76中,D触发器构成T′触发器( 与D短接),因此:

与D短接),因此:

据此,画出Q、Q、A、B波形图如图7-77b所示。

图7-76 习题7.94电路

图7-77 习题7.94波形

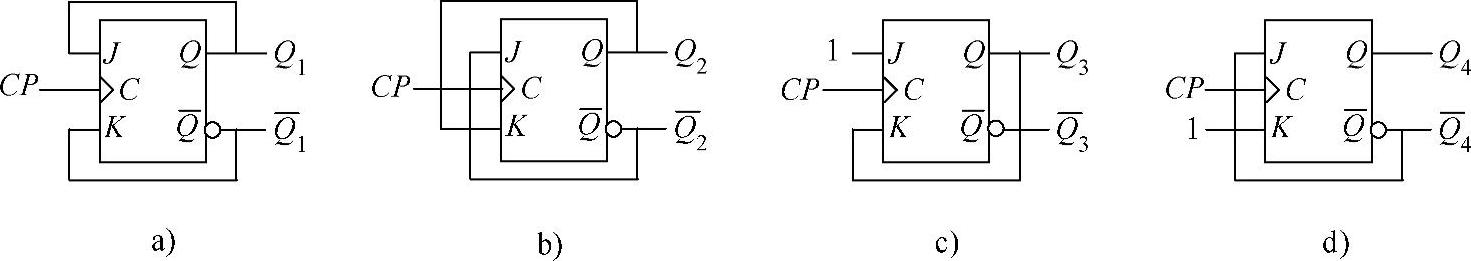

7.95 已知电路如图7-78所示,试求Q1、Q2、Q3和Q4表达式。

图7-78 习题7.95电路

解:参阅例7-10。

7.96 已知触发器功能表如表7-9所示,X、Y为激励(输入)信号,Qn+1为次态输出信号,试确定它们属于何种触发器。

解:表7-9a为或非门组成的RS触发器。

表7-9 习题7.96功能表

表7-9b为JK触发器。

表7-9c为D触发器。

表7-9d为二分频电路(T触发器)。

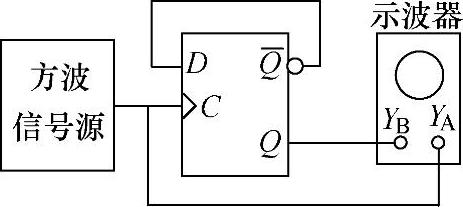

7.97 已知实验电路如图7-79所示,YA、YB为双踪示波器的信号输入端,试画出示波器显示的波形。

解:图7-79中,D触发器构成T′触发器,对CP脉冲二分频,因此YB是YA的二分频方波,如图7-80所示。

图7-79 习题7.97电路

图7-80 习题7.97波形

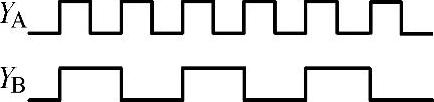

7.98 某同学用图7-81a所示集成电路组成电路,并从示波器上观察到该电路波形如图7-82所示,试问该电路是如何连接的?(画出电路连线)

解:(1)从图7-82中CP与Q波形关系看出,Q对CP二分频,因此JK触发器组成T′触发器,应J=K=1。

(2)Y为异或门,其两个输入端可能的信号只有3种:CP、Q和 ,从CP、Q、Y波形看,Y=CP☉Q,现需用异或门,因此应Y=CP⊕Q。据此,连接电路如图7-81b所示。

,从CP、Q、Y波形看,Y=CP☉Q,现需用异或门,因此应Y=CP⊕Q。据此,连接电路如图7-81b所示。

图7-81 习题7.98电路

a)元件 b)电路

图7-82 习题7.98波形

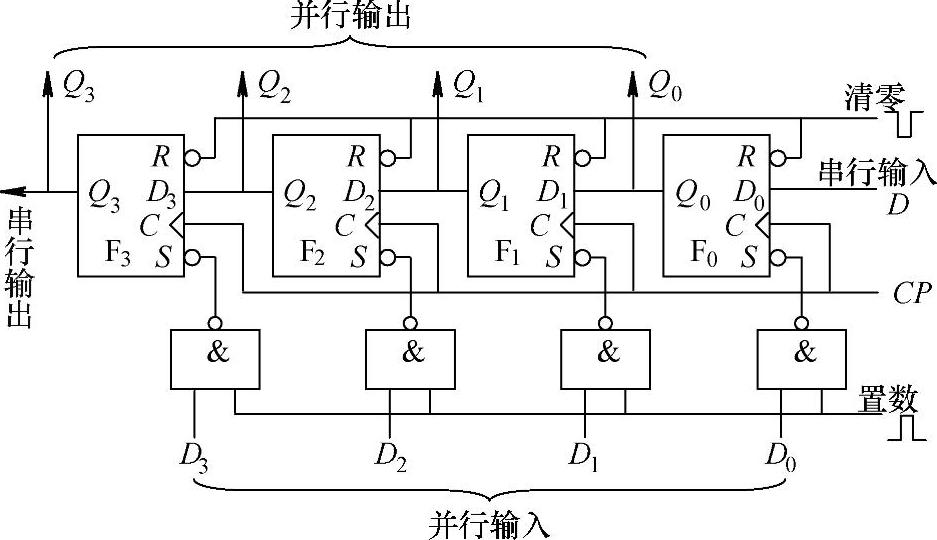

7.99 已知电路如图7-83所示,CP、R、D端波形如图7-84所示,试画出Q3Q2Q1Q0时序波形图。

图7-83 习题7.99电路图

图7-84 习题7.99时序波形图

解:画出Q3Q2Q1Q0时序波形图如图7-84所示。

7.100 已知电路同上,并行数据输入端数据D3D2D1D0=1101,串行数据输入端D=01010000,CP、R和置数脉冲如图7-85所示,试画出时序波形图。

解:画出时序波形图如图7-85所示。其中CP1~CP4,从串行输出端移出并行输入数据D3D2D1D0;CP5~CP8,从串行输出端串行输入D端数据。

7.101 已知74LS164组成串入并出电路,时钟脉冲CP、清0控制信号 和串行输入数据DS如图7-86所示,试画出并行输出端Q0~Q7时序波形。

和串行输入数据DS如图7-86所示,试画出并行输出端Q0~Q7时序波形。

解:当 有效(低电平)时,Q0~Q7端清0;时钟脉冲CP有效(上升沿)时,触发移位,串行数据依次移入Q0~Q7,如图7-86所示。

有效(低电平)时,Q0~Q7端清0;时钟脉冲CP有效(上升沿)时,触发移位,串行数据依次移入Q0~Q7,如图7-86所示。

图7-85 习题7.100时序波形图

图7-86 习题7.101时序波形图

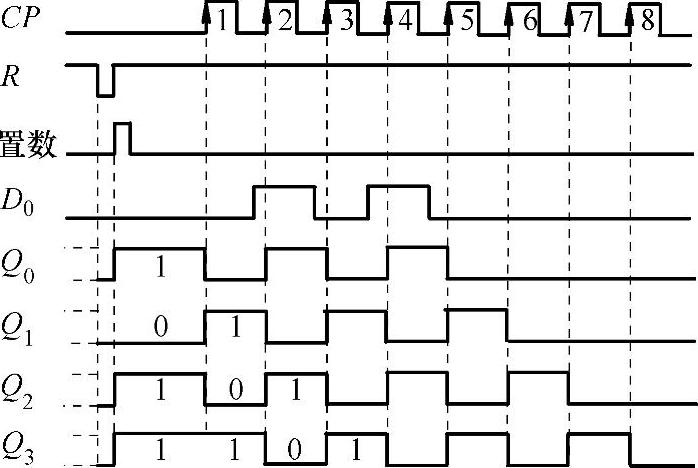

7.102 已知74LS165组成的电路如图7-87所示,控制信号CP、INH、S/L波形如图7-88所示,并行输入信号D7~D0=10110101,串行输入信号DIS=0110101,试画出串行输出端QH、 时序波形。

时序波形。

解:图7-87电路,当移位/置数控制端S/L=0时,并行置入输入信号D7~D0=10110101;CP1时,由于INH=1,电路仍保持原有状态(不移位);直至INH=0,在CP2上升沿,开始从QH端依次移出D7~D0=10110101,同时从串行输入端依次移入串行输入信号DS=01101010。至CP9,并行置入数据10110101全部移出;随后移出串行输入数据,但至CP14后,INH恢复高电平,电路进入保持状态,仅移出5位串行输入数据01101,如图7-88所示。互补输出端 时序波形与QH反相。

时序波形与QH反相。

图7-87 习题7.102电路

图7-88 习题7.102时序波形图

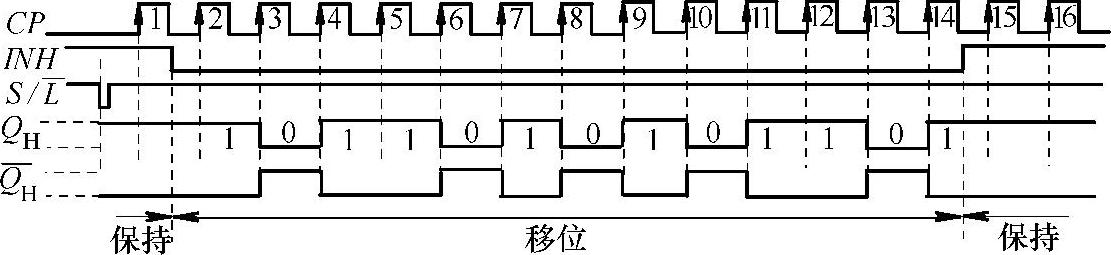

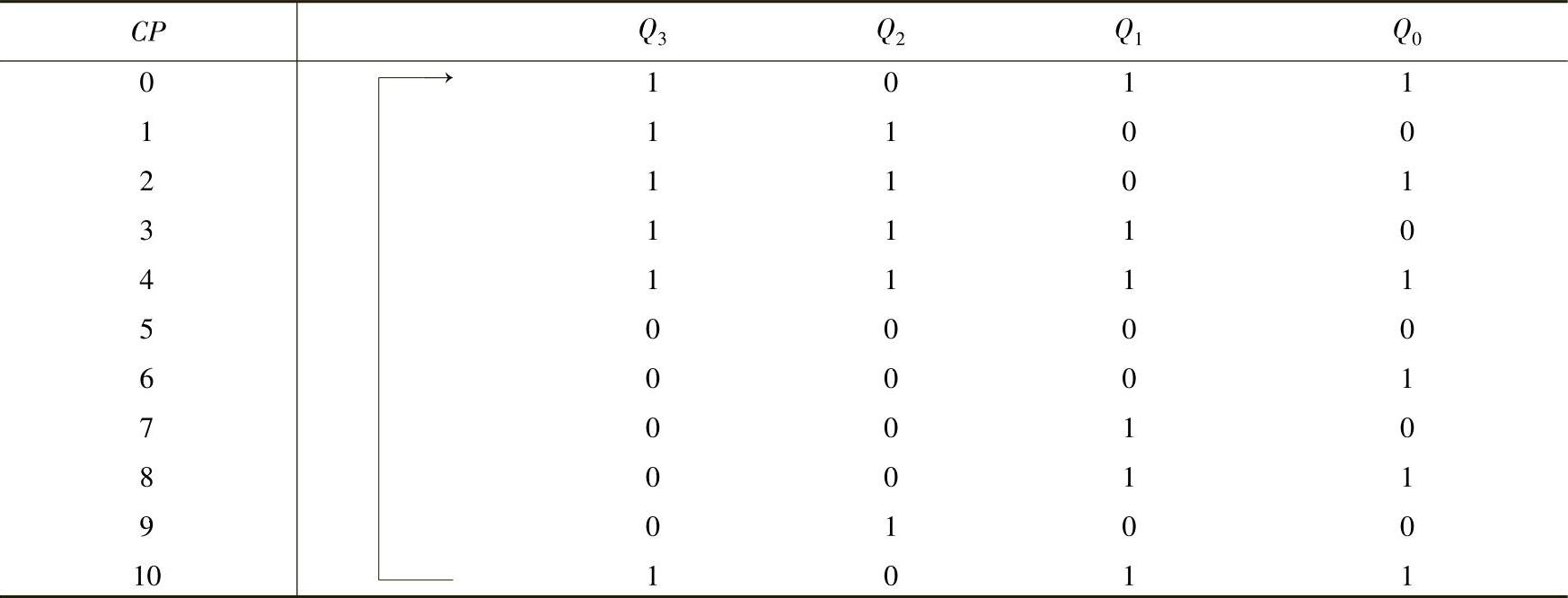

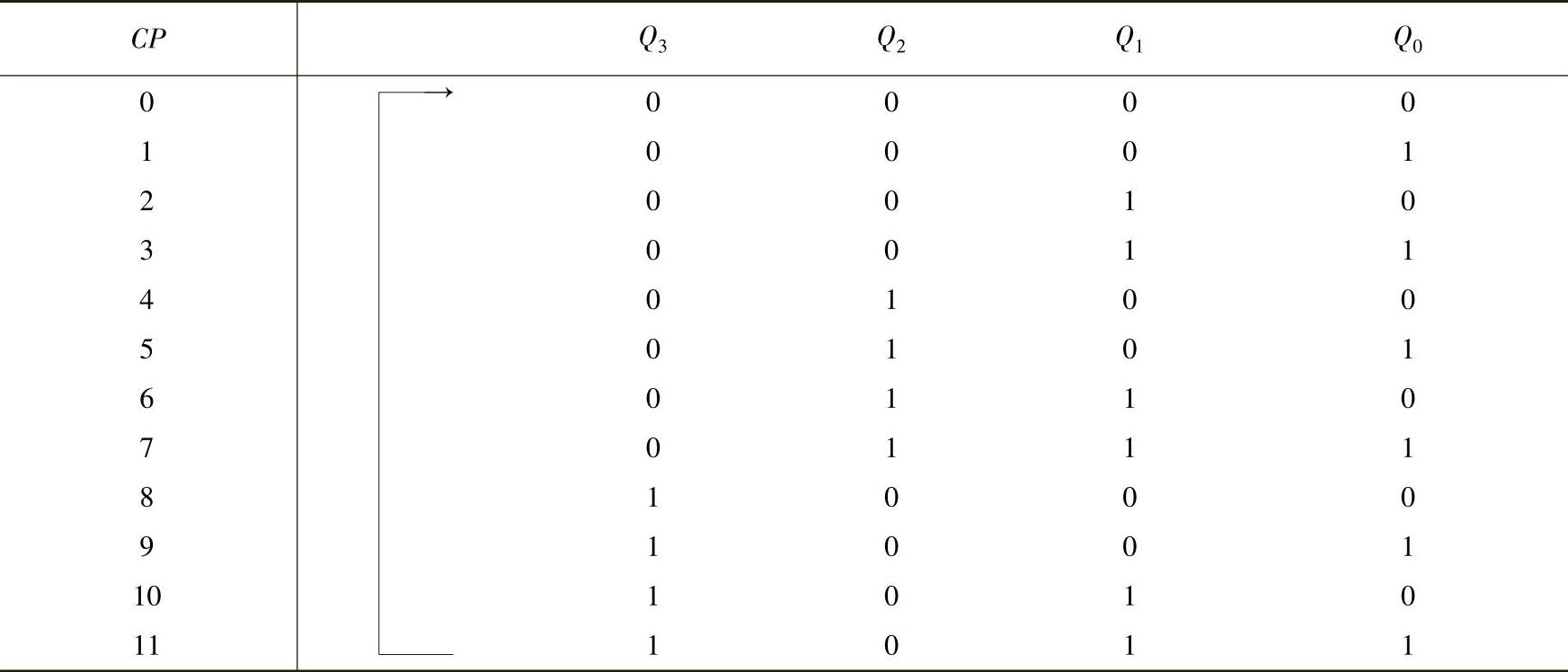

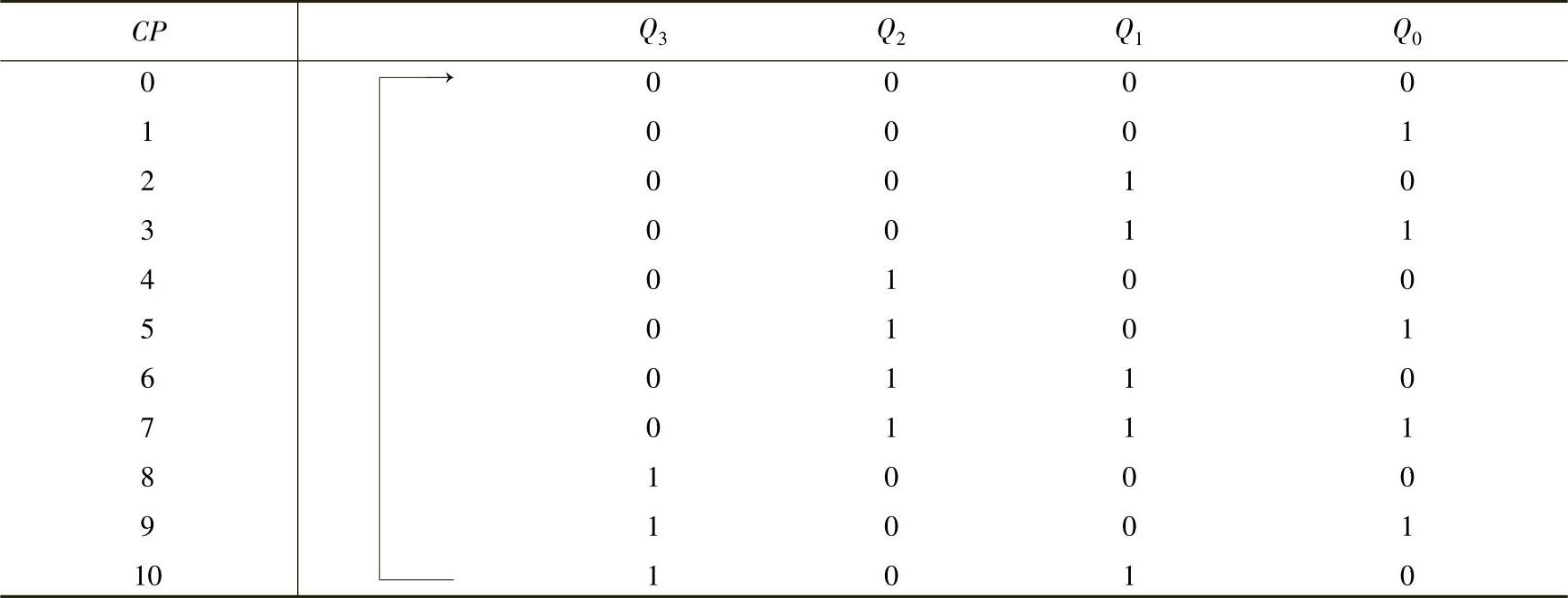

7.103 已知由74LS161组成的2421BCD码和余3BCD码的计数器如图7-89所示,试列出其状态转换表和状态转换图。

图7-89 2421、余3BCD码电路

a)2421BCD码 b)余3BCD码

解:BCD码(Binary Coded Decimal)称为二-十进制编码,除常用的8421BCD码外,还有2421、5211、5421和余3等BCD编码。

图7-89中,2421BCD码和余3BCD码电路均为反馈置数,初态为并行输入端D3D2D1D0数值。其中:

2421BCD码从初态1011开始加法计数,至1111。自动转为0000,计数至0100后,

,触发置数。

,触发置数。

余3BCD码从初态0011开始加法计数,至1100后, ,触发置数。

,触发置数。

列出两种BCD码电路的状态转换表分别如表7-10和表7-11所示,画出其状态转换图如图7-90所示。

表7-10 2421BCD码状态转换表

表7-11 余3BCD码状态转换表

图7-90 习题7.103状态转换图

a)2421BCD码 b)余3BCD码

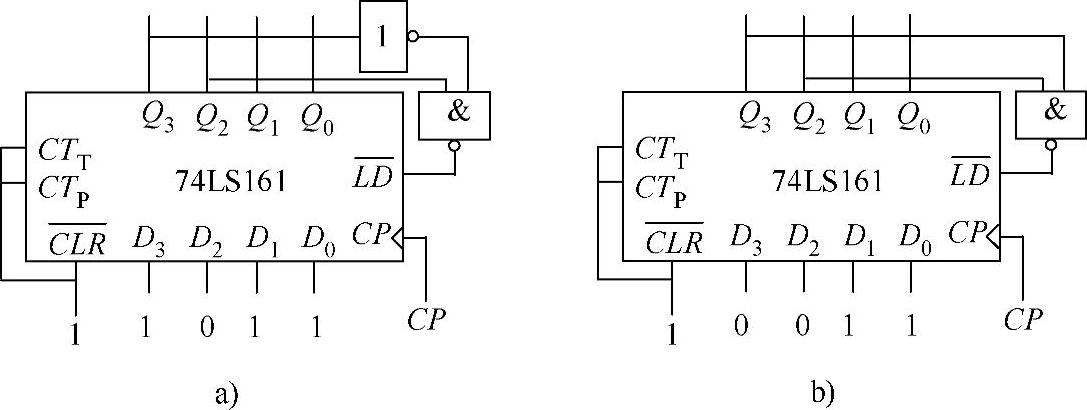

7.104 试利用74LS161组成14进制计数器。

解:参阅例7-11。

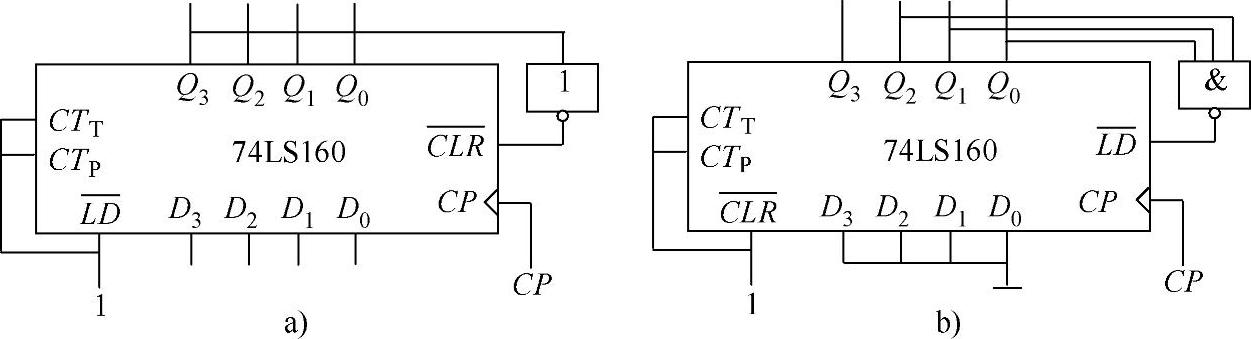

7.105 试用74LS160异步复位和同步置0功能构成八进制计数器。

解:74LS160为十进制同步可预置计数器,根据其功能表, 端为异步复位,清0与CP无关;

端为异步复位,清0与CP无关; D端为同步置数,置0与CP有关,需在CP脉冲上升沿时完成置数。

D端为同步置数,置0与CP有关,需在CP脉冲上升沿时完成置数。

图7-91a为异步复位,当Q3Q2Q1Q0计数至1000时,Q3=1,反相后使CLR=0,触发清0。

图7-91b为同步置0,当Q3Q2Q1Q0计数至0111时,Q2Q1Q0通过与非门,全1出0,使 ,在下一个CP上升沿来到时,触发置数Q3Q2Q1Q0=0000。

,在下一个CP上升沿来到时,触发置数Q3Q2Q1Q0=0000。

图7-91 习题7.105题解图

a)异步置0 b)同步置数

上述两种方法均属反馈法,用 异步清0时,N进制用N反馈;用

异步清0时,N进制用N反馈;用 同步置0时,用(N-1)反馈。

同步置0时,用(N-1)反馈。

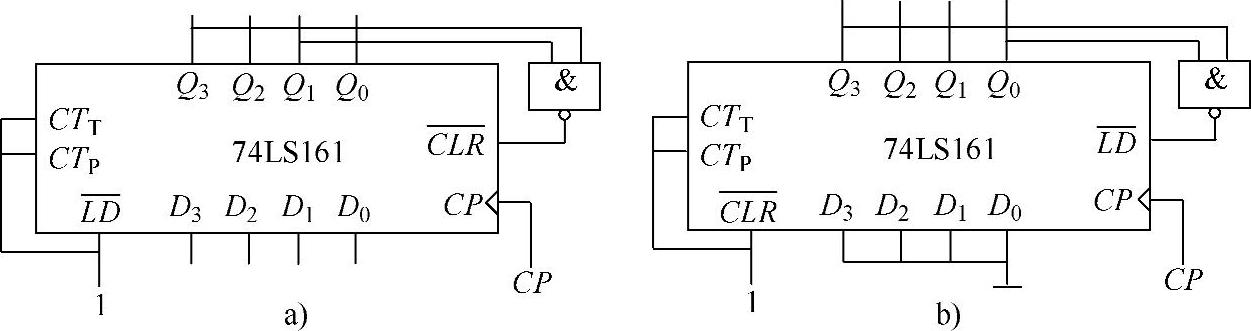

7.106 试用异步复位法和同步置位法将74LS161改为8421BCD码计数器。

解:74LS161为二进制同步可预置计数器,最大计数值为16,而8421BCD码计数器即十进制计数器,最大计数值为10。

计数范围大的计数器改为计数值小的计数器一般用反馈法,74LS161有一个复位端 (也称为清0端),不需要CP配合,因此称为“异步复位”;还有一个置数端

(也称为清0端),不需要CP配合,因此称为“异步复位”;还有一个置数端 ,需要CP配合,因此称为“同步置数”,若置数值D3D2D1D0=0000,则称为“同步置0”。画出两种电路如图7-92所示。

,需要CP配合,因此称为“同步置数”,若置数值D3D2D1D0=0000,则称为“同步置0”。画出两种电路如图7-92所示。

图7-92 8421BCD码计数器

a)反馈复位法 b)反馈置位法

需要指出的是,异步复位法用1010反馈;同步置位法用1001反馈。同步置位法因有CP参与控制,无干扰脉冲输出;异步复位法有短暂的1010状态(约10ns),可能形成干扰。

7.107 试用74LS161异步复位和同步置0构成11进制计数器,并列出状态转换表。

解:74LS161为二进制同步可预置计数器,最大计数值为16。

异步清0时,用 端,计数至N=11时反馈,复位0000。

端,计数至N=11时反馈,复位0000。

同步置0时,用 端,需要CP配合,计数至N=10时反馈,需待下一CP来到时置数。并需将预置数据输入端D3~D0接0000。

端,需要CP配合,计数至N=10时反馈,需待下一CP来到时置数。并需将预置数据输入端D3~D0接0000。

用74LS161按异步清0法和同步置0法构成的11进制计数器,分别如图7-93a、b所示。状态转换表如表7-12和表7-13所示。

表7-12 异步置0状态转换表

表7-13 同步置数状态转换表

图7-93 习题7.107题解图

a)异步清0 b)同步置数

7.108 数字钟电路中,时计数器计满24小时需复位,试用74LS160组成该计数电路。

解:图7-94即为所求电路。74LS160为十进制计数器,CP同时加到两片芯片的CP端,属并联级联方式,计数至10时CO端有一个进位脉冲,芯片I的进位CO与芯片II的CTT、CTP相接,当CTT·CTP=1时,即芯片I有进位时芯片II计数。两片芯片的C 时,即芯片IIQ3Q2Q1Q0=0010,芯片IQ3Q2Q1Q0=0100时,复位。

时,即芯片IIQ3Q2Q1Q0=0010,芯片IQ3Q2Q1Q0=0100时,复位。

7.109 试应用CC4060组成一个秒闪烁电路。

解:参阅例7-12。

7.110 已知电路如图7-95所示,试分析电路功能。

图7-94 模24计数器

图7-95 习题7.110电路

解:CC4017为十进制计数/分频器,其功能如表7-14所示。按下按钮S,CC4017复位,并对CP脉冲计数,Y0~Y5依次输出高电平,6个发光二极管依次点亮,至Y6输出高电平时,INH=1,CC4017保持(灯全灭),直至再次按下按钮S,重复上述过程。因此,该电路功能是按一次S,6个LED灯依次点亮一次。但CP脉冲不能太快,否则看不出6个LED灯依次点亮。

表7-14 CC4017功能表

7.111 已知某存储器共有下列数量的位存储单元,试分别用位存储单元和字节存储单元(1字节=8位)表示其存储容量。

(1)512。(2)8192。(3)65536。(4)262144。

解:用位存储单元表示:

(1)512=1024×0.5=0.5Kbit。

(2)8192=1024×8=8Kbit。

(3)65536=1024×64=64Kbit。

(4)262144=1024×256=256Kbit。

用字节(1B=8bit)存储单元表示:

(1)512=64B。

(2)8192=1024×8=1KB。

(3)65536=1024×8×8=8KB。

(4)262144=1024×8×32=32KB。

7.112 已知下列存储器的存储容量,试计算其位存储单元数量。

(1)16Kbit。(2)4KB。(3)128Kbit。(4)256B。

解:(1)16Kbit=16×1024=16384bit。

(2)4KB=4×1024×8=32768bit。

(3)128Kbit=128×1024=131072bit。

(4)256B=256×8=2048bit。

7.113 数据同题7.111,试计算能区分(选通)上述字节存储单元的地址线根数。

解:(1)26=64因此区分64B需6根地址线。

(2)210=1K,需10根地址线。

(3)213=8K,需13根地址线。

(4)215=32K,需15根地址线。

7.114 已知下列存储器地址线根数,试计算其能选通的最大字节存储单元数。

(1)5。(2)8。(3)11。(4)13。

解:(1)25=32,5根地址线能选通32B存储单元。

(2)28=256,8根地址线能选通256B存储单元。

(3)211=2048,11根地址线能选通2048B存储单元。

(4)213=8192,13根地址线能选通8192B存储单元。

有关计算机电路基础学习指导与习题解答的文章

图8-26 习题8.53电路8.54 图8-27为由集成运放组成三点式振荡器原理电路,为满足相位平衡条件,试在集成运放框内填入同相和反相输入端标志。解:电路振荡频率调节范围6.59~20.7kHz。......

2023-11-24

图1-33 习题1.32电路解:分别画出图1-33所示各电路便于观察的串、并联结构的等效电路如图1-34所示。图1-35 习题1.33电路解:参阅例1-1。图1-37 习题1.35电路1.36 将图1-38a、c所示电流源等效转换为电压源。图1-45 习题1.43电路1.44 试应用分压公式求图1-46所示电路未知电压。......

2023-11-24

图1-4 叠加定理示意图注意事项:①叠加定理只能用来计算线性电路的电流和电压,不适用于非线性电路或计算线性电路功率。②所谓一个电源单独作用,其他电源不作用是指不作用的电源置零,即电压源短路,电流源开路。......

2023-11-24

集成运放组成框图如图4-5c所示,主要有输入级、中间级、输出级和偏置电路组成。图4-5 集成运放电路符号和组成框图a)电路符号 b)集成运放旧符号 c)组成框图集成运放中的信号。集成运放主要参数。是开环时集成运放差模输入电阻,Rid越大越好。是集成运放输出电压为0时,加在两个输入端的补偿电压,反映了集成运放两个输入端的不对称性。......

2023-11-24

场效应晶体管属于单极型晶体管,即只有一种载流子参与导电。3个电极D、G和S分别称为漏极、栅极和源极,相当于晶体管的C、B和E极。图3-8 N沟道场效应晶体管转移特性图3-9 N沟道场效应晶体管输出特性曲线a)结型 b)耗尽型MOS c)增强型MOS饱和漏极电流IDSS。结型:约107Ω;MOS管:高达1015Ω。......

2023-11-24

1.单项选择题(1)D (2)B (3)B (4)D (5)C (6)D (7)A (8)B (9)D (10)C (11)B (12)A (13)C (14)B (15)C (16)B (17)A (18)D (19)B (20)D (21)B (22)D (23)D2.解答题(1)(2)(3)(4)(5)(6)(7)由得(8)由于所以(9)由于所以,x→0时,α(x)是x的三阶无穷小.(10)......

2023-10-27

相关推荐