A.尽量绕道躲避B.立即报警,停车观望C.协助保护现场,并立即报警D.加速通过,不予理睬解析:题中,A、D明显错误,先排除掉,B停车观望与题意也背道而驰,唯有答案C为给予“帮助”,符合题意。印象认定法要求考生对某知识点由印象的深刻程度来选择答案。......

2023-10-06

7.1 通常能实现“线与”功能的门电路是A。(A.OC门;B.TSL门;C.TTL与门;D.74LS与门)

7.2 (多选)TTL与(与非)门电路,多余输入端可接ABCE;TTL或(或非)门电路,多余输入端可接BDF。(A.+VCC;B.与有信号输入端并联;C.悬空;D.接地;E.接对地电阻RI>RON;F.接对地电阻RI<ROFF)

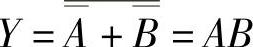

7.3 图7-25电路中,用TTL门电路能实现逻辑功能 功能的门电路是D。

功能的门电路是D。

图7-25 习题7.3电路

7.4 若电源电压为5V,有关阈值电压的说法,74LS系列门电路是D;CMOS门电路是A。(A.UTH=2.5V;B.UTH>2.5V;C.UTH<2.5V;D.UTH≈1V;E.不定)

7.5 与TTL74LS系列门电路引脚和电平均兼容的CMOS门电路是C。(A.CMOS4000系列;B.74HC系列;C.74HCT系列;D.MC14000/MC14500系列)

7.6 与TTL门电路相比,CMOS门电路的优点(多选)在于ACD。(A.微功耗;B.高速;C.抗干扰能力强;D.电源电压范围大)

7.7 图7-26电路中,能实现逻辑功能Y=A+B的电路(多选)是DEF。

图7-26 习题7.7电路

说明:A:COMS门电路多余输入引脚不能悬空(悬空为不定状态)。

B:两个反相器输出端不是OC门,不能线与。C: D:TTL门电路多余输入引脚悬空,相当于接高电平。

D:TTL门电路多余输入引脚悬空,相当于接高电平。 E:OC门可线与。

E:OC门可线与。 F:

F:

7.8 若需对50个输入信号编码,则输出编码位数至少为B个。(A.5;B.6;C.10;D.50)

7.9 若编码器编码输出位数为4位,则最多可对C个输入信号编码。(A.4;B.8;C.16;D.32)

7.10 相对于普通编码器,优先编码器对输入信号编码的特点是D。(A.只允许有一个有效输入信号;B.只允许有效输入信号为1;C.只允许有效输入信号为0;D.仅对其中一个优先等级最高的有效输入信号编码)

7.11 将给定的二进制码变换为相应(多选)的ABC功能之一者,就属于译码器。(A.另一种形式二值代码;B.显示代码;C.BCD码;D.十进制数)

7.12 74LS1383个控制端G1、 和

和 的关系为A。(A.与;B.或;C.无关;D.不定)

的关系为A。(A.与;B.或;C.无关;D.不定)

7.13 16选1数据选择器,其地址输入端至少应有B位。(A.2;B.4;C.8;D.16)

7.14 下列有关数据选择器说法正确(多选)的是AC。(A.只能传输数字信号;B.既可传输数字信号,又可传输模拟信号;C.基本功能相当于一个单刀多掷开关;D.可用于数据分配器)

7.15 8选1数据选择器,其数据输入端有D个。(A.2;B.3;C.4;D.8)

7.16 数据选择器主要应用功能(多选)有ABD。(A.从多路数据中选择一路输出;B.将并行数据变为串行数据;C.将串行数据变为并行数据;D.实现组合逻辑函数)

7.17 半加器有A;全加器有C。(A.2个输入端,2个输出端;B.2个输入端,3个输出端;C.3个输入端,2个输出端;D.3个输入端,3个输出端)

7.18 全加器与半加器的区别为B。(A.不包含异或运算;B.加数中包含来自低位的进位;C.无进位;D.有进位)

7.19 不属于FF触发器特点的是D。(A.有两个稳定状态;B.可以由一种稳定状态转换到另一种稳定状态;C.具有记忆功能;D.有不定输出状态)

7.20 基本RS触发器的功能缺陷(多选)为BD。(A.存在“空翻”现象;B.触发时刻不能同步;C.具有记忆功能;D.有不定输出状态;E.有两个稳定状态;F.具有“透明”特性)

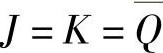

7.21 欲使JK触发器按Qn+1=1工作,可使JK触发器的输入端(多选)BCE。(A.J=K=1;B.J=1,K=0;C. ;D.J=K=0;E.J=Q,K=0)

;D.J=K=0;E.J=Q,K=0)

说明:选D时,若初态Q=0,则不符要求。

7.22 欲使JK触发器按Qn+1=0工作,可使JK触发器的输入端(多选)BCD。(A.J=K=1;B.J=0,K=Q;C.J=Q,K=1;D.J=0,K=1;E.J=K=0)

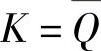

7.23 欲使JK触发器按Qn+1=Qn工作,可使JK触发器的输入端(多选)ABDE。(A.J=K=0;B.J=Q, ;C.

;C. ,K=Q;D.J=Q,K=0;E.J=0,K=Q)

,K=Q;D.J=Q,K=0;E.J=0,K=Q)

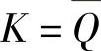

7.24 欲使JK触发器按Qn+1=Qn工作,可使JK触发器的输入端(多选)ACDE。(A.J=K=1;B.J=Q, ;C.

;C. ,K=Q;D.J=Q,K=1;E.J=1,K=Q)

,K=Q;D.J=Q,K=1;E.J=1,K=Q)

7.25 欲使D触发器按 工作,应使输入D端接D。(A.0;B.1;C.Q;D.

工作,应使输入D端接D。(A.0;B.1;C.Q;D. )

)

7.26 欲使D触发器按Qn+1=Qn工作,应使输入D端接=C。(A.0;B.1;C.Q;D. )

)

7.27 D触发器在计算机系统中有着广泛的应用,主要(多选)为AC。(A.数据缓冲;B.优先编码器;C.组成分频电路;D.译码器;E.实现组合逻辑)

7.28 下列电路中,不属于组合逻辑电路的是D。(A.编码器;B.译码器;C.数据选择器;D.计数器)(www.chuimin.cn)

7.29 同步时序电路和异步时序电路比较,其差异在于B。(A.没有触发器;B.没有统一的时钟脉冲控制;C.没有稳定状态;D.输出只与内部状态有关)

7.30 某移位寄存器的时钟脉冲频率为100kHz,欲将存放在该寄存器中的二进制数码左移8位,完成该操作需要B。(A.10μs;B.80μs;C.100μs;D.800μs)

7.31 一个触发器可记录A位二进制代码。(A.1;B.2;C.4;D.8)

7.32 存储8位二进制信息至少要D个触发器。(A.2;B.3;C.4;D.8;E.28)

7.33 8位移位寄存器,串行输入时,须经D个脉冲后,8位数码全部移入寄存器中。(A.1;B.2;C.4;D.8)

7.34 下列逻辑电路中为时序逻辑电路的是A。(A.数码寄存器;B.数据选择器;C.变量译码器;D.加法器)

7.35 N个触发器最多可寄存B位二进制数码。(A.N-1;B.N;C.N+1;D.2N;E.2N)

7.36 74LS373引脚输出允许端 时,输出端Q为C;74LS377引脚门控端

时,输出端Q为C;74LS377引脚门控端 时,输出端Q为D。(A.高电平;B.低电平;C.高阻态;D.Qn)

时,输出端Q为D。(A.高电平;B.低电平;C.高阻态;D.Qn)

7.37 用二进制异步计数器从0起做加法计数,最少需要B个触发器才能计数到100。(A.6;B.7;C.8;D.10;E.100)

说明:27=128>100

7.38 某数字钟需要一个分频器,将32768Hz的脉冲转换为1Hz的脉冲,欲达此目的,该分频器至少需要B个触发器。(A.10;B.15;C.32;D.32768)

说明:215=32768

7.39 一位8421BCD码计数器至少需要B个触发器。(A.3;B.4;C.5;D.10)

7.40 欲设计0~7计数器,如果设计合理,采用同步二进制计数器,最少应使用B个触发器。(A.2;B.3;C.4;D.8)

7.41 同步计数器和异步计数器比较,同步计数器的显著优点是A。(A.工作速度高;B.触发器利用率高;C.电路简单;D.不受时钟CP控制)

7.42 N个触发器可以构成最大计数长度(进制数)为D的计数器。(A.N;B.2N;C.N2;D.2N)

7.43 把一个五进制计数器与一个四进制计数器串联可得到D进制计数器。(A.4;B.5;C.9;D.20)

7.44 已知74LS161组成的计数器电路,图7-27a的模是C;图7-27b的模是D。(A.10;B.11;C.12;D.13)

7.45 已知74LS161组成的计数器电路,图7-28a的模是C;图7-28b的模是B。(A.10;B.11;C.12;D.13)

7.46 已知74LS161组成的计数器电路,图7-29a的模是C;图7-29b的模是E。(A.10;B.11;C.12;D.13;E.16)

图7-27 习题7.44电路

图7-28 习题7.45电路

图7-29 习题7.46电路

7.47 下列存储器引脚端名称中输入允许为B;输出允许为C;片选允许为A;(A.CE;B.WE;C.OE;D.NC)

7.48 下列条件中,C不是读存储器某一单元的必要条件。(A.挂在数据总线上的其他器件呈“高阻”态;B.存储器片选有效;C.该存储单元中存有数据;D.该存储单元被选通;E.该存储芯片OE端电平有效)

7.49 下列存储器中,用户一次性写入的是B;紫外线擦除可编程的是C;电可擦除可编程的是D;需生产厂商写入的是A。(A.Mask ROM;B.OTPROM;C.UVEPROM;D.E2PROM)

7.50 下列存储器中,可多次擦写(多选)的有CDE。(A.Mask ROM;B.OTP-ROM;C.UVEPROM;D.E2PROM;E.Flash Memories)

7.51 下列存储器中,存储内容需不断刷新的是B。(A.SRAM;B.DRAM;C.MROM;D.PROM)

7.52 下列存储器中(多选),能随机读写的是AB;断电后,信息不丢失的有CD。(A.SRAM;B.DRAM;C.MROM;D.PROM)

7.53 读存储器某一单元时(多选),破坏存储单元内容的是B;复制存储单元内容的是ACD。(A.SRAM;B.DRAM;C.MROM;D.PROM)

有关计算机电路基础学习指导与习题解答的文章

A.尽量绕道躲避B.立即报警,停车观望C.协助保护现场,并立即报警D.加速通过,不予理睬解析:题中,A、D明显错误,先排除掉,B停车观望与题意也背道而驰,唯有答案C为给予“帮助”,符合题意。印象认定法要求考生对某知识点由印象的深刻程度来选择答案。......

2023-10-06

数据寄存器用于存储数值型数据。若两个相邻的数据寄存器组合,可存储32位的数值型数据。数据寄存器可分为如下几类。①通用型数据寄存器,共200点。通用型数据寄存器一旦写入数据,只要不再写入其他数据,其内容不变。只要不改写,无论PLC是从运行到停止,还是断电时,断电保持型数据寄存器里的数值将保持不变。特殊数据寄存器供监控机内元件的运行方式用。④文件数据存储器。......

2023-06-20

法律效力存在差异:鉴定意见和检验报告都可以作为证据使用,但法律效力存在差异,按照司法解释的规定,鉴定意见可以作为定案的依据,检验报告可以作为定罪量刑的参考。(二)常见鉴定类型1.人身鉴定2.价格鉴定3.毒品鉴定4.精神疾病司法鉴定5.文检鉴定6.痕迹鉴定7.司法会计鉴定8.声像资料司法鉴定9.电子数据鉴定10.物品性质鉴定11.微量物证鉴定、毒物法医鉴定......

2023-08-10

在医学行业,使用3D打印技术打印牙齿和其他骨骼模型,以及制药,解决了药品发潮变质、过期等问题。在航天科技领域,可以使用3D打印技术制造高难度零件,同时可以降低生产成本。在汽车和建筑行业,借助3D打印技术可以解决不可再生资源问题。在历史文物领域,使用3D打印技术可以复原珍贵文物,尤其是易碎文物等。3D打印技术已在多家博物馆用于复制文物和公益活动。......

2023-08-13

Unity是一个非常流行和强大的游戏引擎,它支持众多的平台和设备。图7-75Game视图效果注意:对于Unity 2D游戏,Unity编辑器会自动处于2D模式。图7-77将playership精灵图片拖入场景视图在结构视图中,单击Unity为你创建的playership游戏对象,在检视器中查看它的属性。通过Unity的2D精灵表单编辑器,能够轻易管理这些精灵表单。......

2023-10-17

相关推荐