1芯片片内内存使用TI芯片相关的内存管理,对片外内存来说,可以通过启动参数将需要内核管理的内存进行设置。这样做的原因是由于需要连续的物理内存空间,并且对内核的物理内存管理影响最小。3独立cmem管理之前简单说明芯片厂商的独立内存管理,针对于TI的视频芯片,TI提供了cmem的内存管理驱动,主要是连续内存管理。有了该内存管理功能,TI的多媒体框架和编解码库就可以使用连续的物理内存空间,高效地完成多媒体处理相关的功能。......

2025-09-30

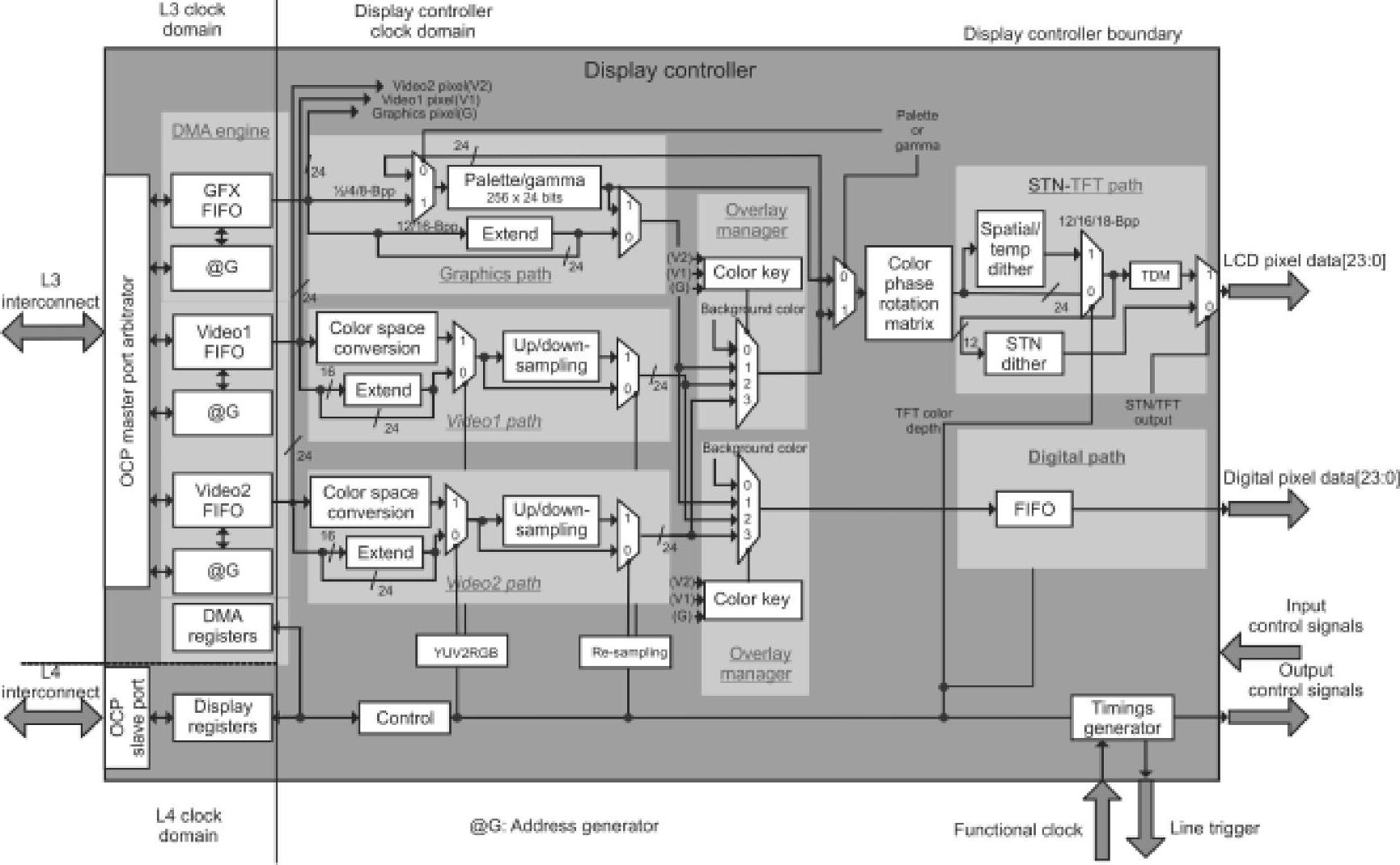

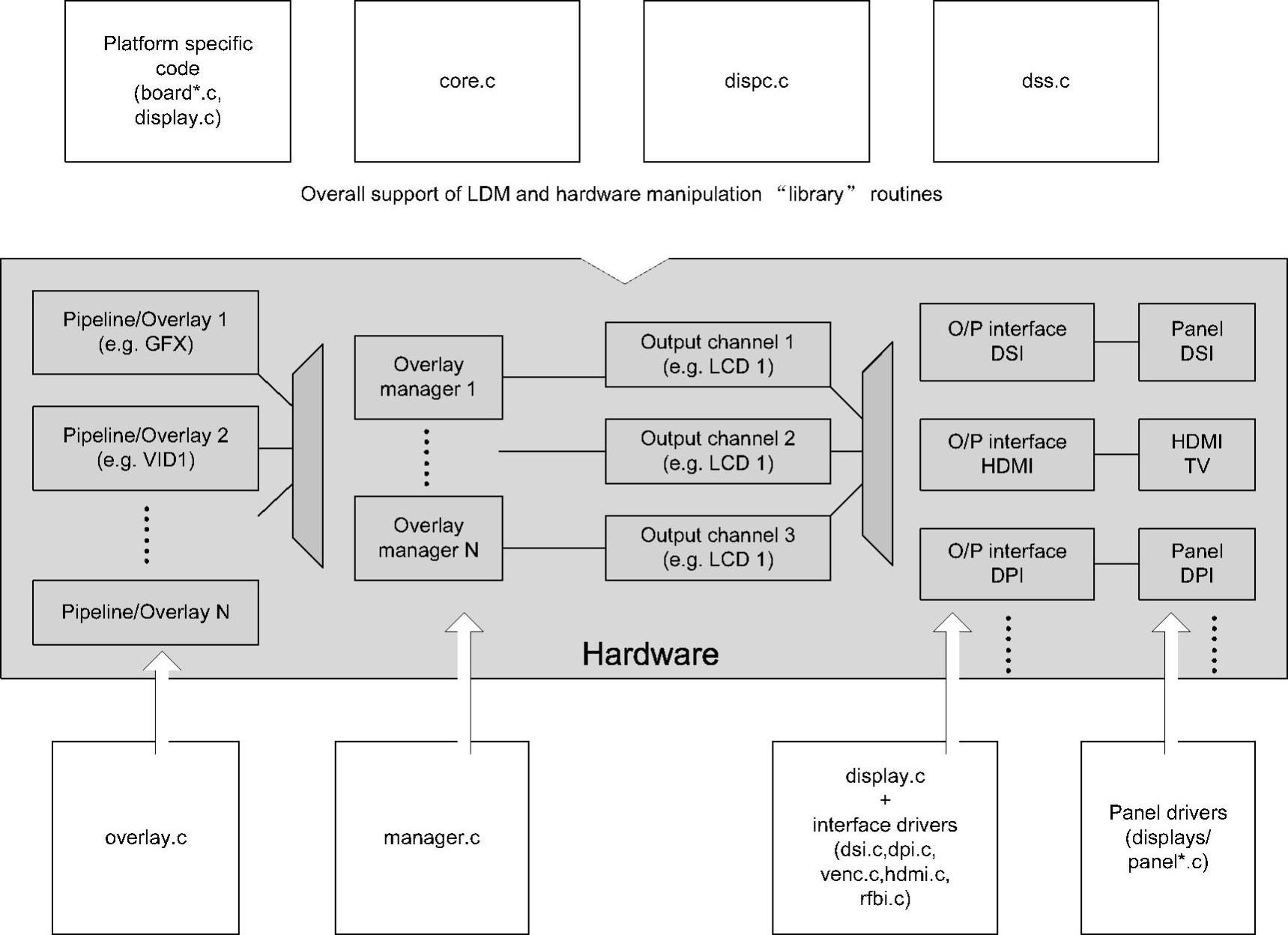

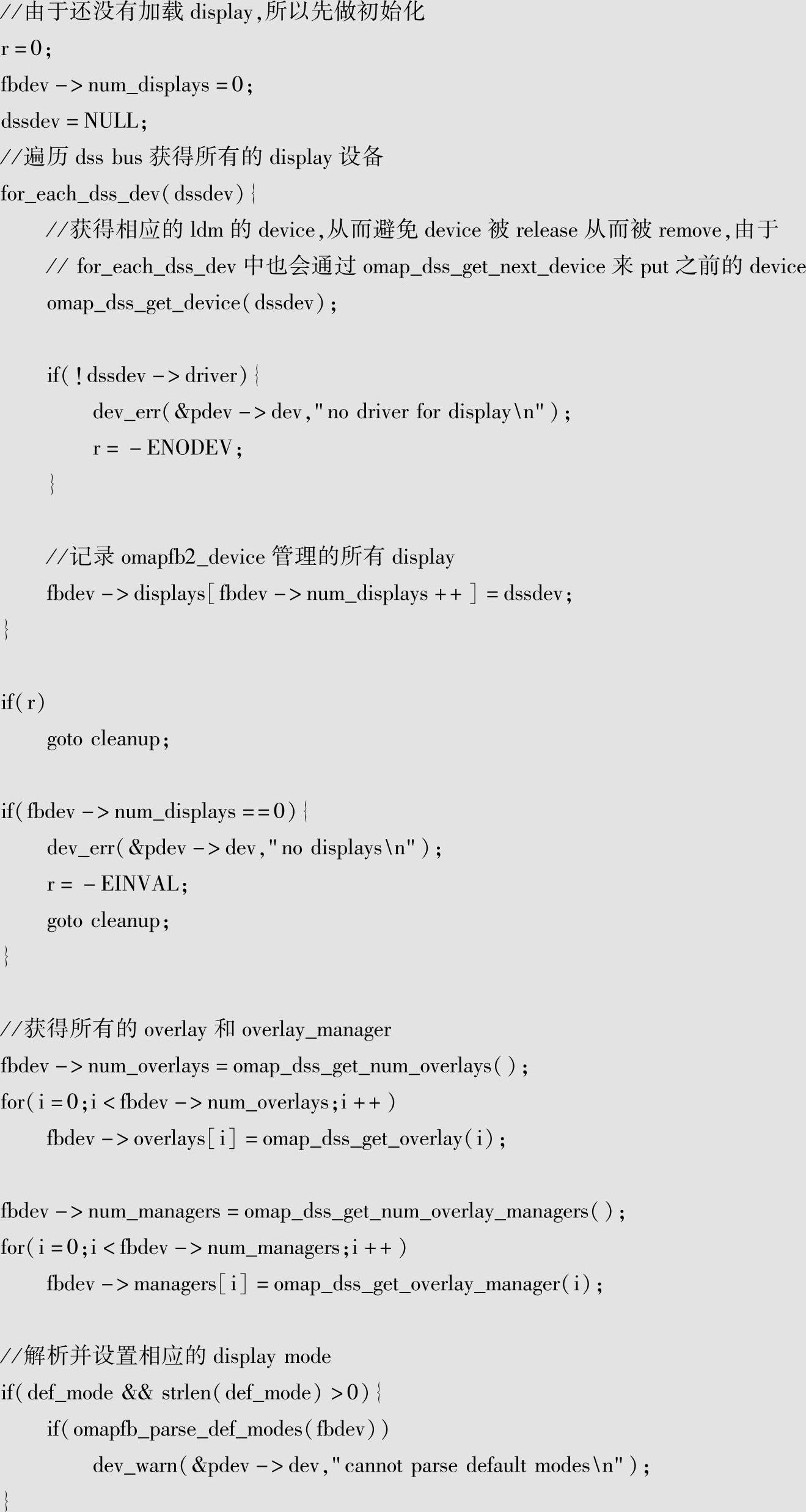

TI DM3730的frame buffer驱动针对的硬件设备是display controller,硬件框图如图6-9所示。图6-9引自《DM3730芯片手册》中第1624页框图。

图6-9 DM3730 display控制器硬件框图

从图6-9可见,DM3730支持3个不同的显示通道,而且所有的通道都通过DMA自动获得显示信息进行显示,不同的通道可以以一定顺序进行叠加,在显示硬件上也可以有两个显示设备,硬件提供了在不同的显示通道以及硬件显示设备切换的能力。

1ᤫ整体框架

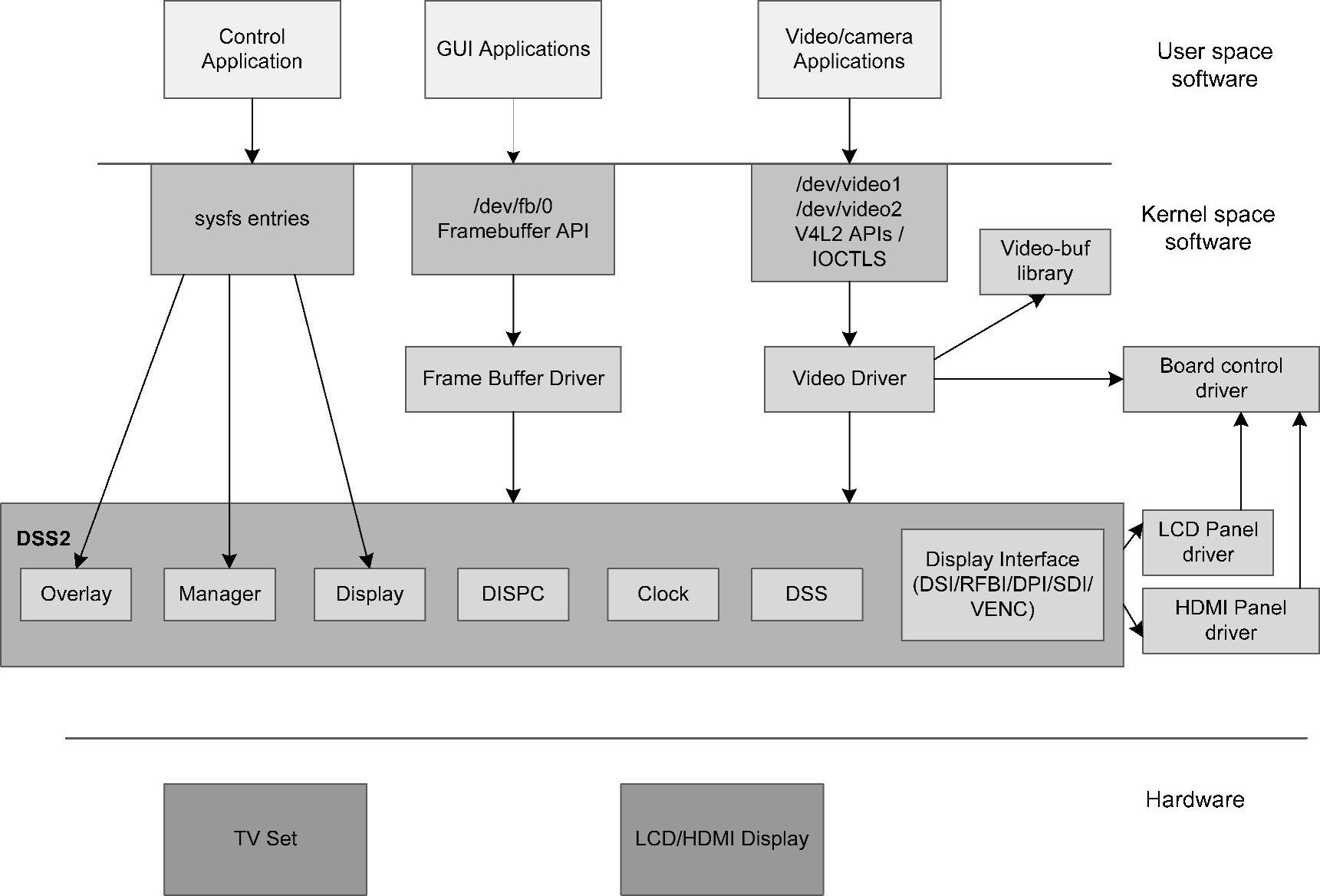

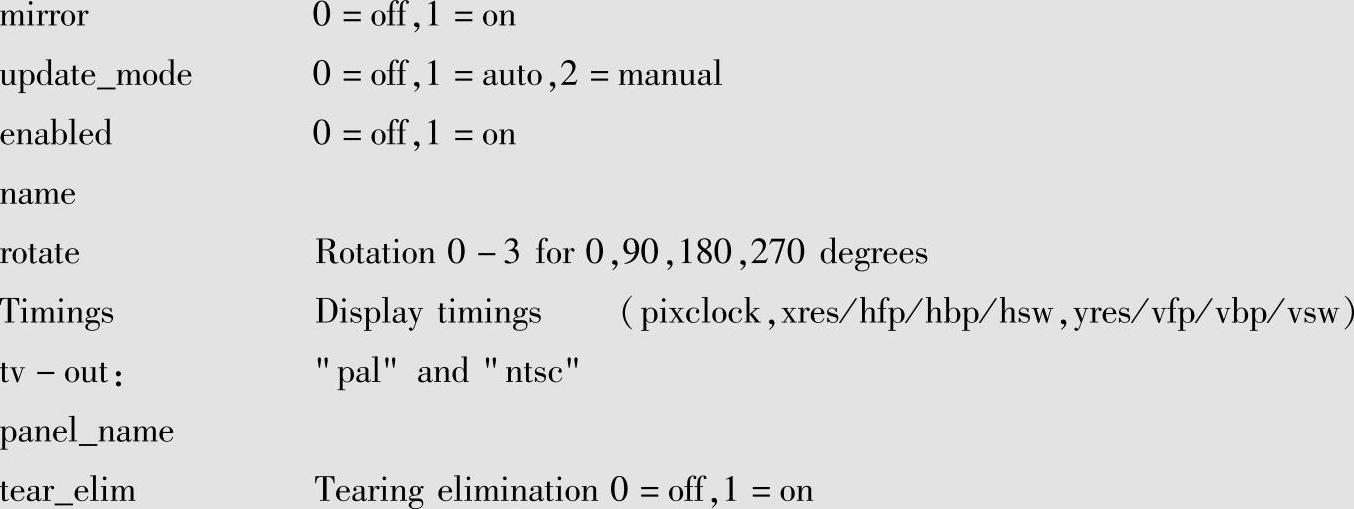

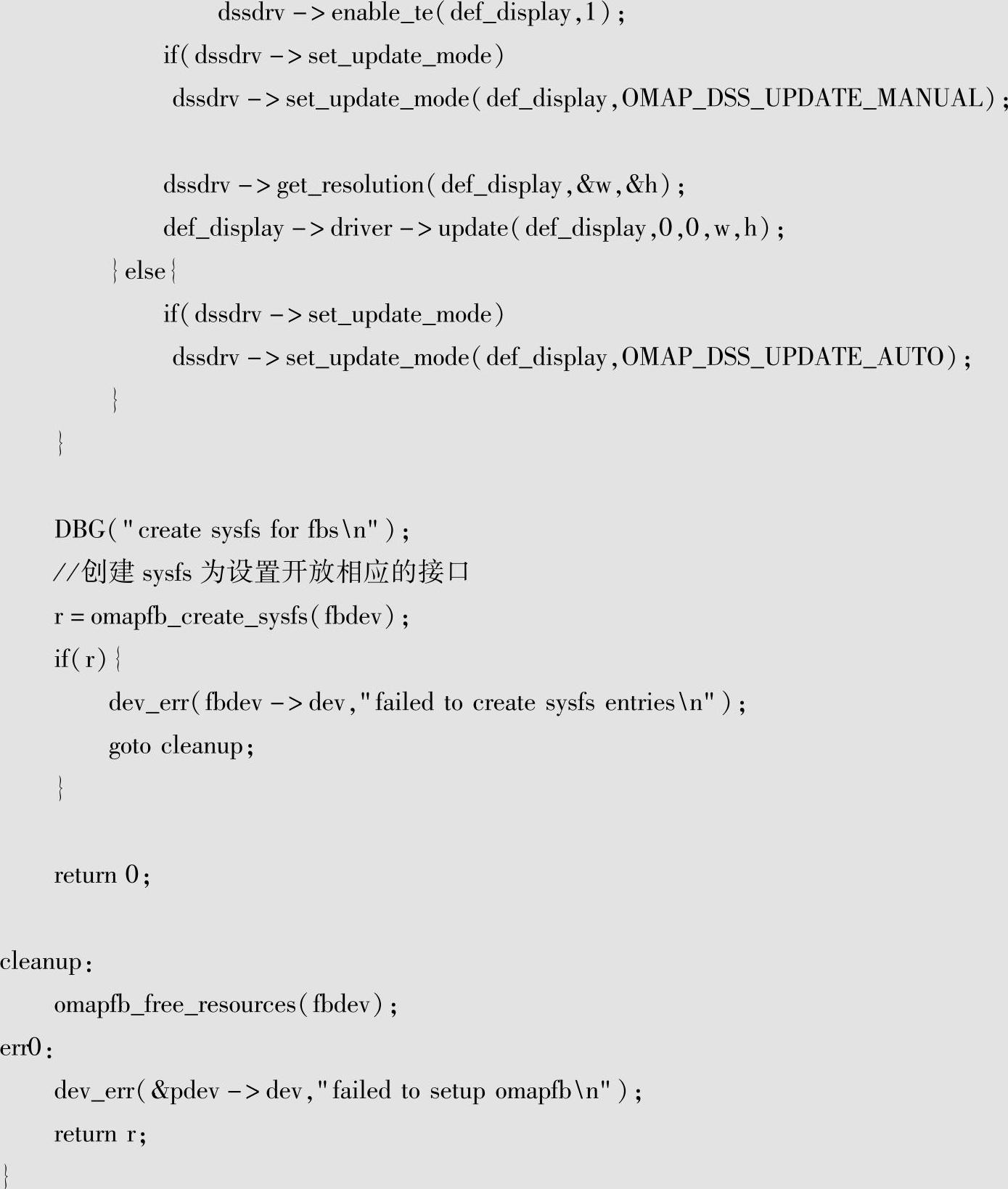

为了支持硬件的各种功能,在相应的驱动设计过程中TI设计了DSS(display subsystem)架构支持该功能。整体的架构如图6-10所示。

图6-10 DM3730显示子系统软件整体架构

从图6-10可见,在驱动框架部分,DSS的设计支持frame buffer和V4L2两种架构,这是由于两种类型的设备都是通过硬件的display子系统进行显示,它们之间可以通过叠加子系统进行叠加,这样相当于在硬件层进行了硬件加速,可以实现良好的显示效果。

在系统设计中还开放了sys文件系统接口,可以方便地进行切换和设置,来满足各种动态的需求。

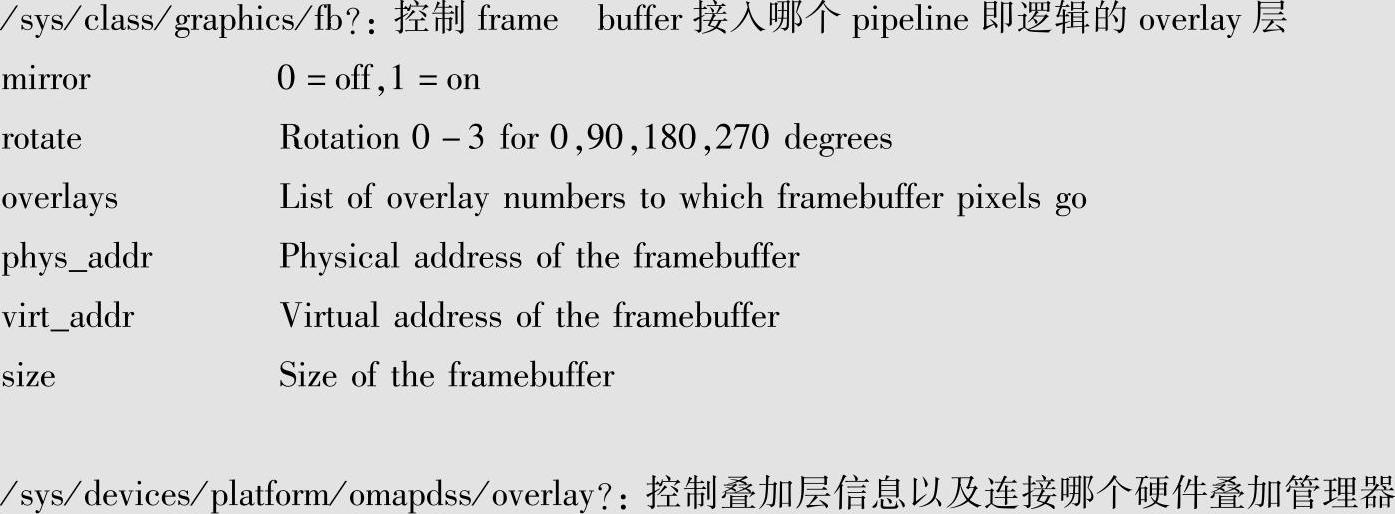

DSS系统中各个模块与硬件的对应关系如图6-11所示。

从图6-11可见,不同的pipeline是由overlay进行管理来表示不同的overlay层,而man-ager则是管理硬件的叠加控制以及之后的显示通路,会对应到显示接口,display部分是对显示接口的控制,panel则是对应真实的显示设备。

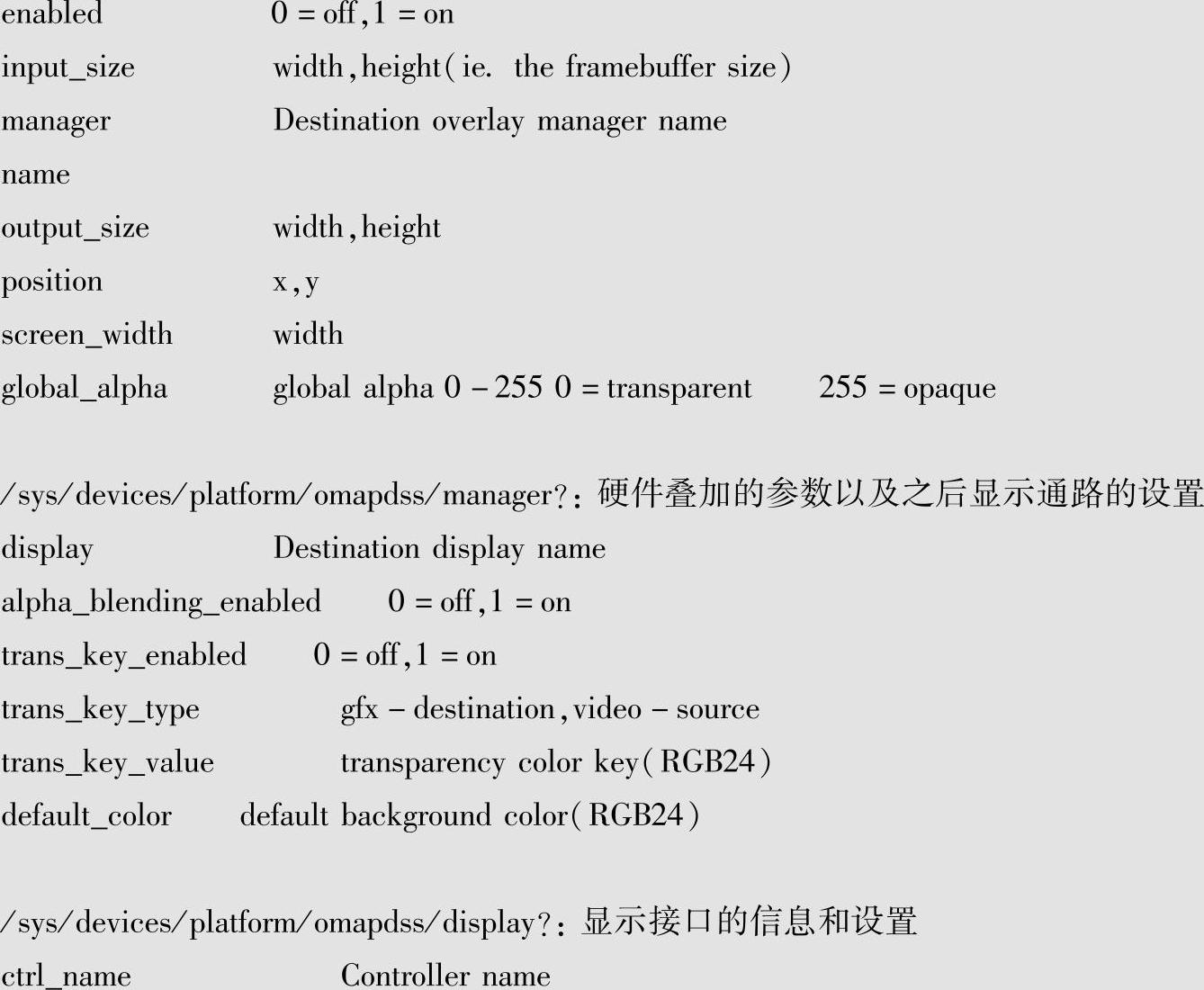

开放的sys接口如下:

图6-11 DSS软件模块与硬件对应关系图

通过以上的设置就可以实现显示的切换、叠加等复杂的功能。

2ᤫFrame Buffer驱动

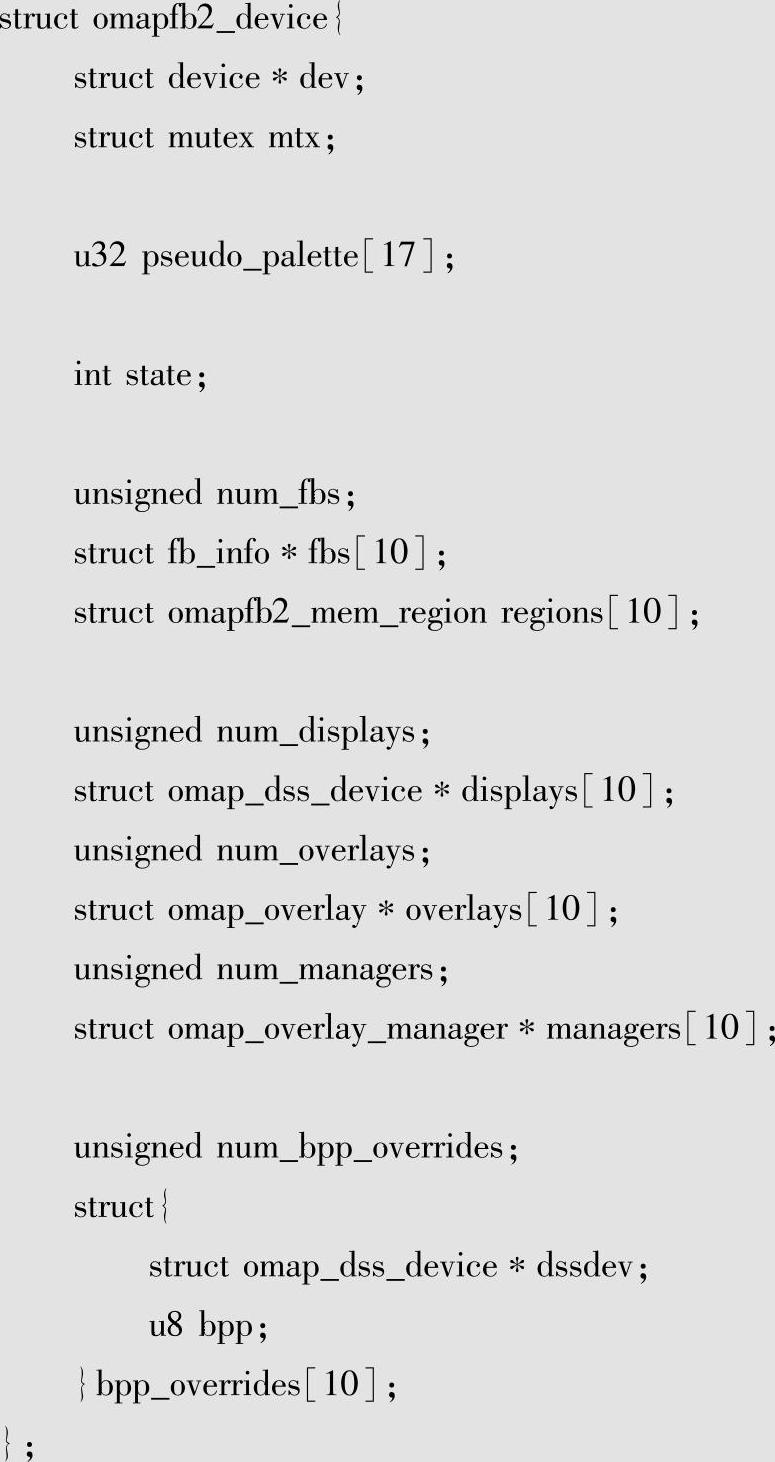

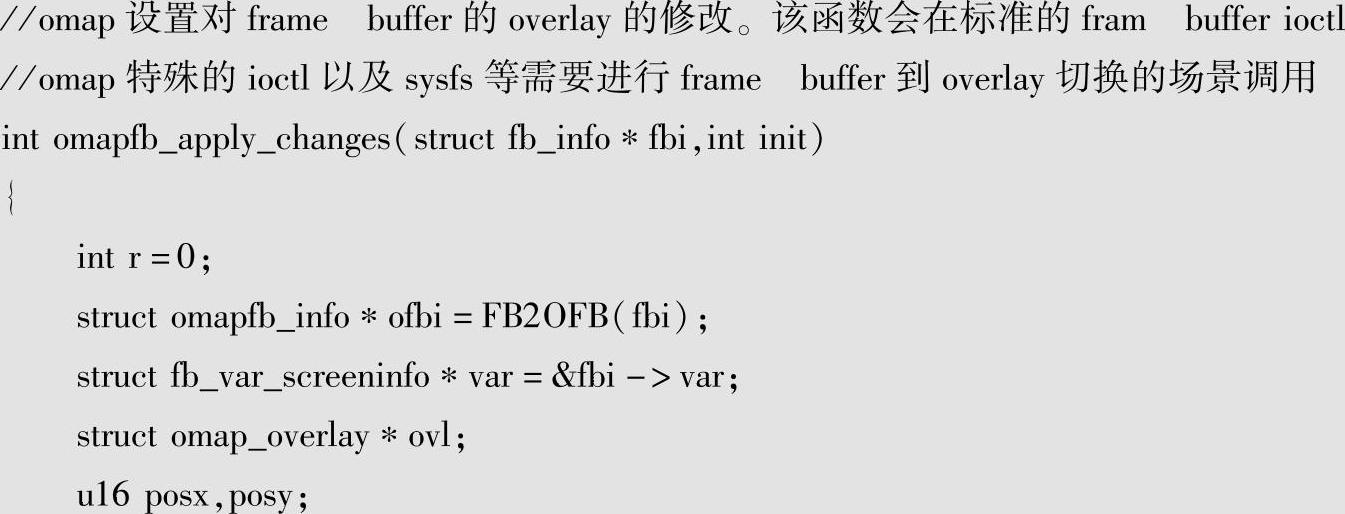

接下来看看framebuffer驱动是如何实现的。TI frame buffer驱动的核心管理实体是omapfb2_device。

从内容看其管理了上层fb_info以及内部的overlay、manager还有display,实际它就是display subsystem的逻辑实体。

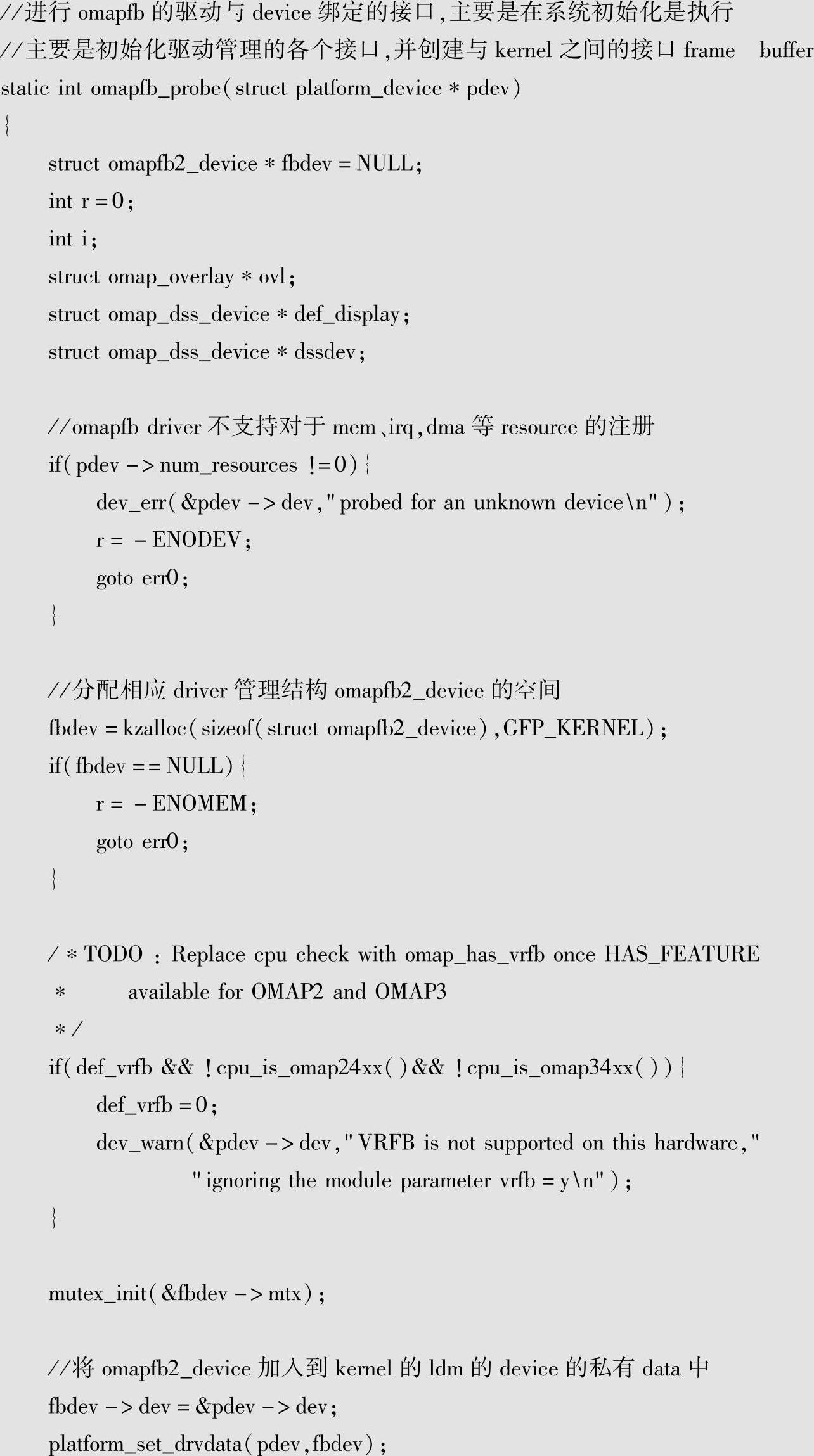

相关的初始化是在platform驱动的probe中进行的,具体分析如下:

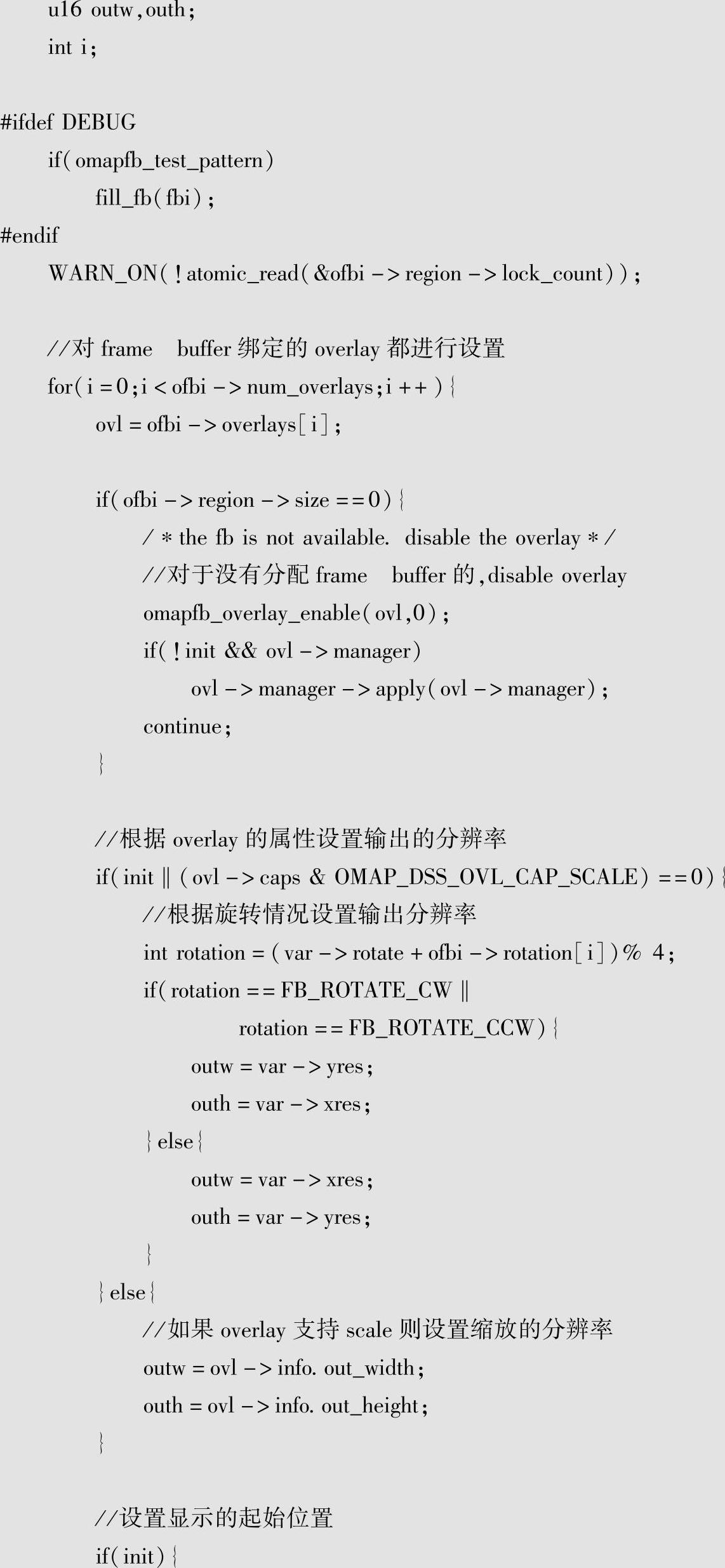

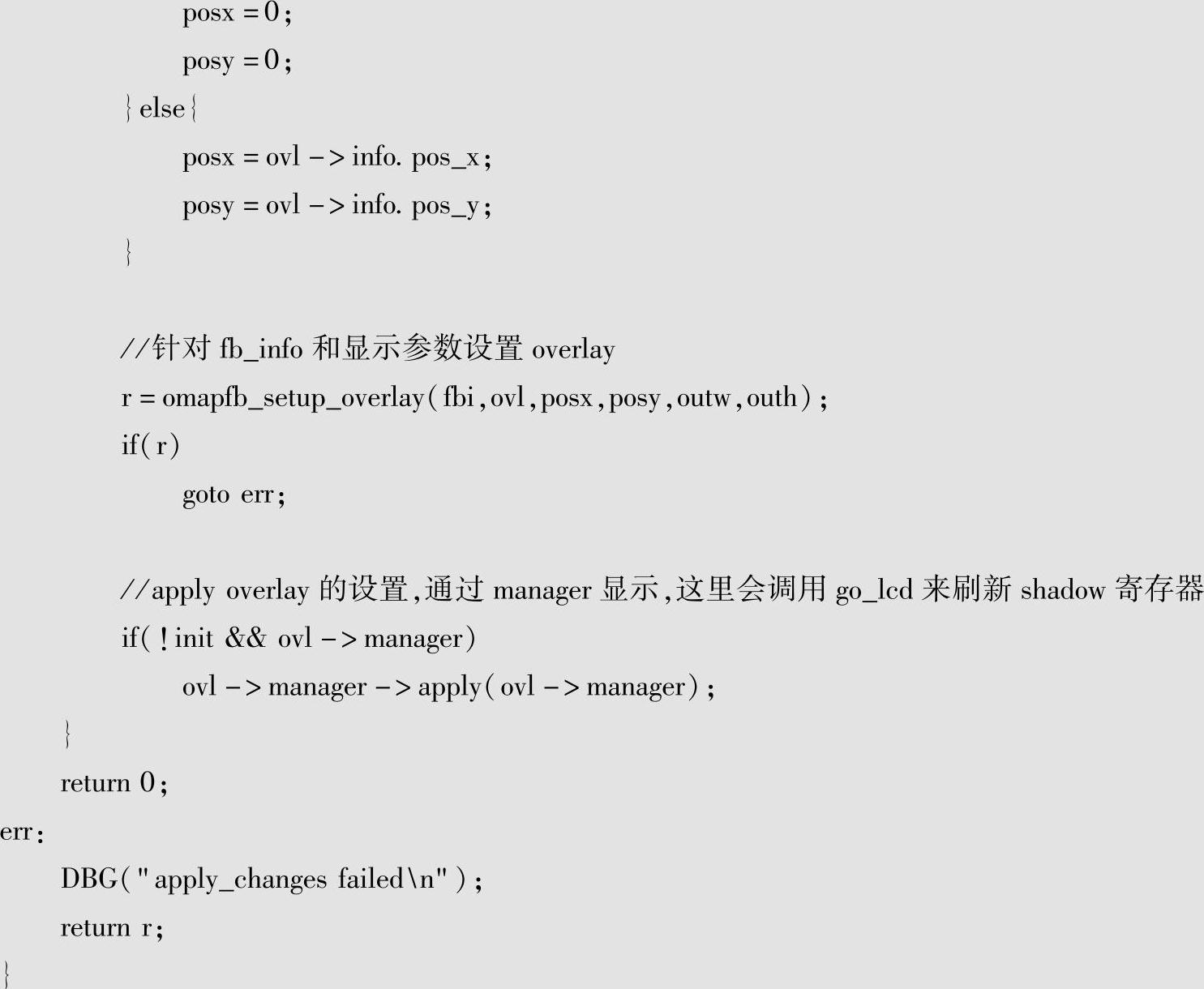

通过以上初始化后,就可以通过sys文件系统对相关属性进行设置了。另外frame buffer的可变参数也是可以修改的(如FBIOPAN_DISPLAY命令)。驱动应对这种修改通过mapfb_apply_changes来实现。具体分析如下:(https://www.chuimin.cn)

frame buffer的驱动还有重要的内容就是对显示存储空间的分配和映射,下面进行相关的分析。

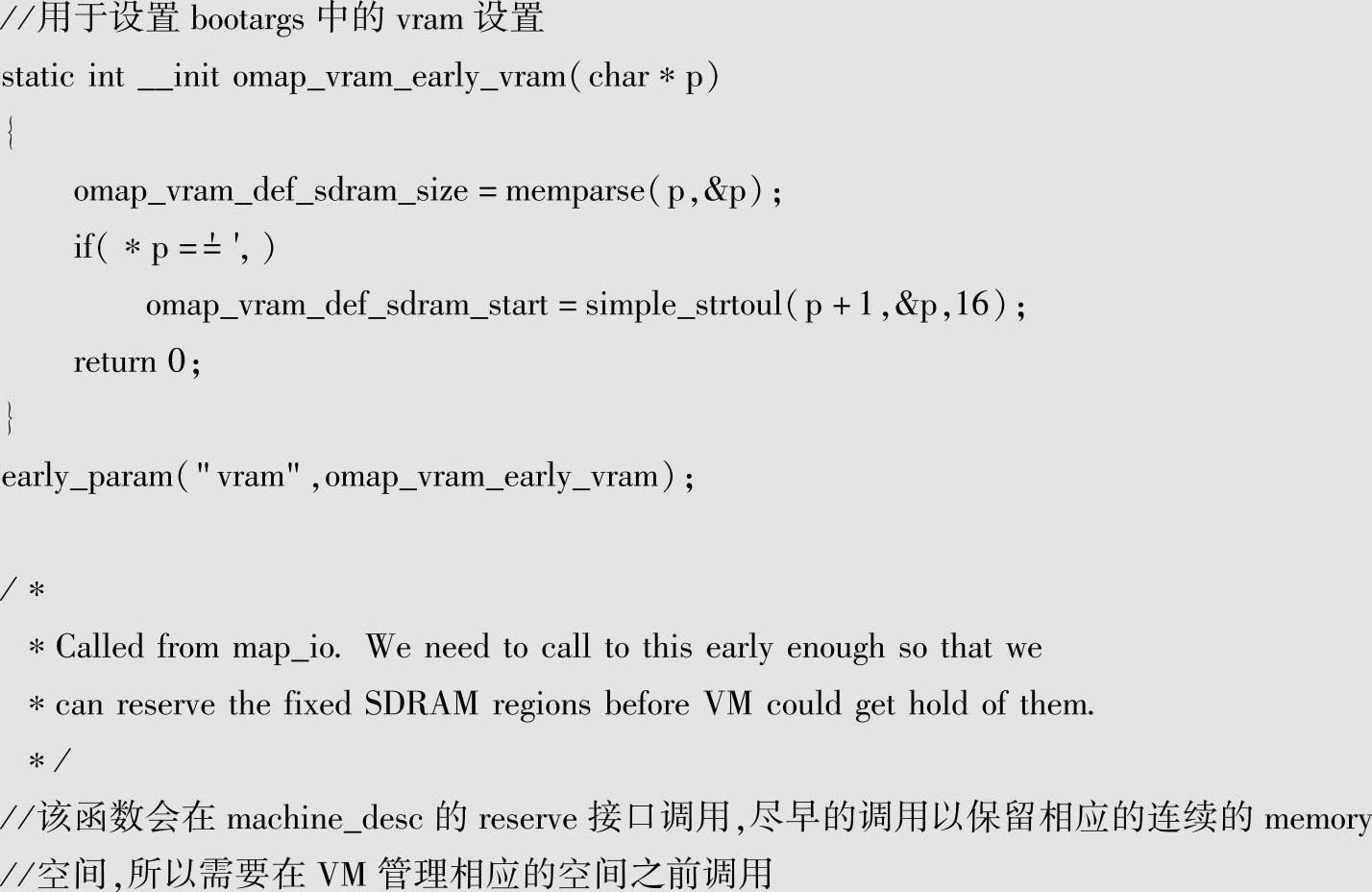

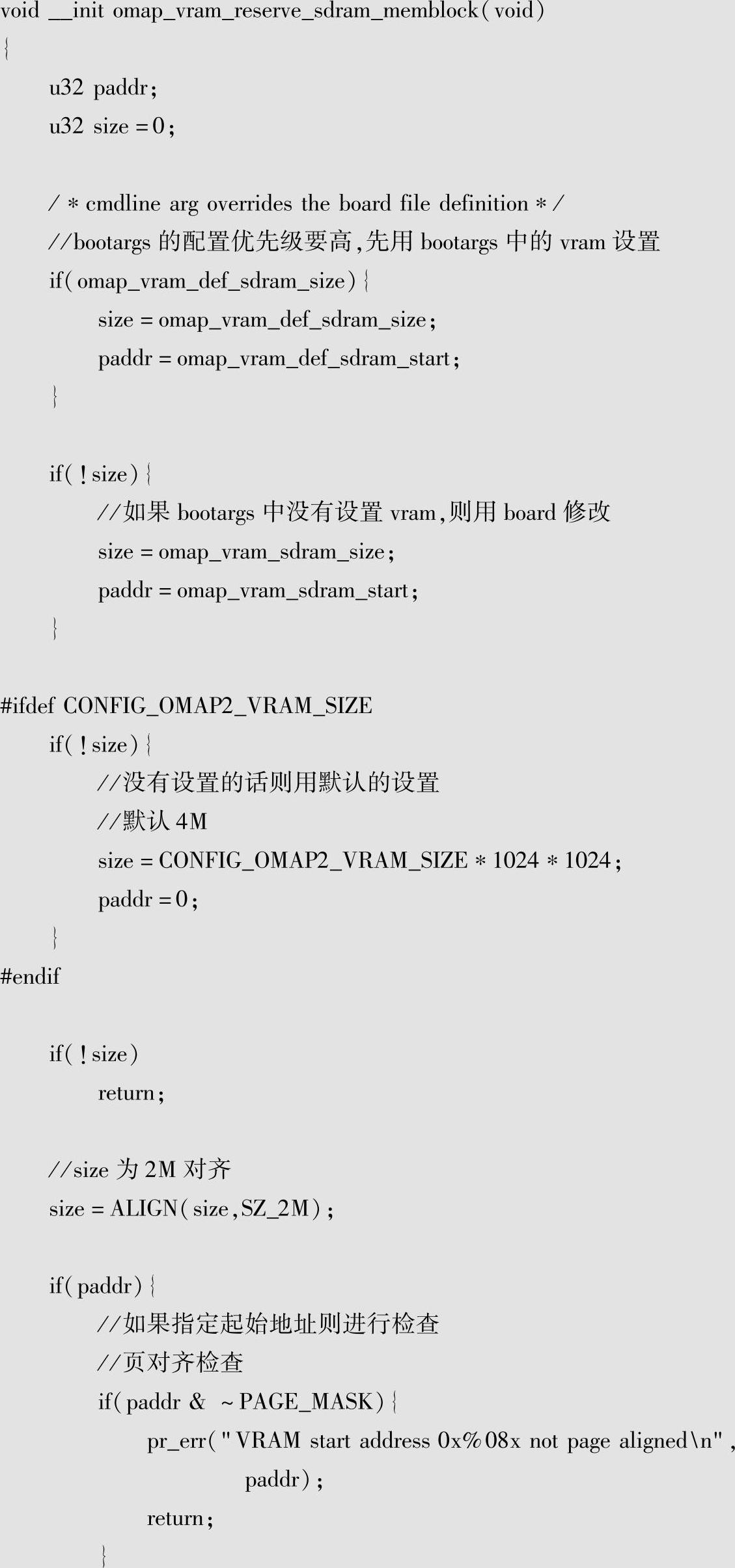

显示存储空间的分配系统会在初始化的时候通过启动参数预留,相关代码分析如下:

显存的空间通过vram统一管理,这部分空间不在内核的管理范围内,相应的分配也是由vram的分配函数omap_vram_alloc来进行,具体的分配工作则是在驱动probe中通过omapfb_create_frame buffers来执行的。

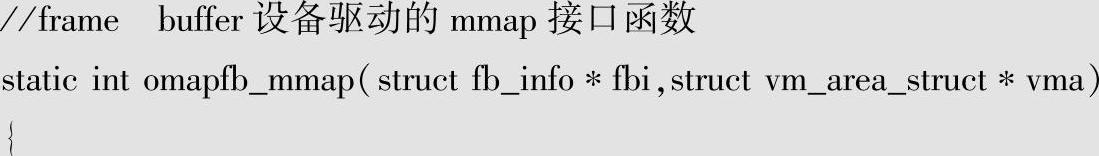

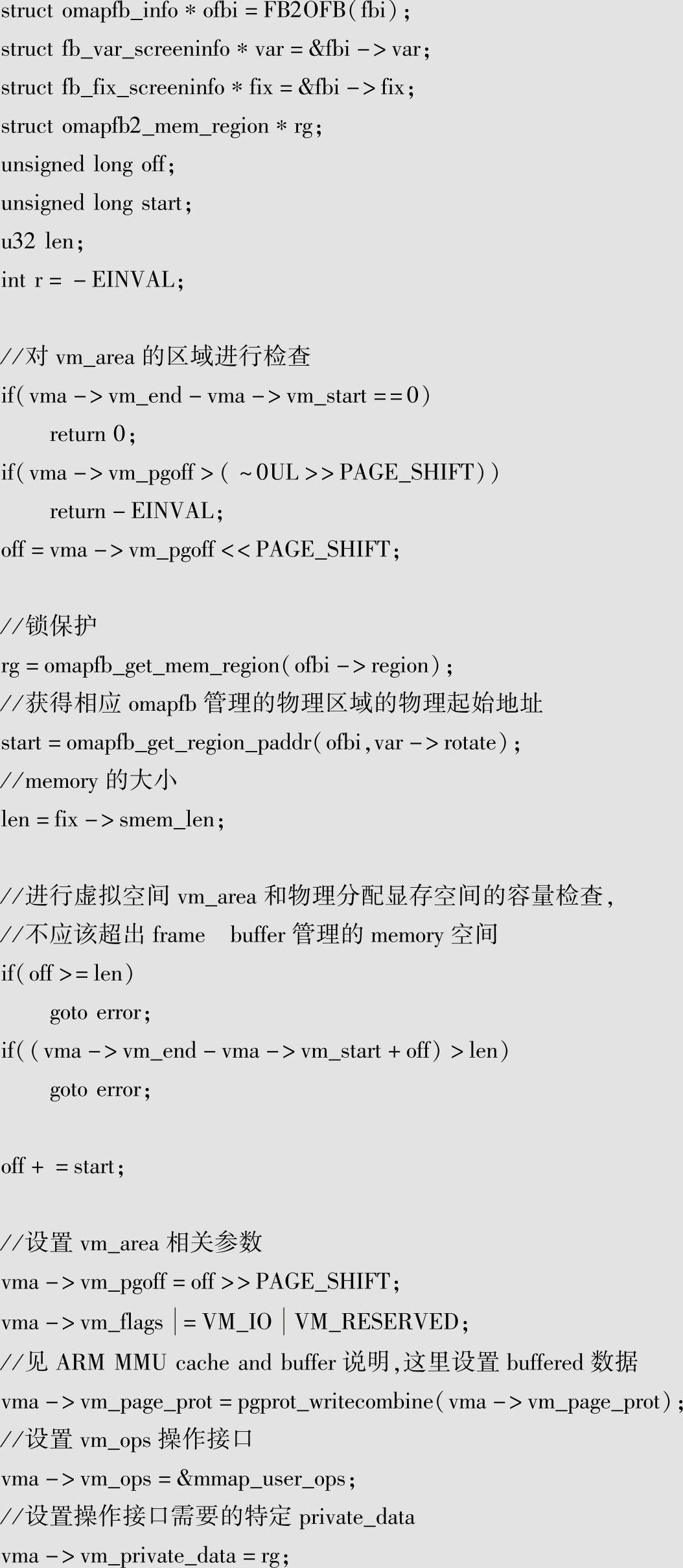

驱动也提供了相应的映射接口omapfb_mmap,分析如下:

从分析中可见,设置了虚拟地址区域的操作接口mmap_user_ops,由于相应的映射是通过io_remap_pfn_range的整体映射,并不需要进行缺页异常的操作,所以mmap_user_ops只提供了open和release的接口用于引用计数的操作。

用户对frame buffer的操作基本都通过以上的功能完成。

3ᤫ显示设备的管理

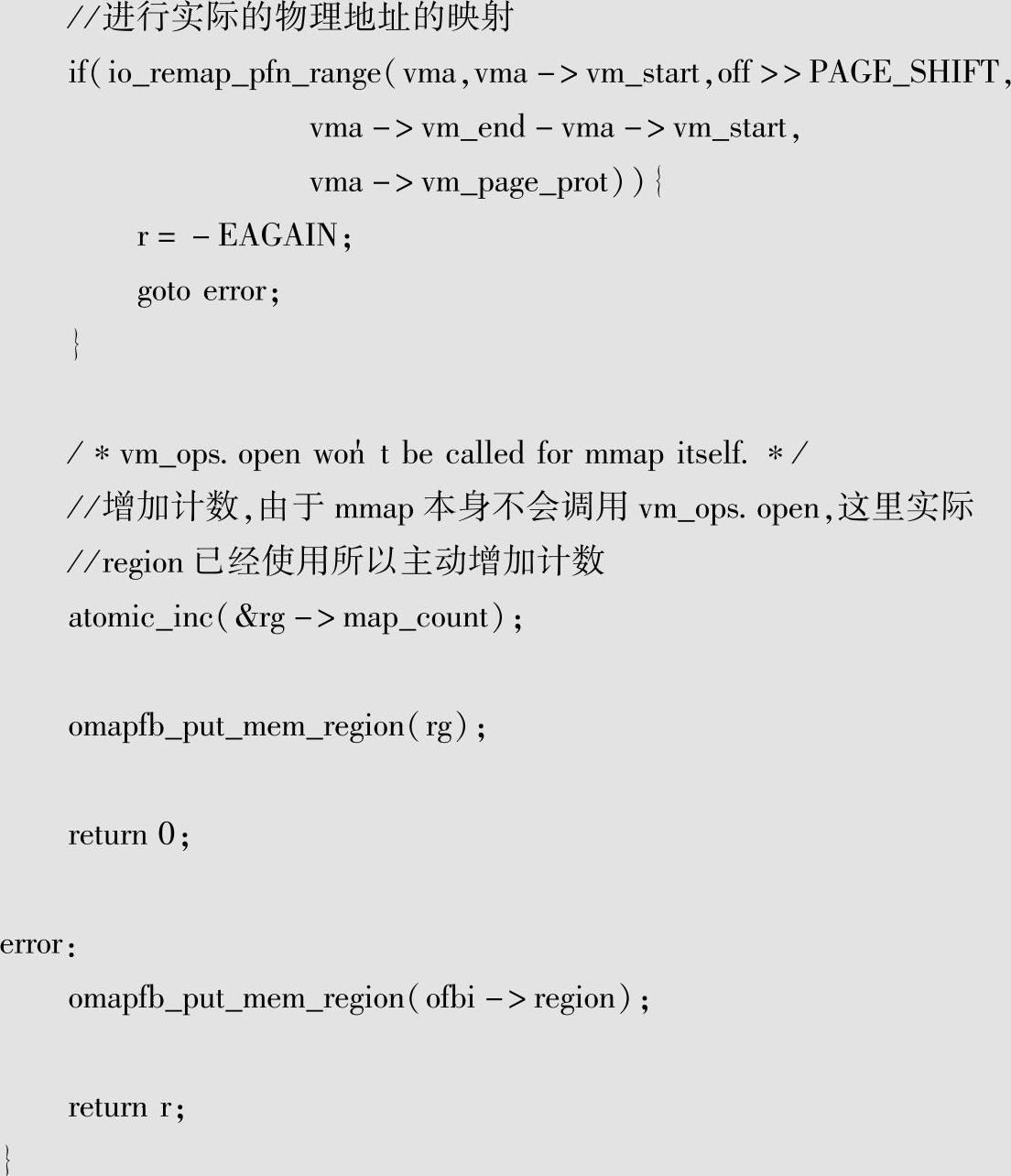

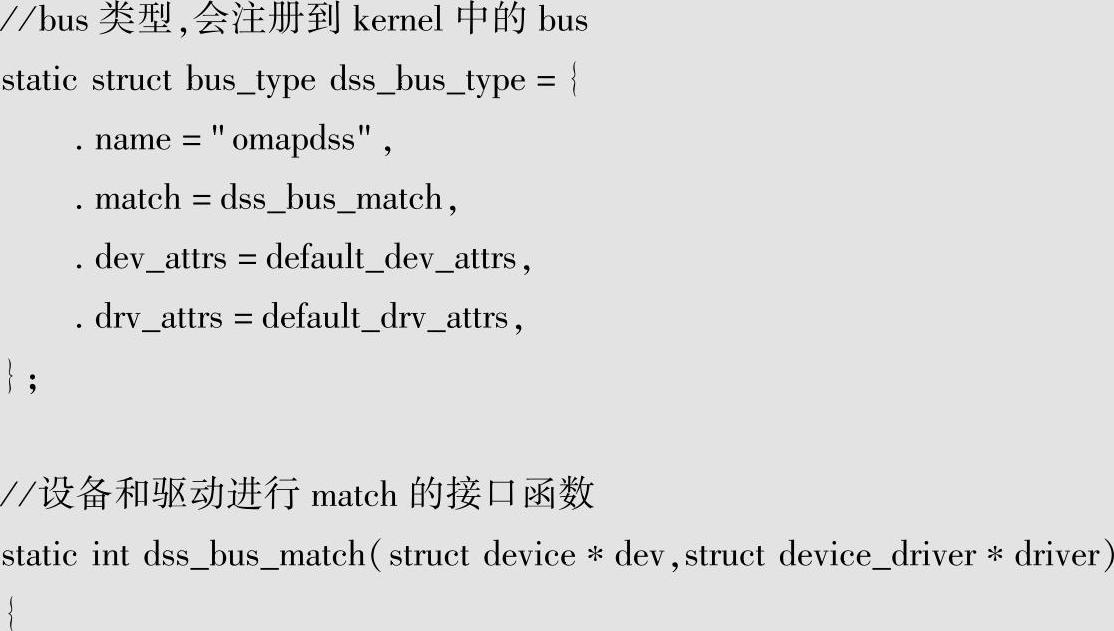

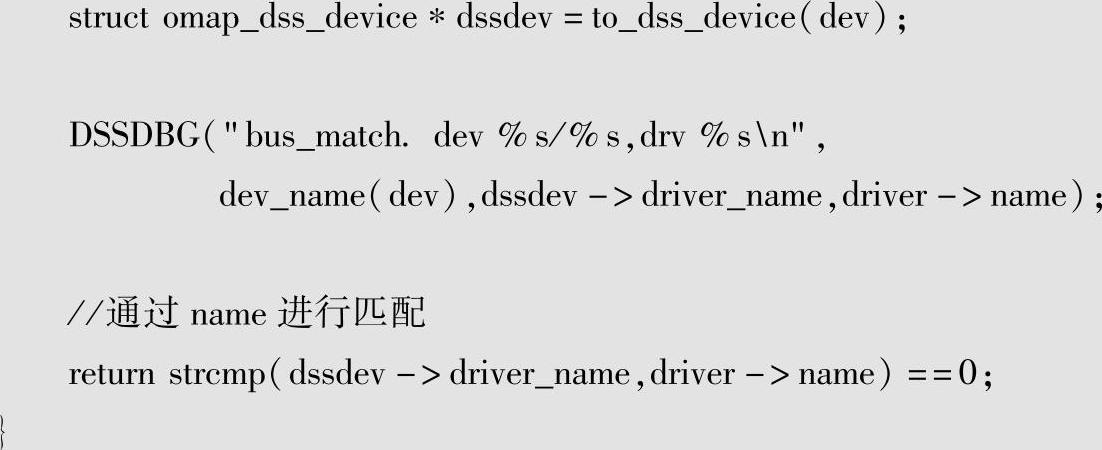

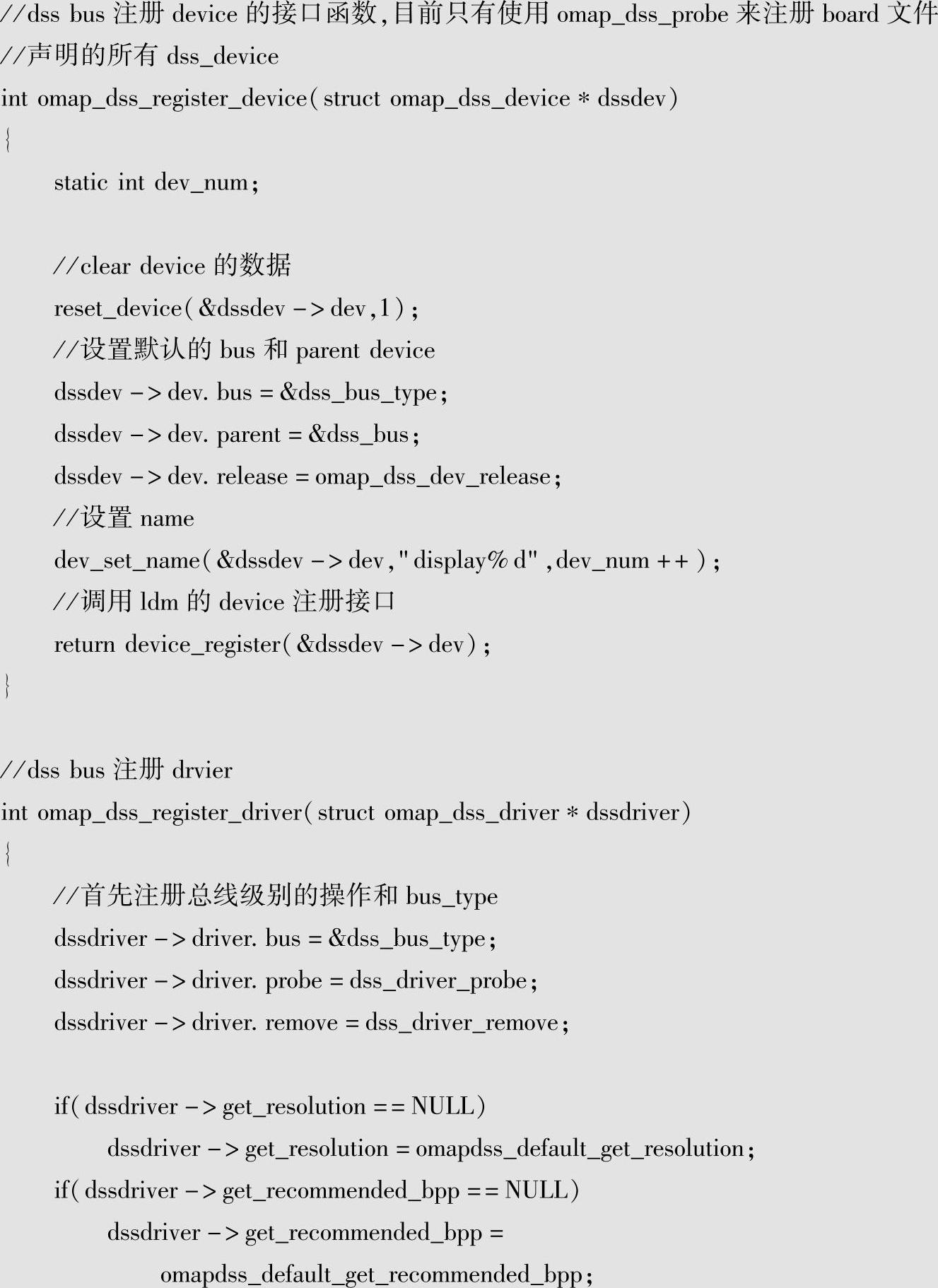

从DSS硬件可见,其可以支持多个显示设备,这有些类似于总线,为了能够同时支持多个显示设备,驱动设计并实现了一种逻辑总线———dss_bus。相关分析如下:

另外在设备与驱动绑定需要相应的注册接口,具体的分析如下:

可见dssbus管理的实体就是设备omap_dss_device和驱动omap_dss_driver,在omap_dss_device中主要是显示设备的硬件信号信息,而omap_dss_driver则是操作接口(包括功能和电源管理操作)。

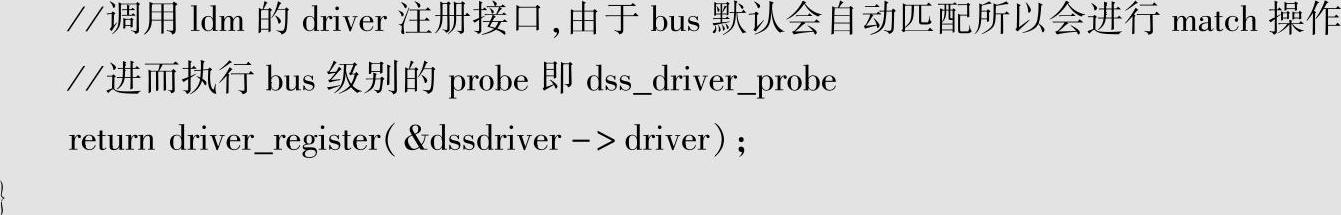

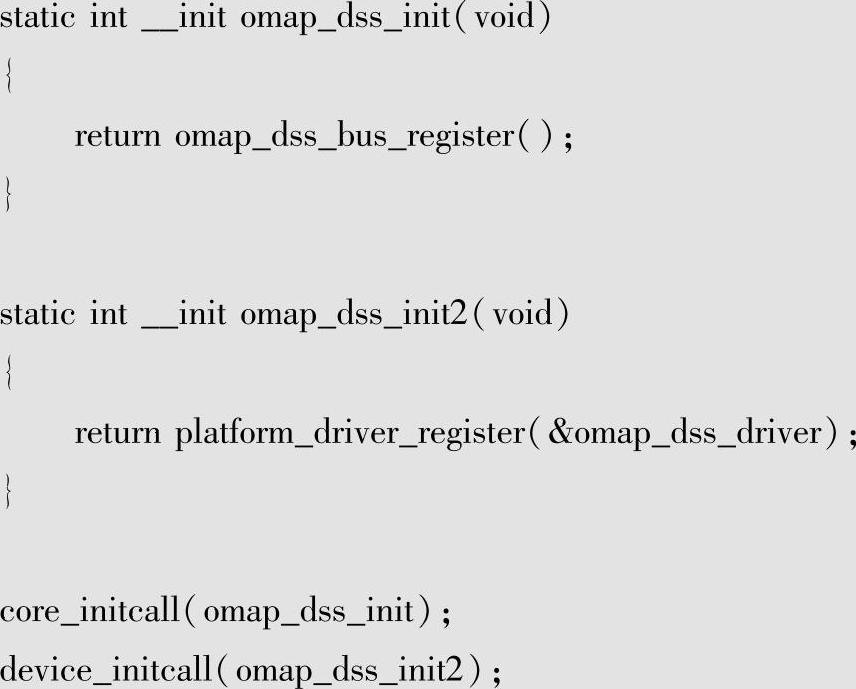

如果整个dss编进内核的话,相应的初始化如下:

可见bus的初始化要早于相应的驱动,这样就在dss驱动初始化probe的过程中将所有的显示设备信息注册,而驱动注册的时候就可以将二者绑定。

这样就完成了多种显示设备的管理,从而可以实现各种复杂的功能。

相关文章

1芯片片内内存使用TI芯片相关的内存管理,对片外内存来说,可以通过启动参数将需要内核管理的内存进行设置。这样做的原因是由于需要连续的物理内存空间,并且对内核的物理内存管理影响最小。3独立cmem管理之前简单说明芯片厂商的独立内存管理,针对于TI的视频芯片,TI提供了cmem的内存管理驱动,主要是连续内存管理。有了该内存管理功能,TI的多媒体框架和编解码库就可以使用连续的物理内存空间,高效地完成多媒体处理相关的功能。......

2025-09-30

图4-24DM 3730物理空间设置IO空间映射的目的就是将这些物理地址映射到整个内核的地址空间中。首先来看ioremap虚拟地址返回是如何实现的。DM 3730等TI芯片就是通过该方法来实现该功能的。注意__arm_ioremap_caller使用的是vmalloc的空间进行映射,在相应版本内核中vmalloc的空间和TI芯片的IO映射空间是完全分开的,所以这里要直接返回相应的虚拟地址。......

2025-09-30

图1-3引自TI的《DM 3730芯片手册》中第136页框图,为了方便读者在芯片手册中查找相关的内容,会在引用芯片手册框图时说明其所在的页码。各种不同类型的数据连接接口其设计思想以及功能是不同的,例如I2C通常用于设备的控制,McBSP用于音频数据的传输等。图1-3基于DM 3730的设备框图为什么要有这么多连接方式呢?......

2025-09-30

设备模型中管理驱动的数据结构是device_driver,其中包含驱动提供的通用服务的接口,下面对它进行分析:来看看sys文件系统中驱动之下主要管理哪些实体:从driver_private可见,其中主要的信息是运行中使用该驱动的设备列表。以platform驱动实体为例进行分析:其中定义了总线设备相关的服务接口:从platform驱动注册接口可以看出,抽象层的服务接口都被换为实例化的接口,这样内嵌的driver可以通过设备模型核心提供的标准操作进行管理,也可以通过这些实例化接口进行转换。......

2025-09-30

图3-3Linux内核整体框架③bridges:桥梁层。Linux内核通过统一的接口操作设备,这样就屏蔽了各个设备的差异,从而降低了和硬件的耦合关系。Linux内核为了简化实现,将共享资源的进程作为线程。考虑到外部事件需要对执行流程进行转换,另外不同的应用执行流程之间需要切换,这就要在Linux内核的逻辑层抽象出调度器这一逻辑功能。......

2025-09-30

Linux内核中的内存管理框架考虑到了各个方面的需求,实现得非常精细。1内核对于内存的管理和使用的整体框架Linux内核的内存管理也要满足内核自身的需要。图4-32展示了Linux内核的内存管理框架。仅有好的页分配器是不能满足内核对于内存管理的需要的,前面已经介绍了,内核有很多频繁使用的数据结构,对于它们最好单独分配空间进行管理,这就形成了SLAB分配器。......

2025-09-30

谈到Linux内核,大家的第一感觉就是一个庞大的系统、很多的模块和功能,实在是太复杂了。Linux内核在设计过程中这些都已考虑在其中,这也就提升了它的适用范围。抽象是人类的一个重要思维能力,从某种角度来说软件系统是对各种概念或者行为进行抽象,并加以管理。......

2025-09-30

整个系统启动和初始化的过程,Linux内核是在主处理器启动之后才会执行。不同的处理器启动流程并不相同,这就要求Linux内核能支持各种处理器的初始化操作。Linux内核各个模块,大部分设计时做到了体系结构无关。Linux内核是一个庞大的系统,最终生成的操作系统代码的执行文件非常大。......

2025-09-30

相关推荐