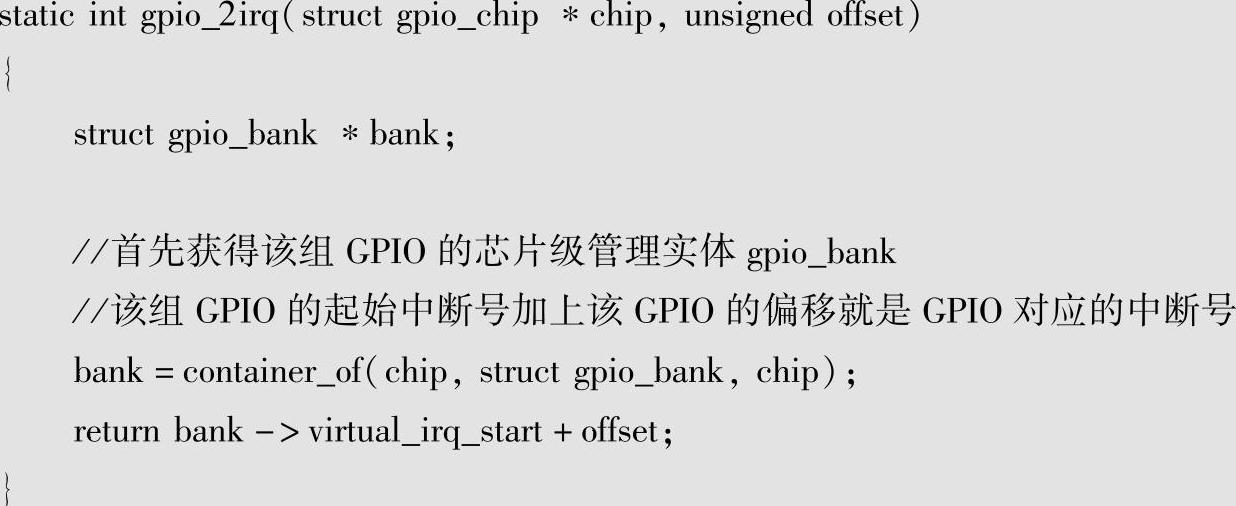

【摘要】:TI芯片GPIO管理的具体实现仍是以DM 3730为例,关于GPIO模块本身,DM81XX等处理器与DM 3730是相同的,只是一些寄存器地址和参数不同。图4-50DM 3730GPIO子系统框图从图4-50可见,DM 3730一共有6组GPIO管理单元,每组管理32个GPIO。1重要的初始化实现对于GPIO功能芯片特殊的实现和GPIO lib的接口就是gpio_chip。3GPIO中断相关实现GPIO中断相关的实现,最主要的是中断控制器相关的接口实现以及中断级联中GPIO组的中断处理函数。

TI芯片GPIO管理的具体实现仍是以DM 3730为例,关于GPIO模块本身,DM81XX等处理器与DM 3730是相同的,只是一些寄存器地址和参数不同。

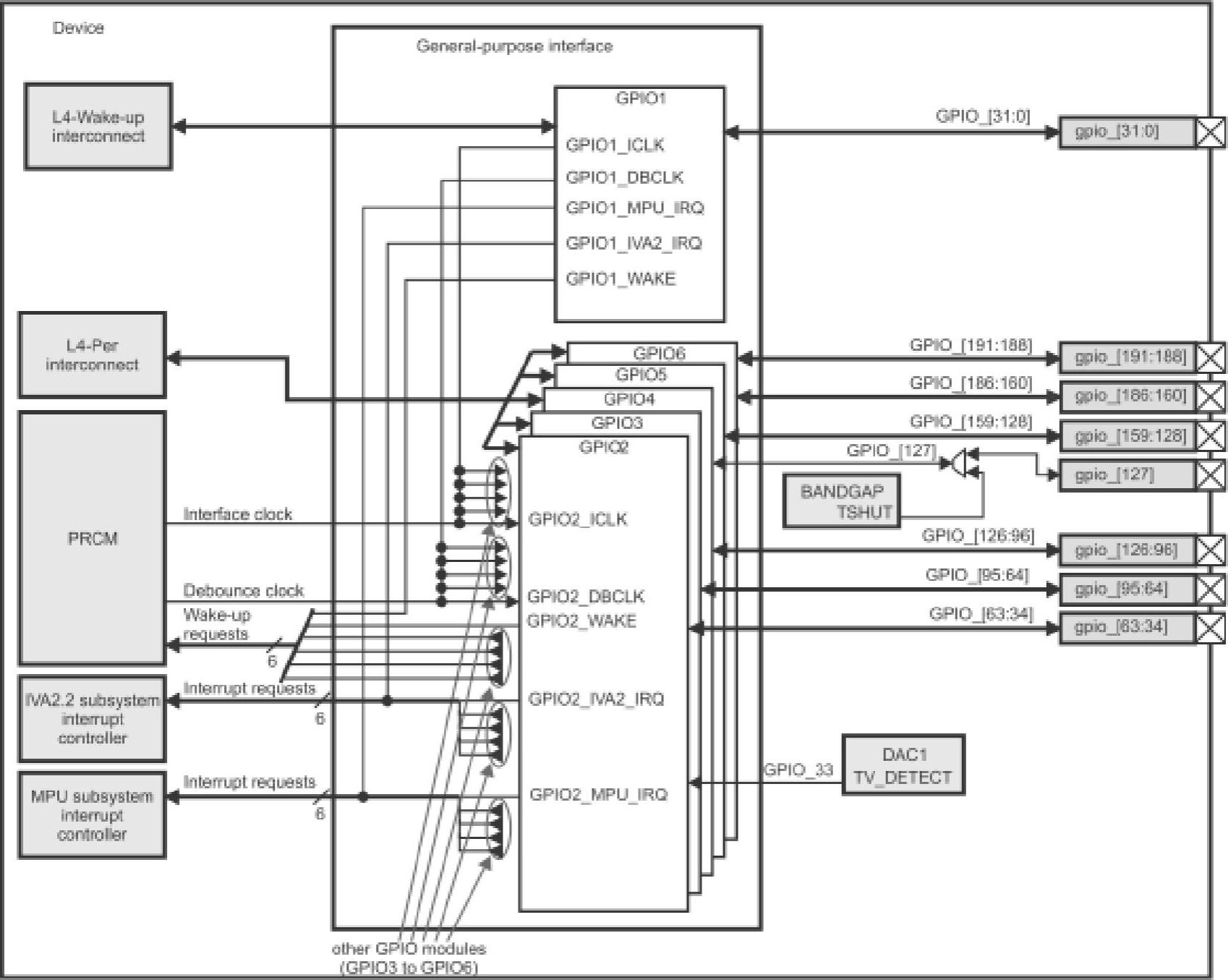

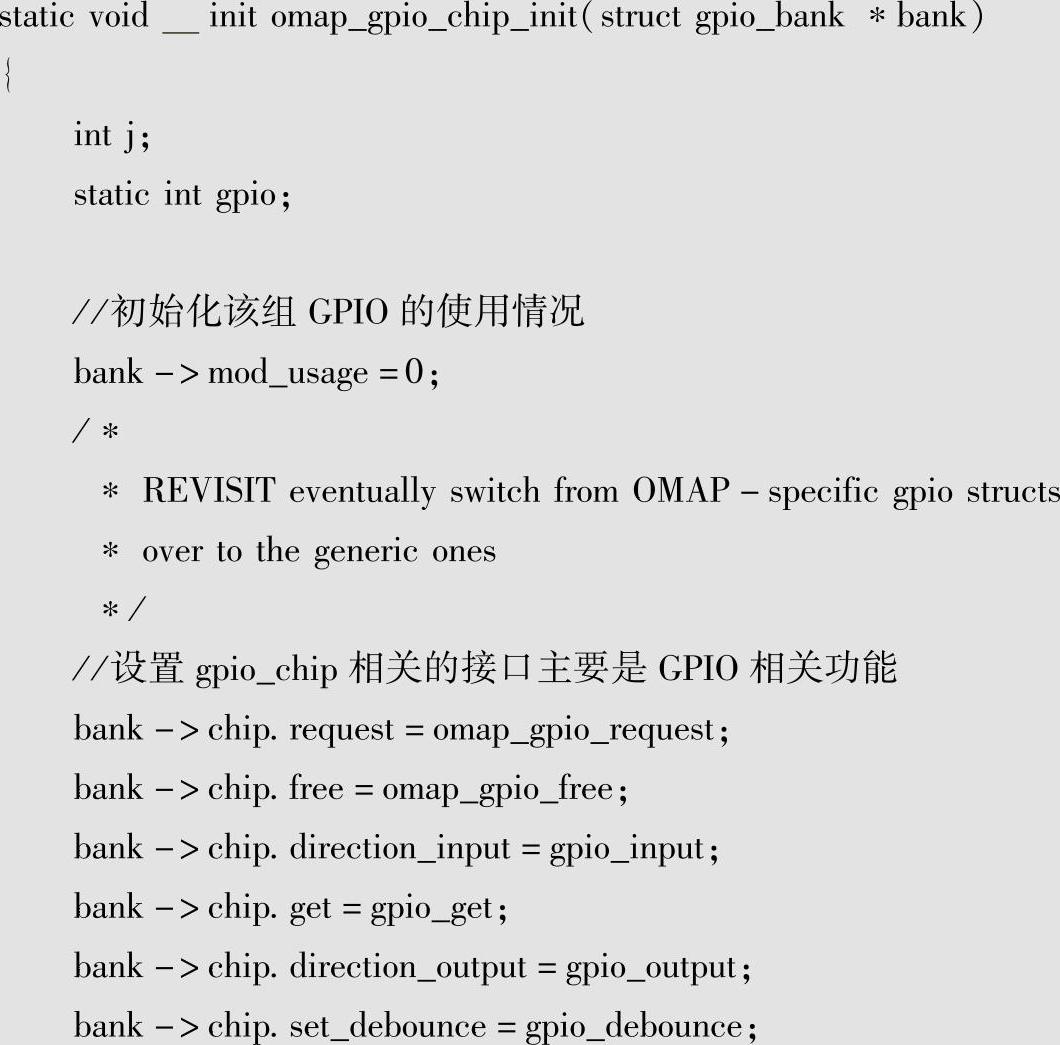

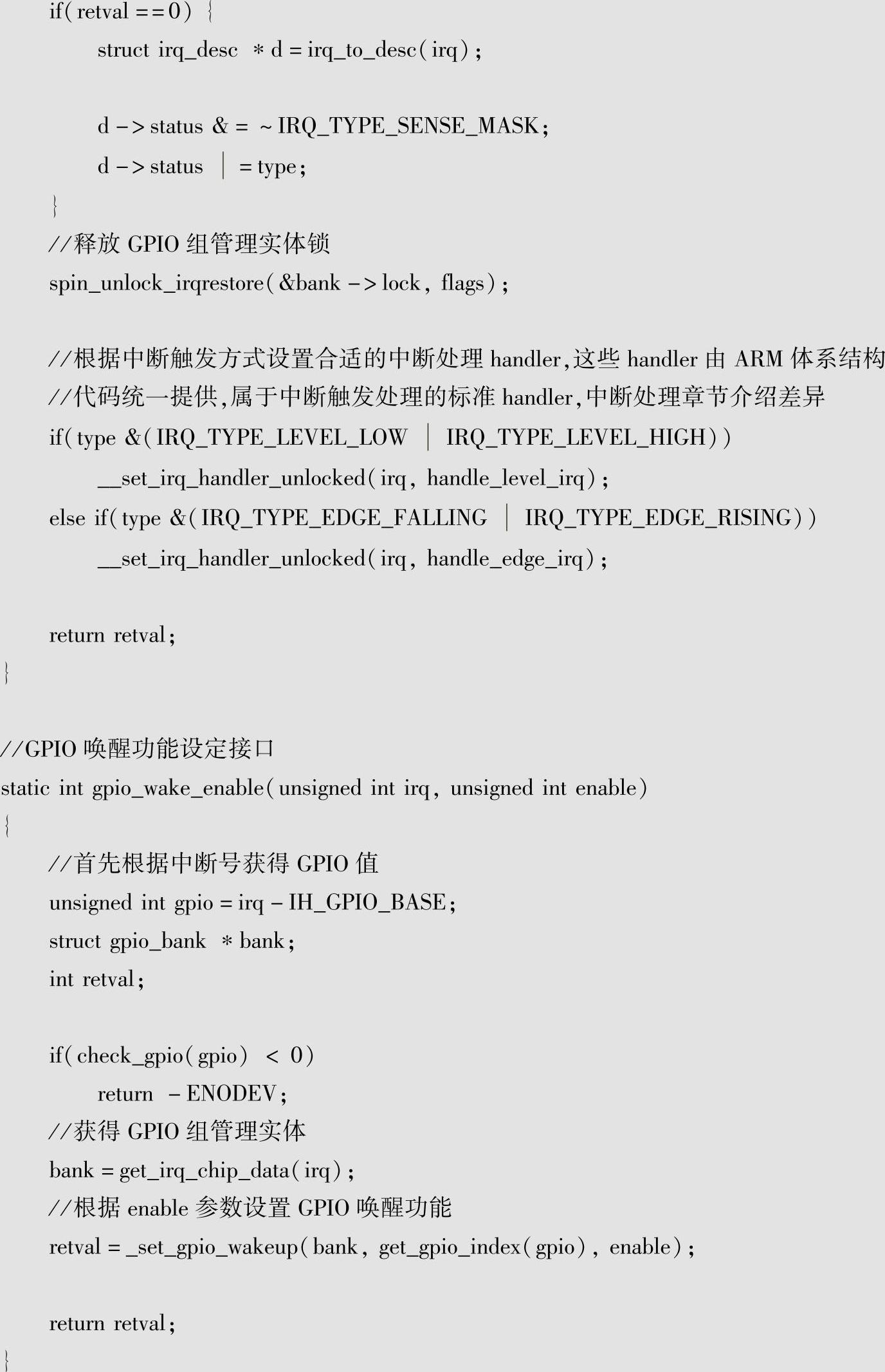

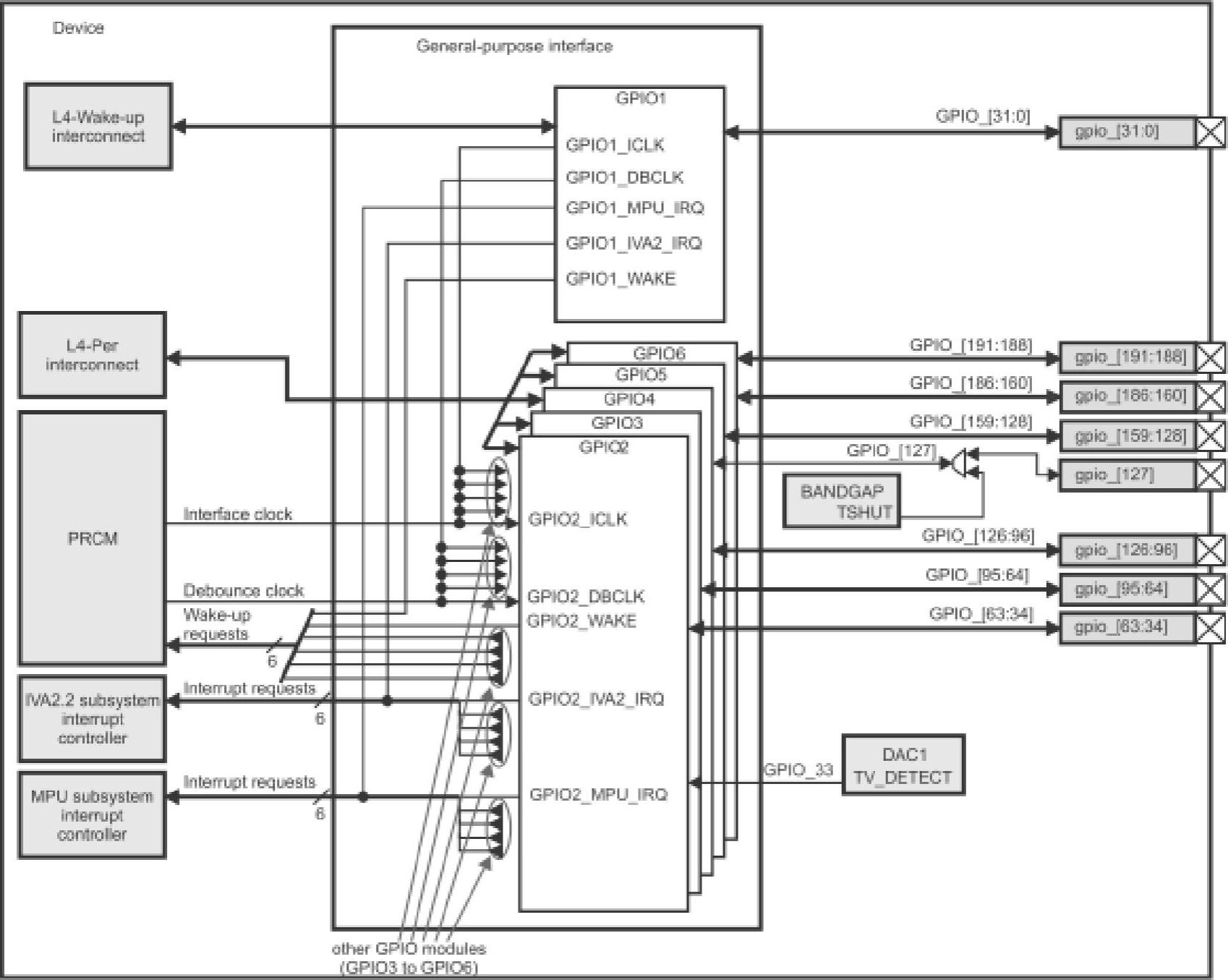

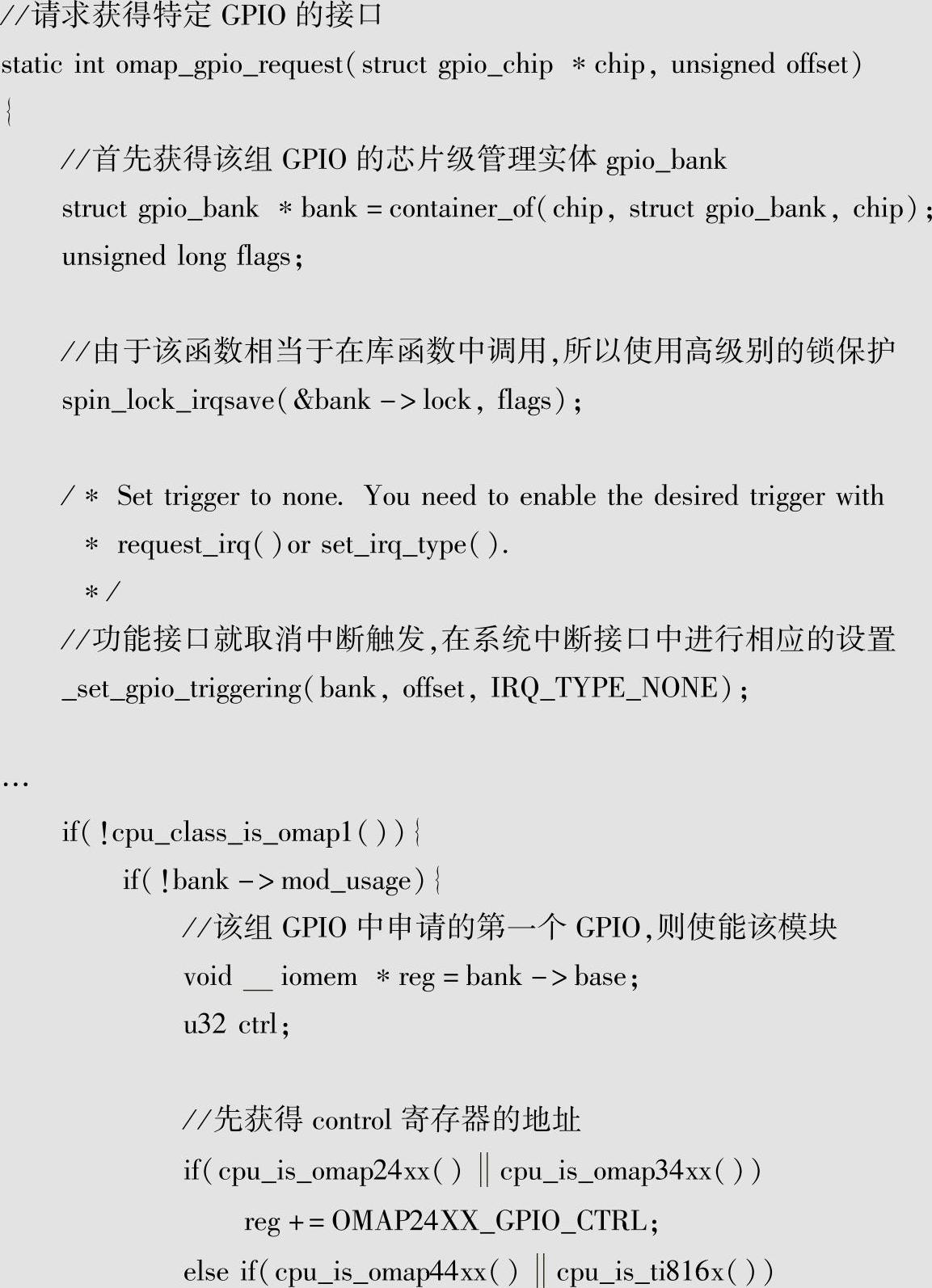

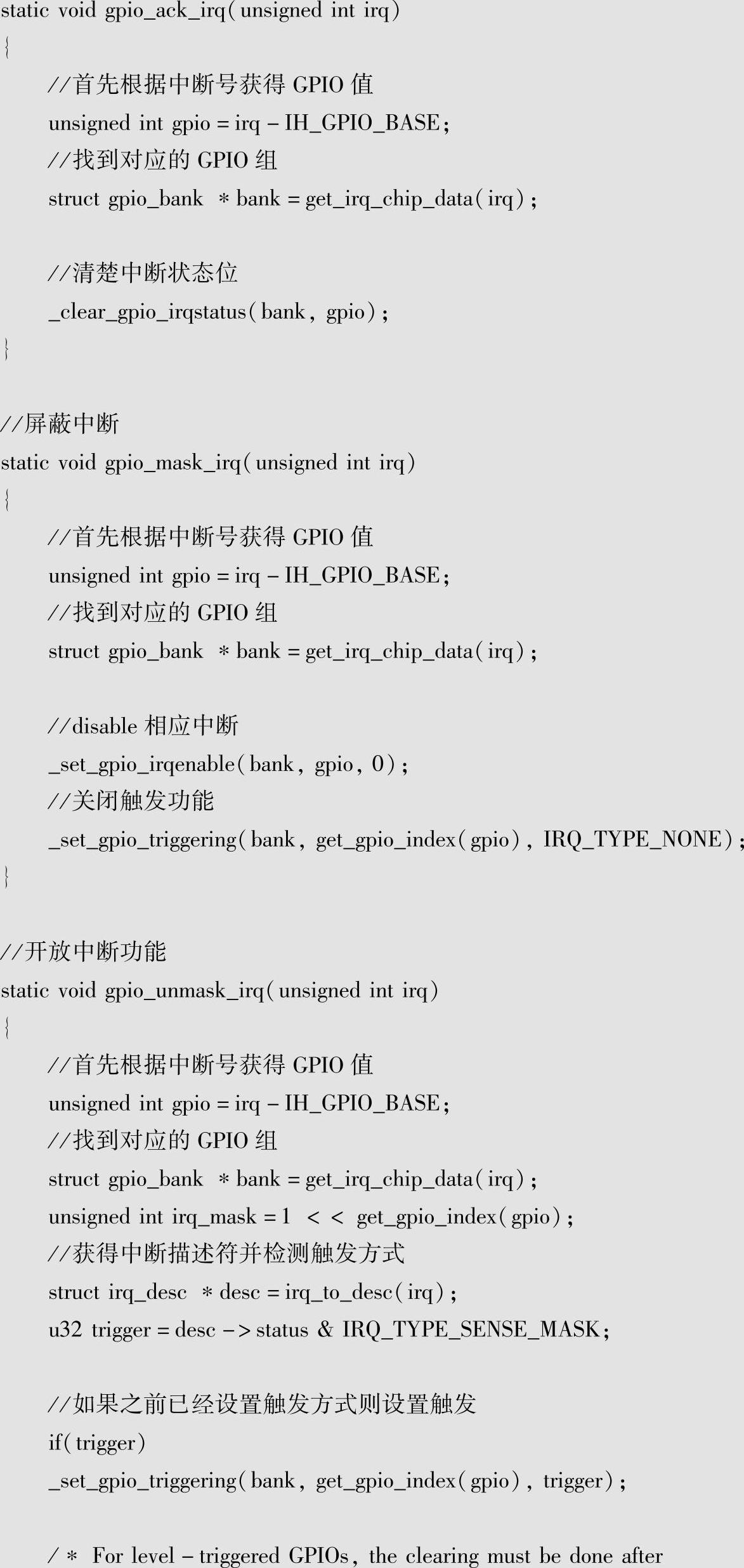

先来看看硬件的框架和细节。DM 3730GPIO子系统框图如图4-50所示,引自《DM3730芯片手册》中第3478页框图。

图4-50 DM 3730GPIO子系统框图

从图4-50可见,DM 3730一共有6组GPIO管理单元,每组管理32个GPIO。其中GPIO1是比较特殊的,其原因在硬件电源管理技术中已提到,GPIO1在WKUP domain中,而其他组的GPIO在其他的power domain中。WKUP domain是特殊的power domain,该do-main的模块会一直供电。在每组GPIO中,除了标准的时钟之外,还有debounce clock用来进行debounce处理(主要在作为input时去抖,避免抖动产生的错误结果),另外还有唤醒系统的功能。GPIO的中断信号同样可以提供给ARMMPU和IVADSP,从而不同的核都可以对外部的GPIO进行操作。

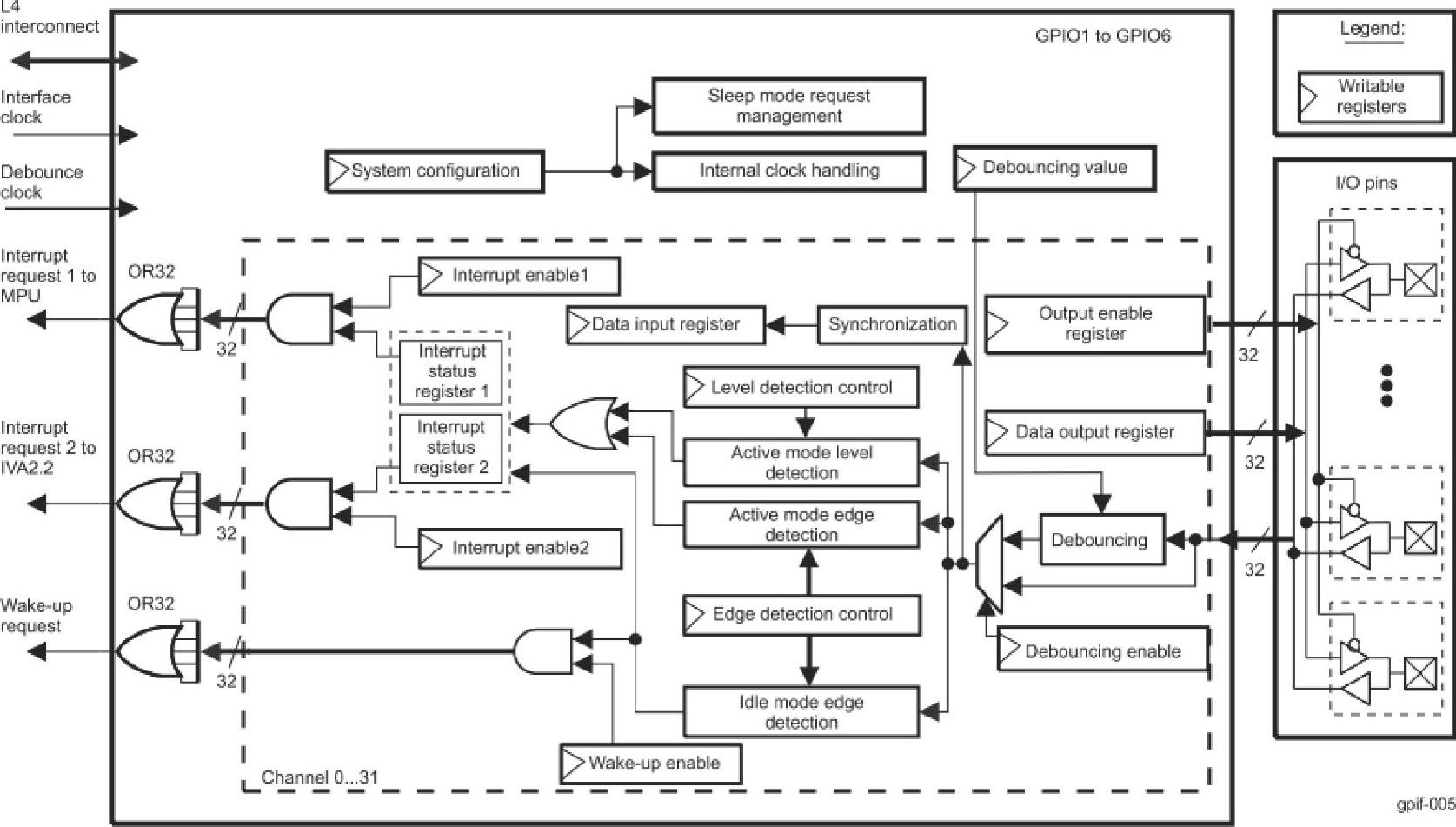

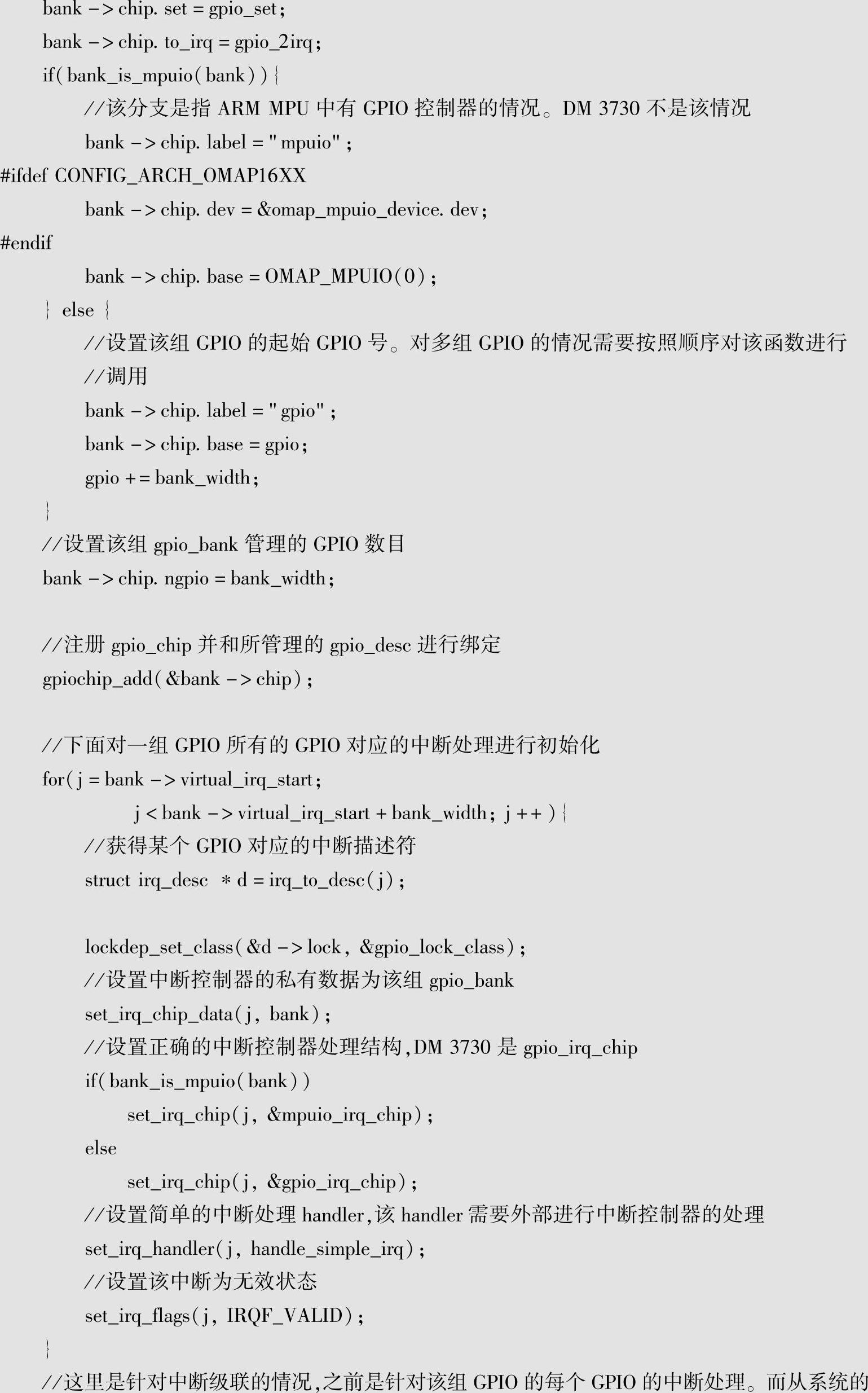

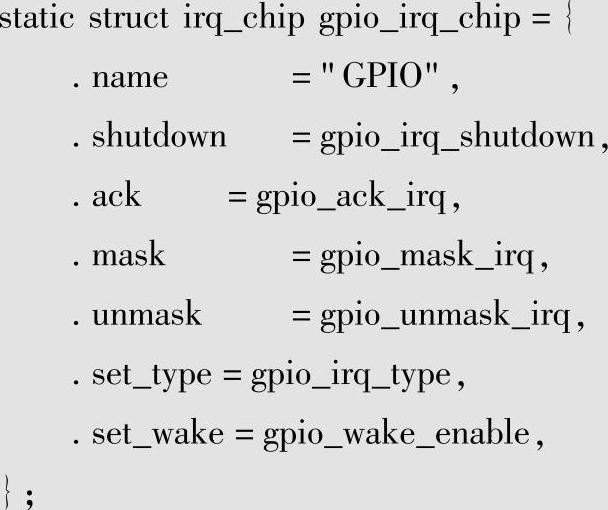

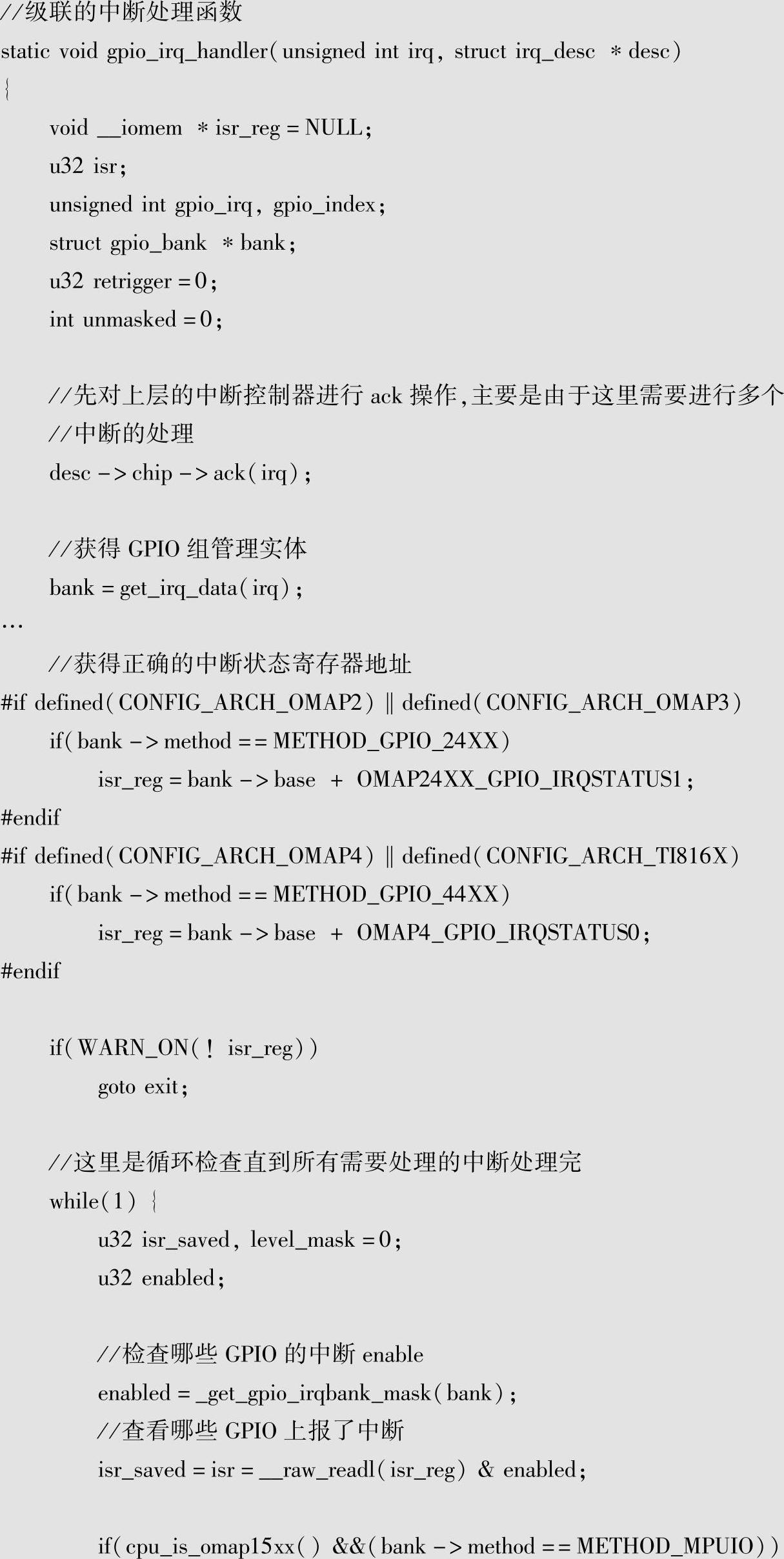

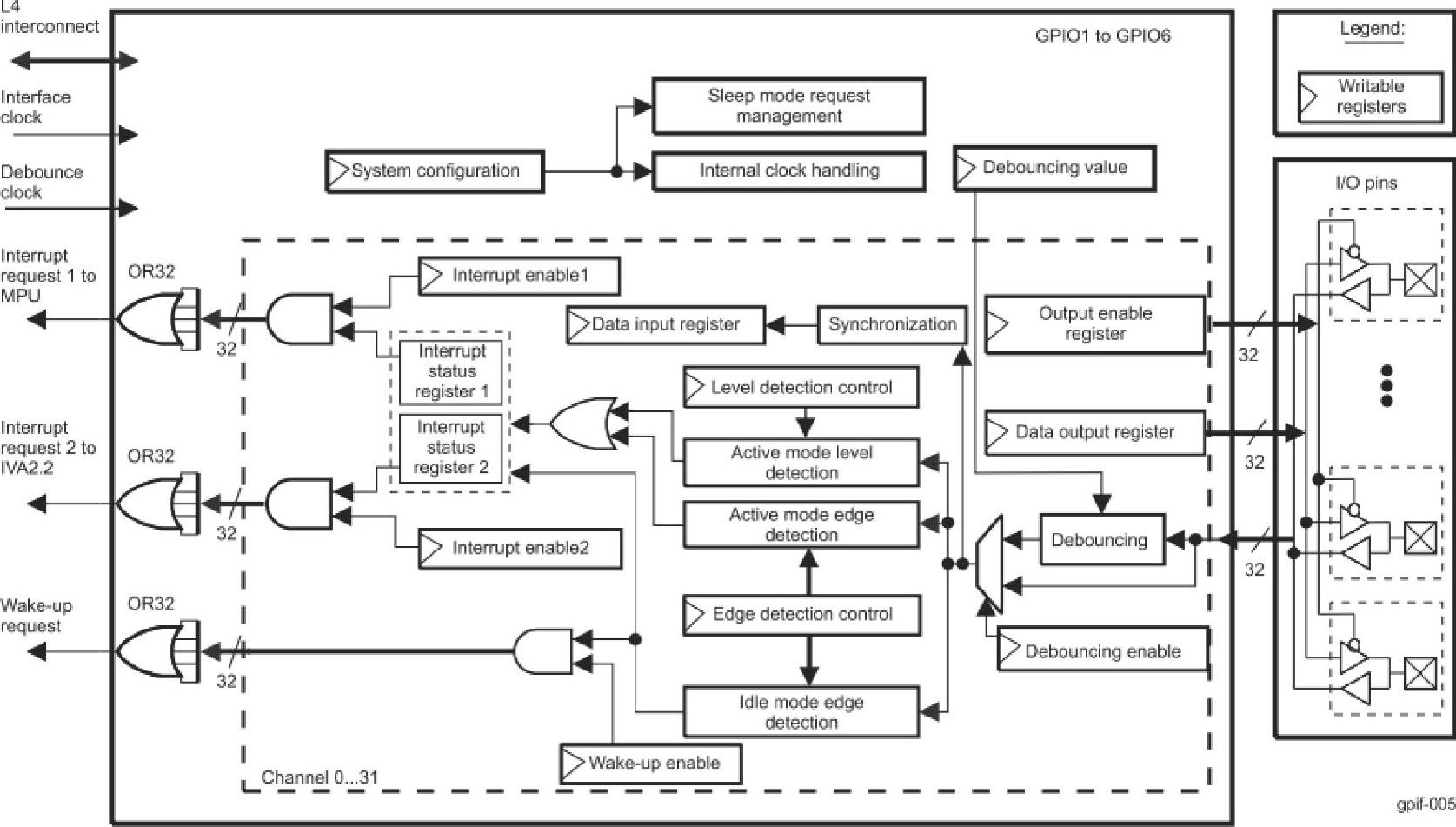

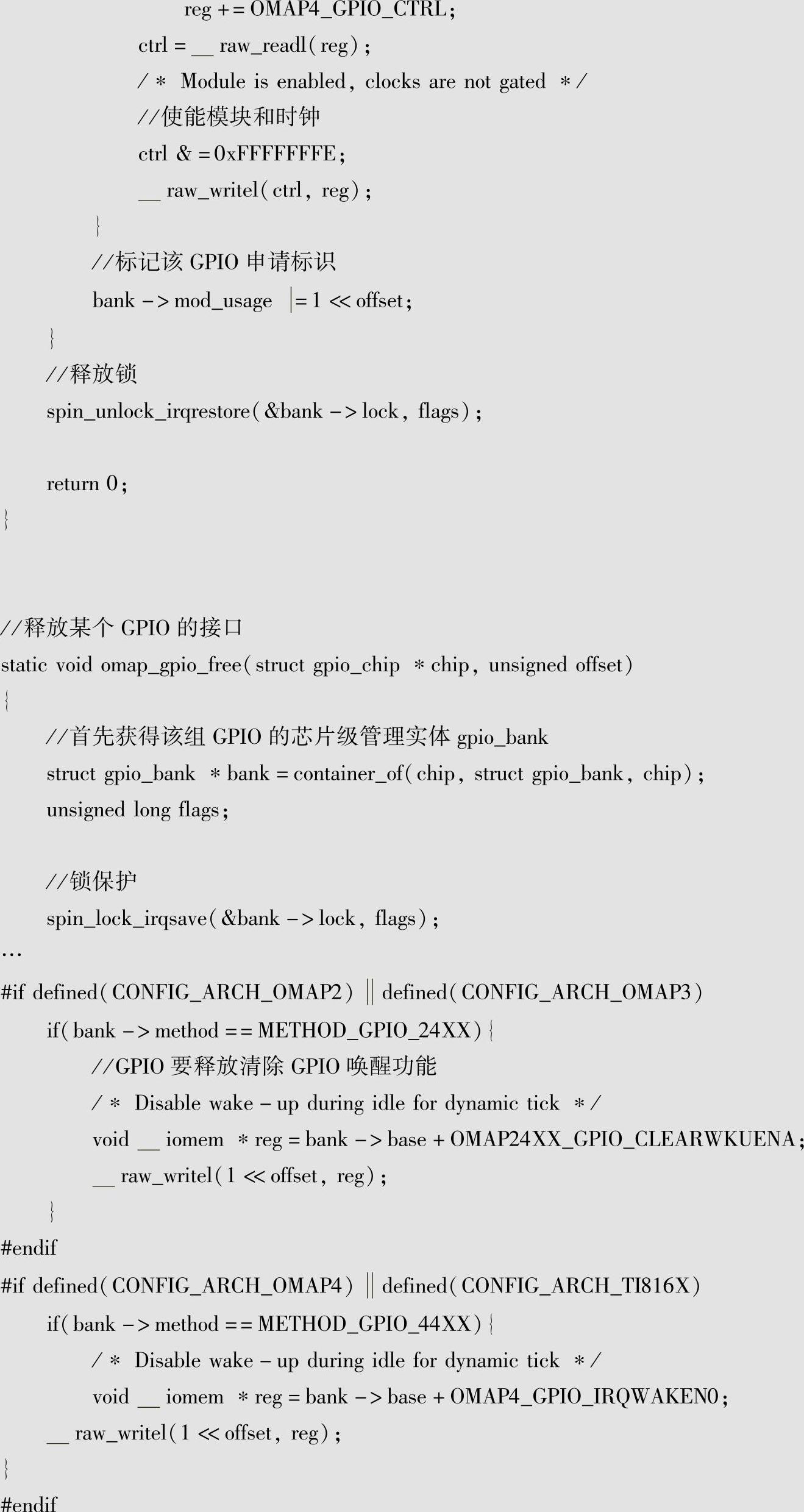

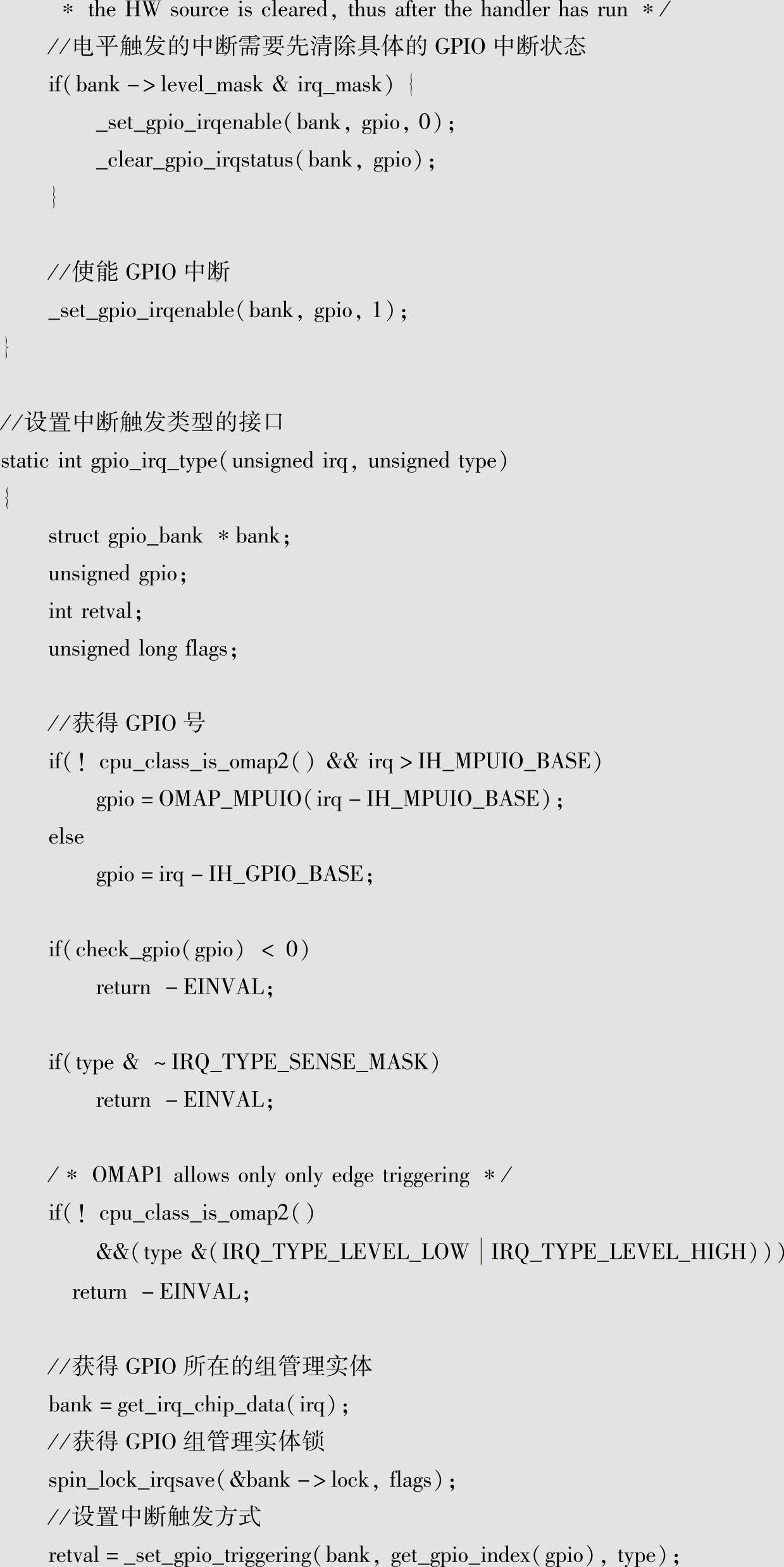

关于GPIO内部的系统设计如图4-51所示。图4-51引自《DM 3730芯片手册》中第3490页框图。

图4-51 DM 3730GPIO内部系统设计图

从图4-51中可见,一组GPIO的设置寄存器接口,主要由系统控制、中断管理、去抖模块、输入输出特性等不同功能设置寄存器对相应的功能进行设置。

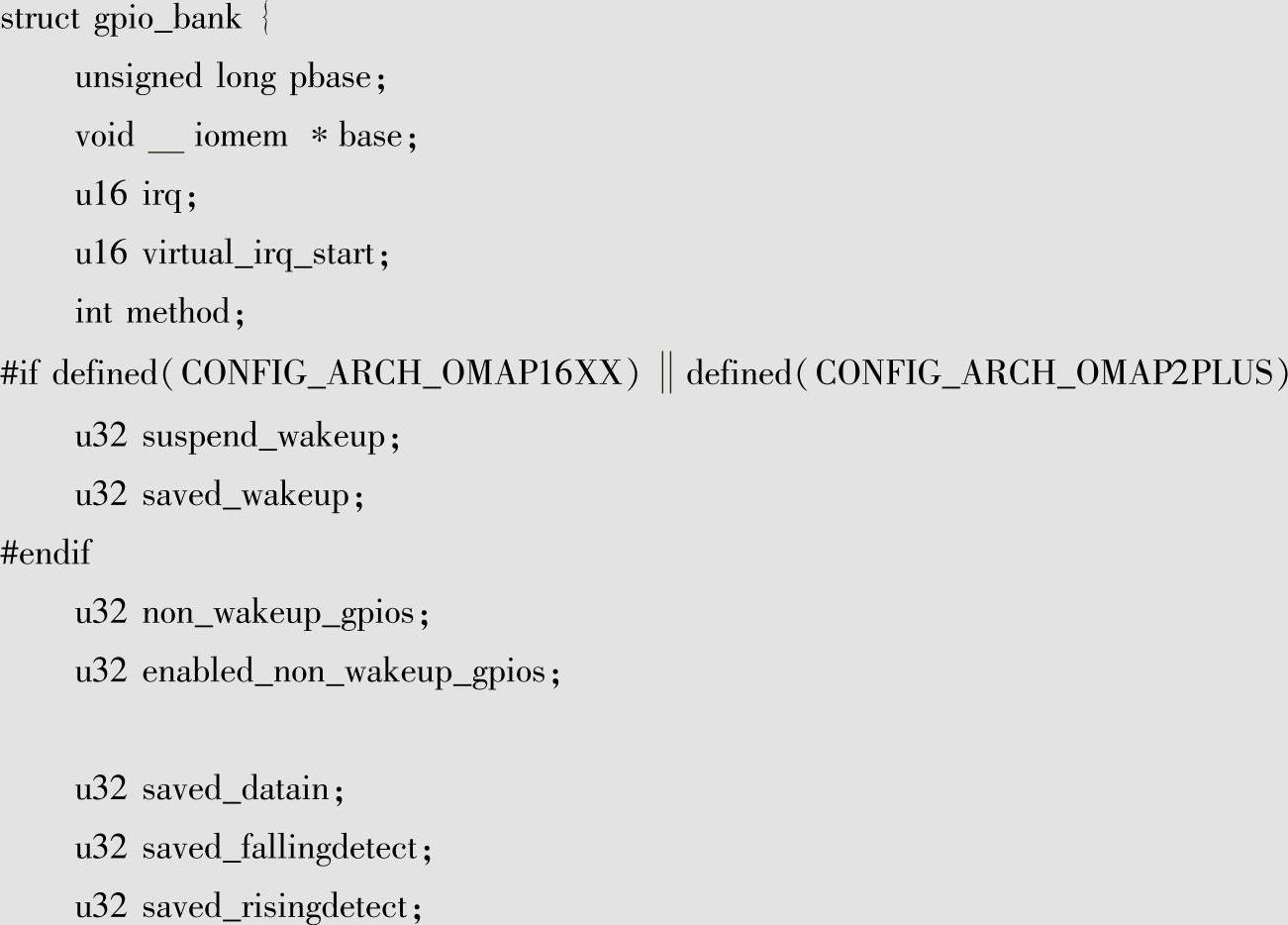

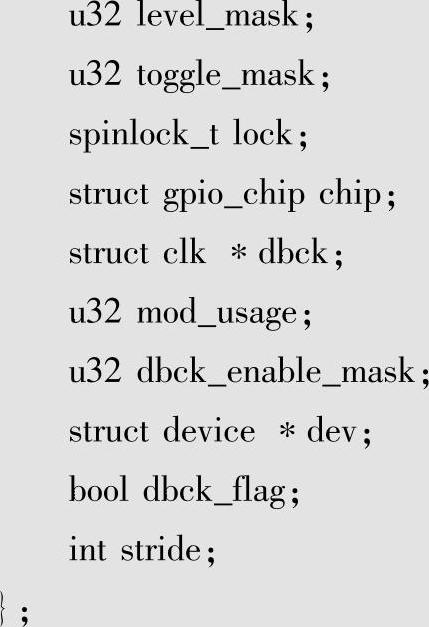

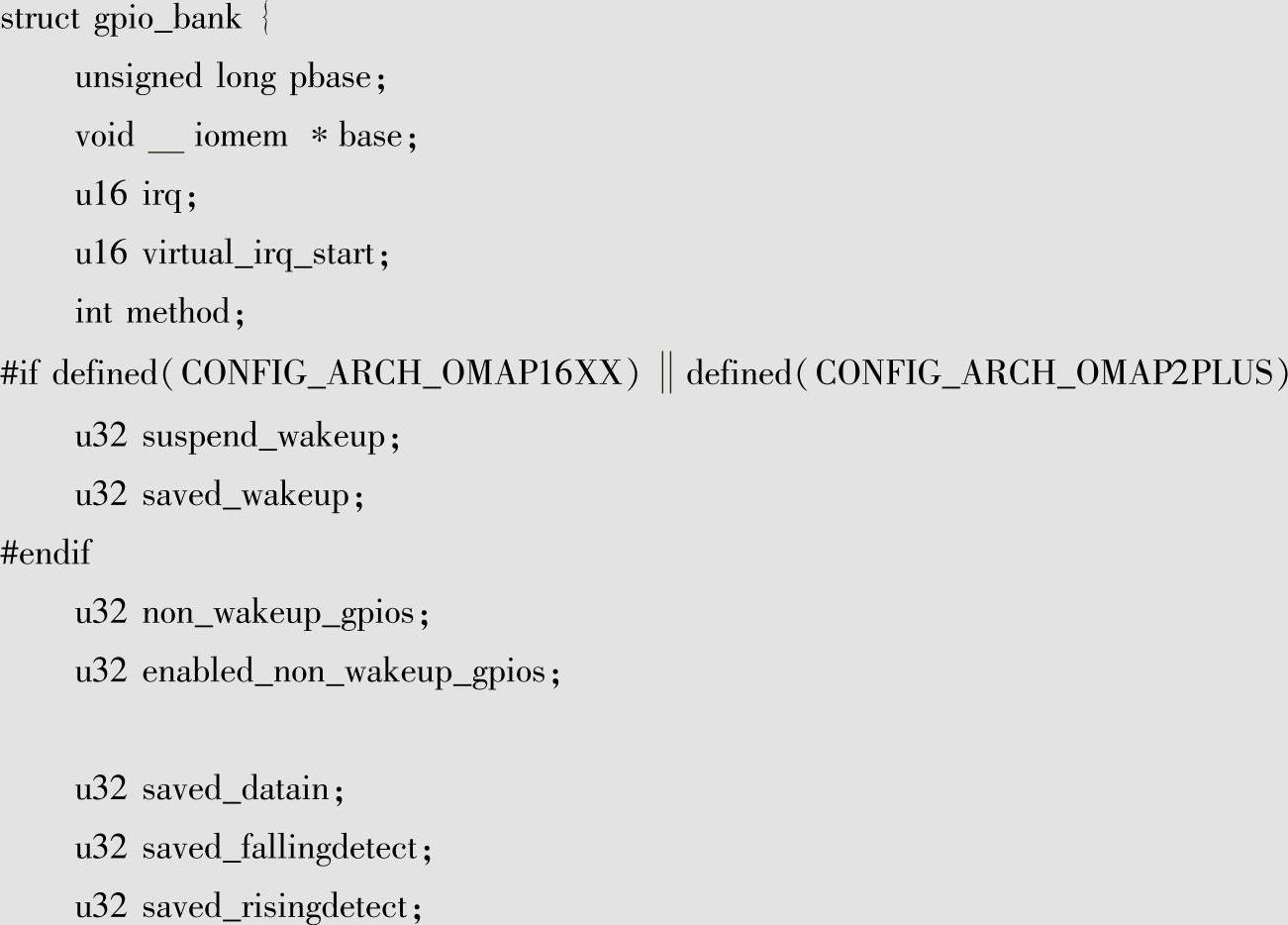

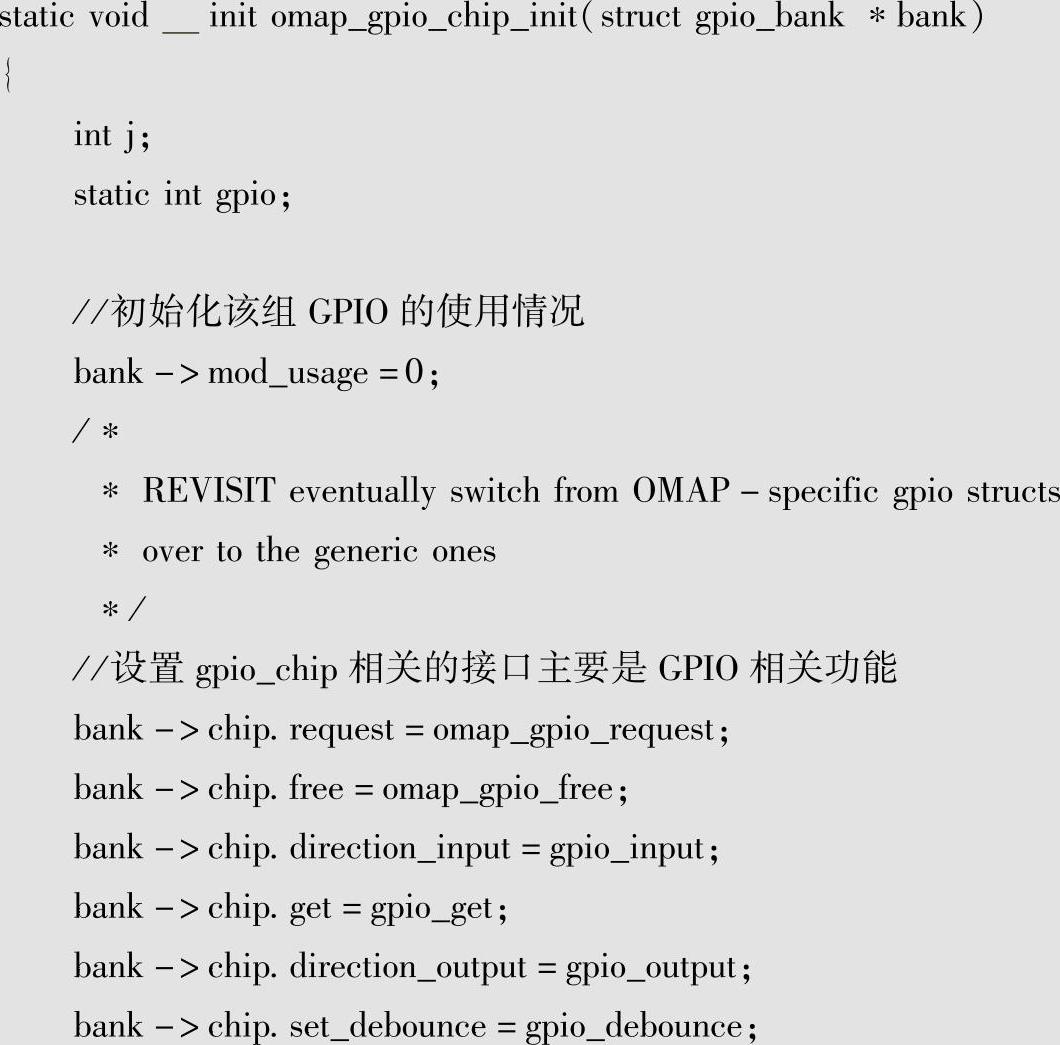

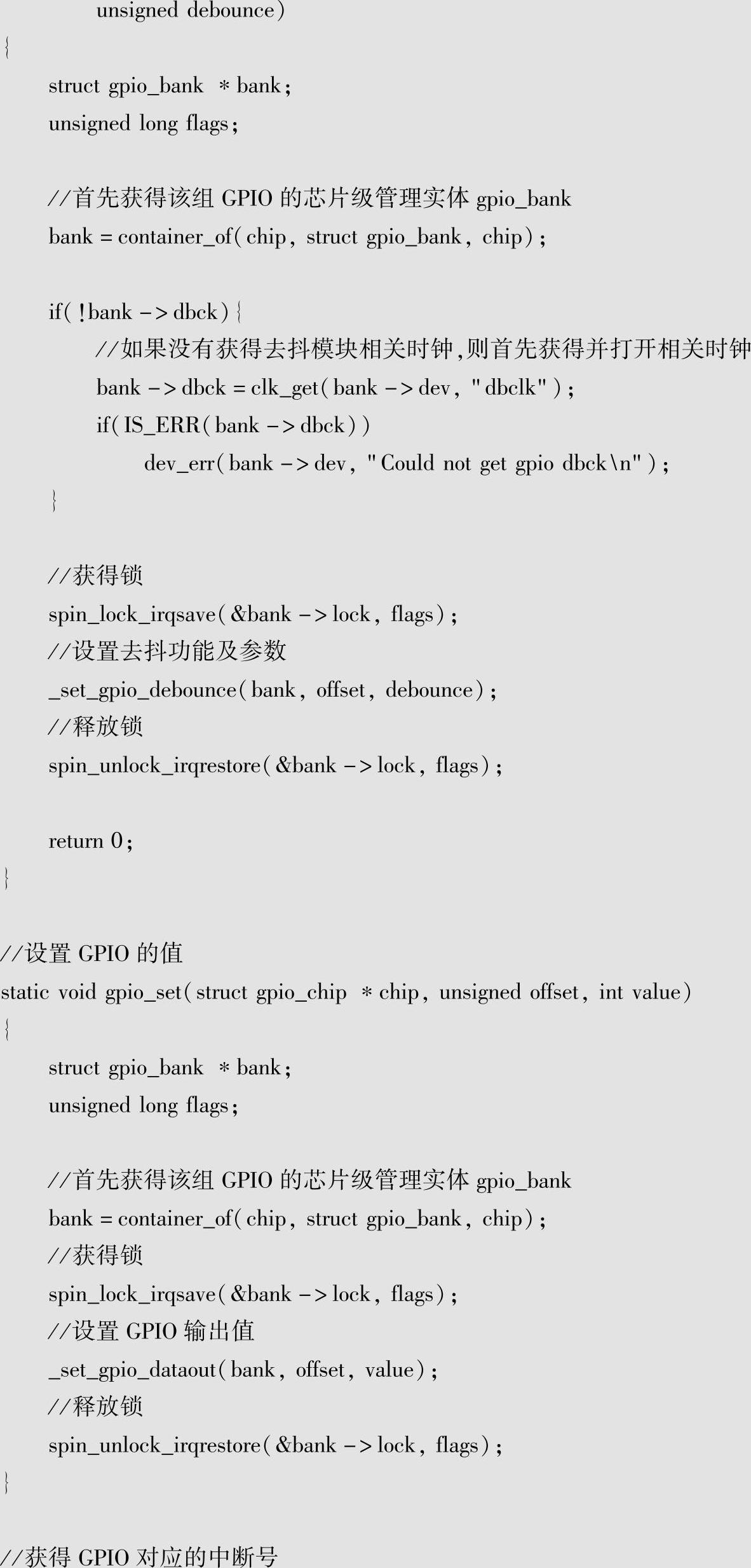

针对软件的实现,使用GPIO lib提供的管理实体gpio_chip不能满足DM 3730关于GPIO控制管理的需求,所以在芯片代码中对gpio_chip进行了封装并加入芯片特定的管理属性形成gpio_bank结构,详细内容如下:

作为DM 3730芯片GPIO管理的核心数据结构,gpio_bank中已经包含了GPIO lib需要的gpio_chip,这样的实现符合面向对象的方法,从体系结构层次的角度考虑也是底层包含上层的内容。另外gpio_bank中还包含了用于GPIO控制的属性,这些属性会在具体的操作中用到。

下面介绍详细的实现。

1ᤫ重要的初始化实现

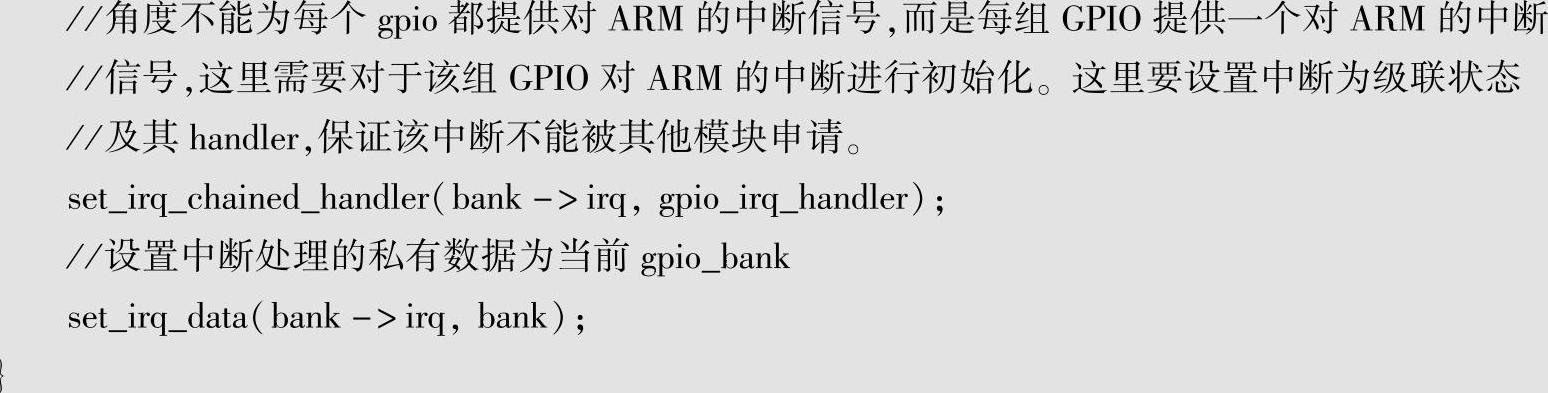

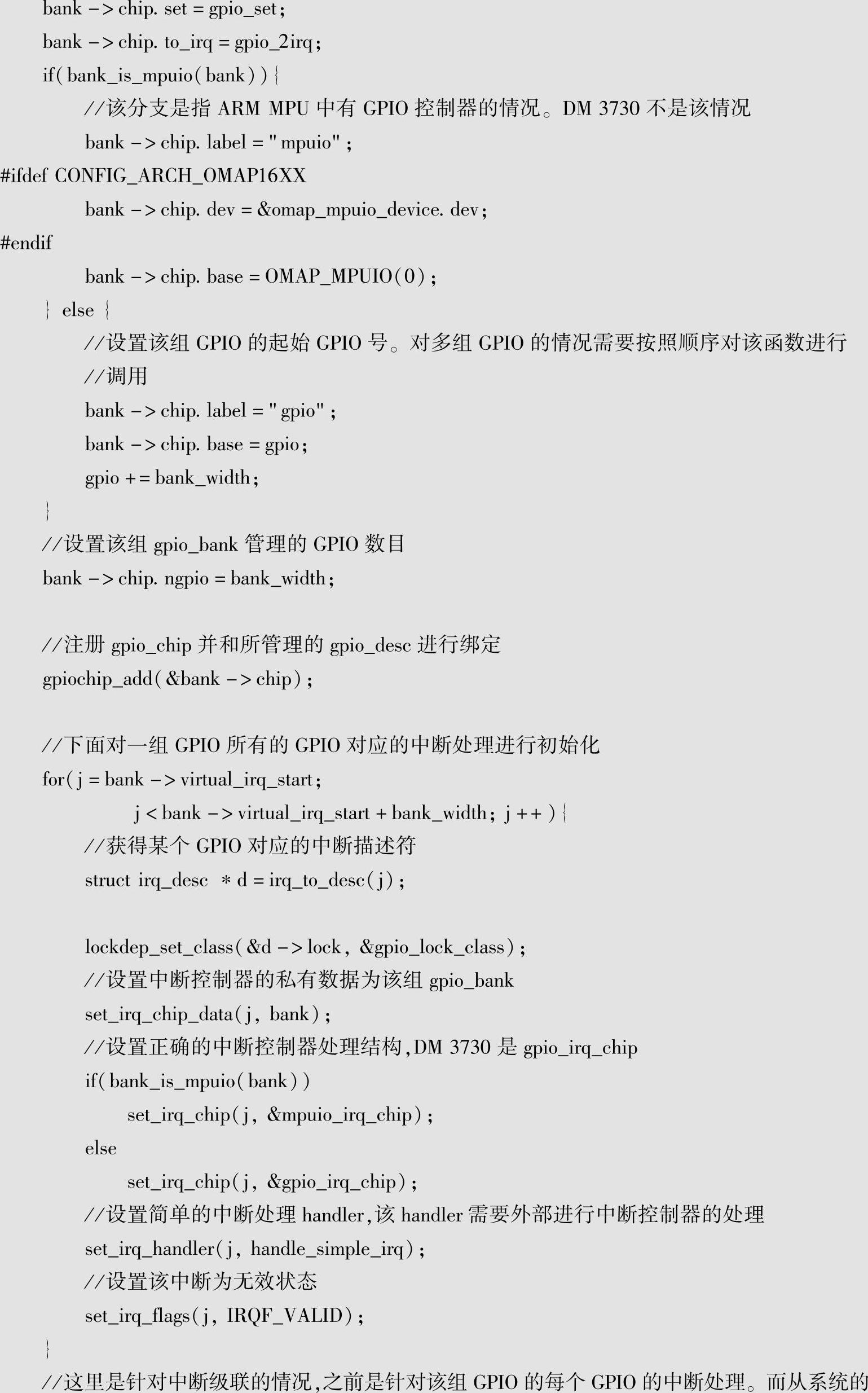

对于GPIO功能芯片特殊的实现和GPIO lib的接口就是gpio_chip。而芯片特殊实现本身也和填充gpio_chip以及注册gpio_chip相关,这些都是在初始化中实现的,了解这些初始化工作就可以大致了解GPIO芯片的特性。DM 3730相关的初始化函数是omap_gpio_chip_init,详细的内容和注释如下:

分析了重要的初始化函数omap_gpio_chip_init之后,可见GPIO分为两个重要的功能组,一组是gpio_chip相关的功能接口,另一组是和中断相关的功能。下面分两部分进行详细的代码解析。

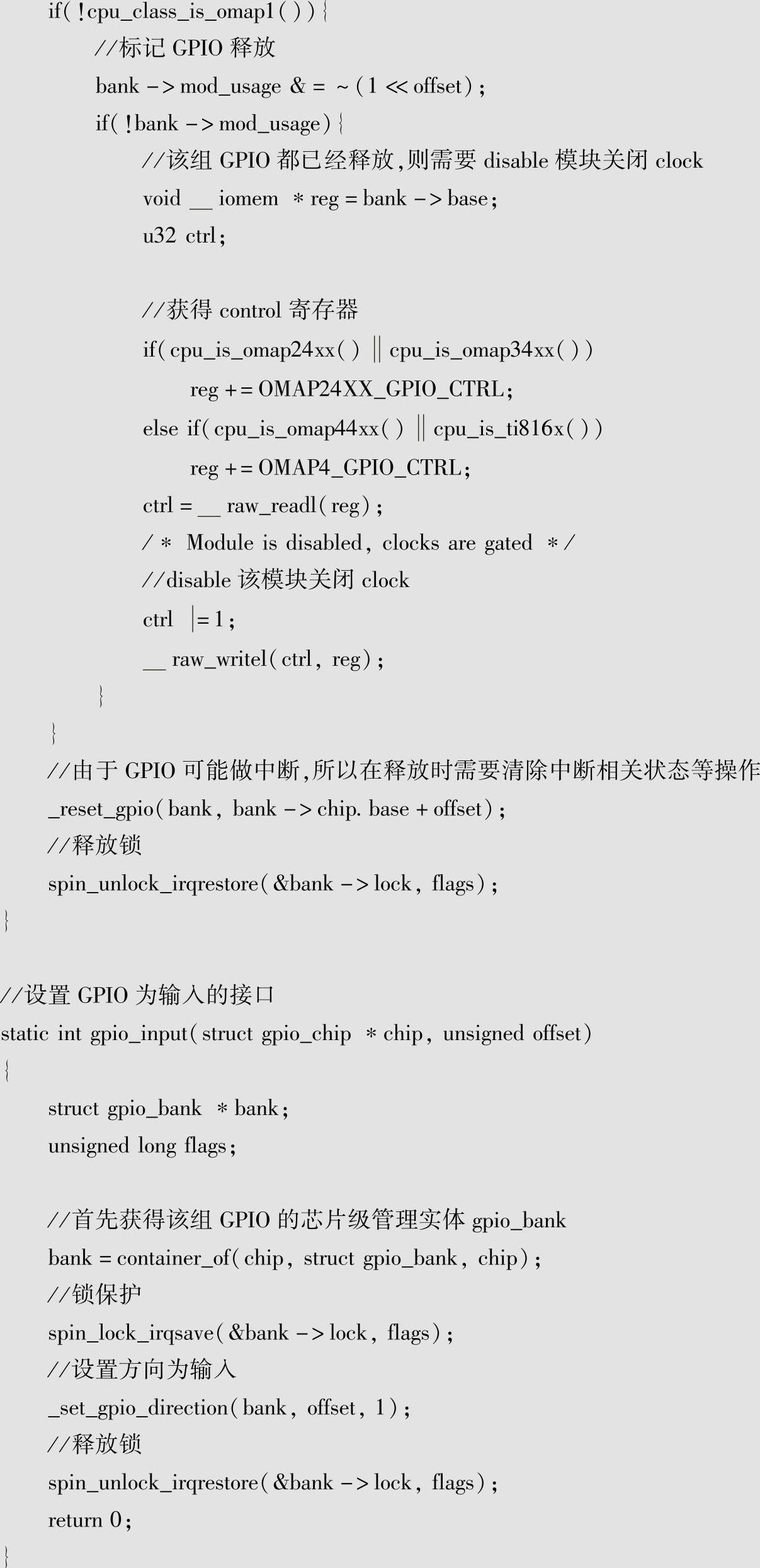

2ᤫgpio_chip功能接口

GPIO的功能主要是通过gpio_chip的功能接口实现的。下面对相关实现代码进行详细解析:

(https://www.chuimin.cn)

(https://www.chuimin.cn)

对GPIO相关功能的芯片特殊实现,主要进行了函数功能的分析,具体到子函数的细节可以查看相关代码。

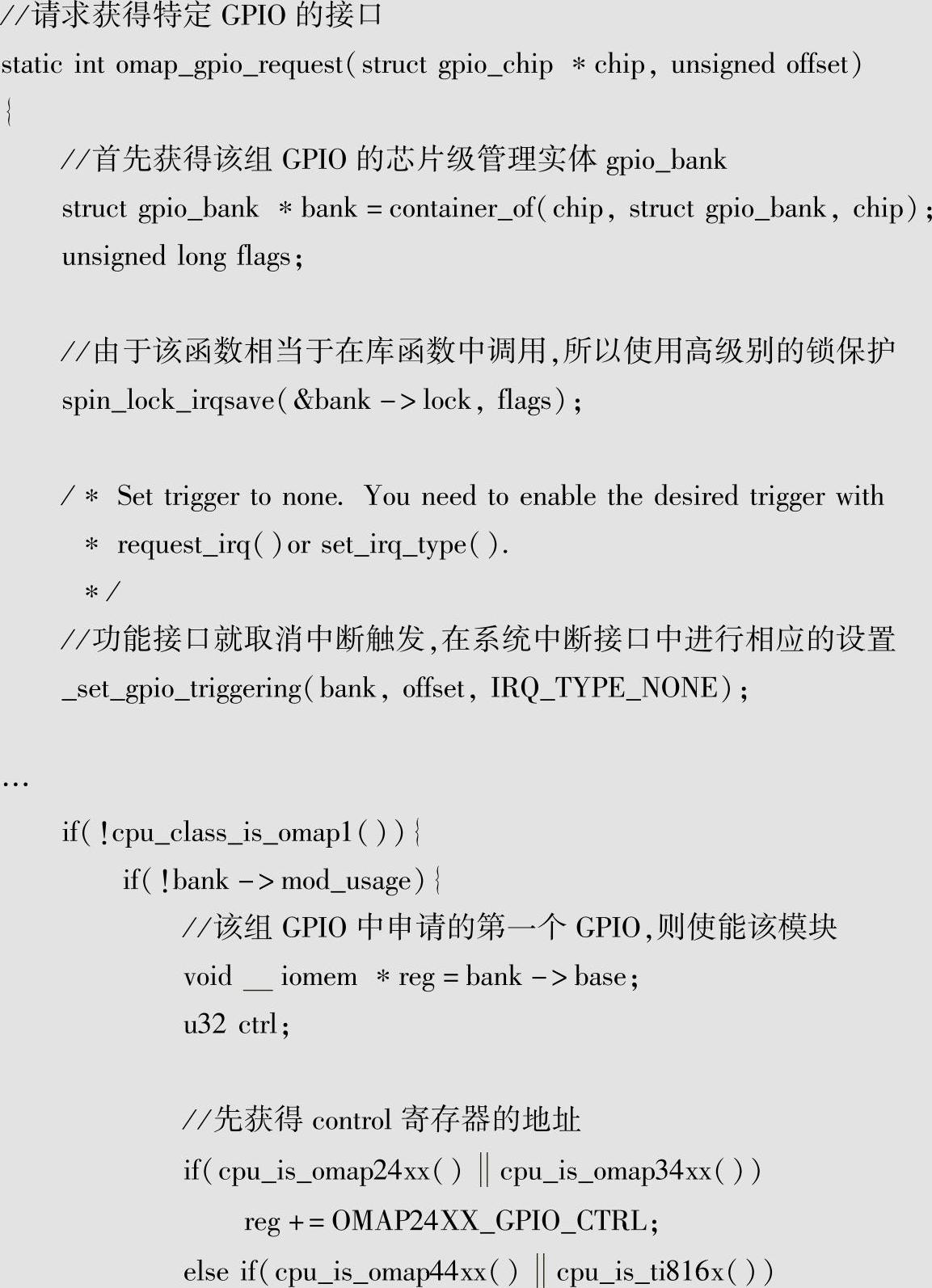

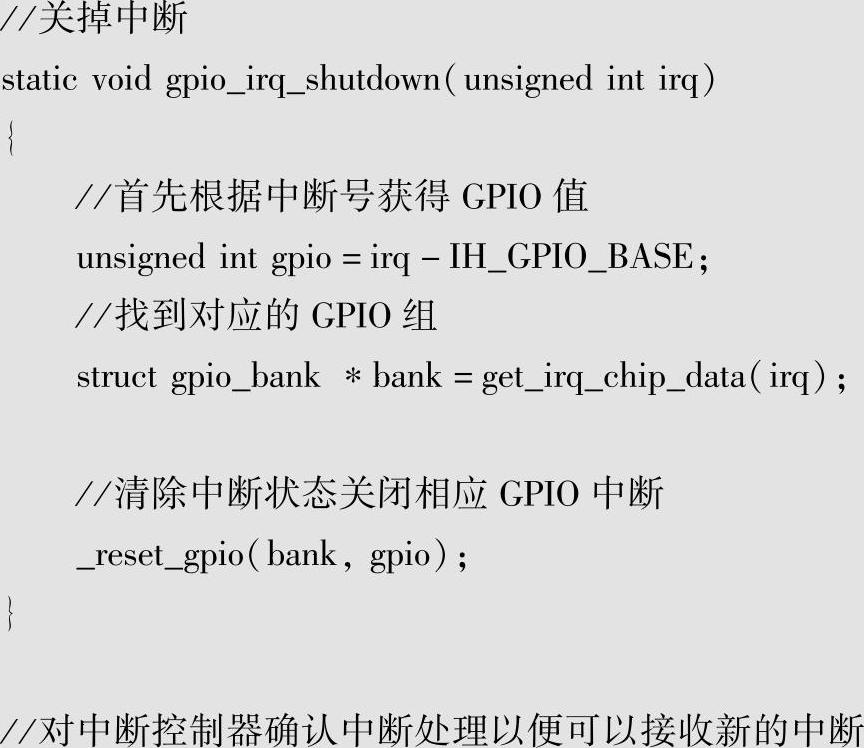

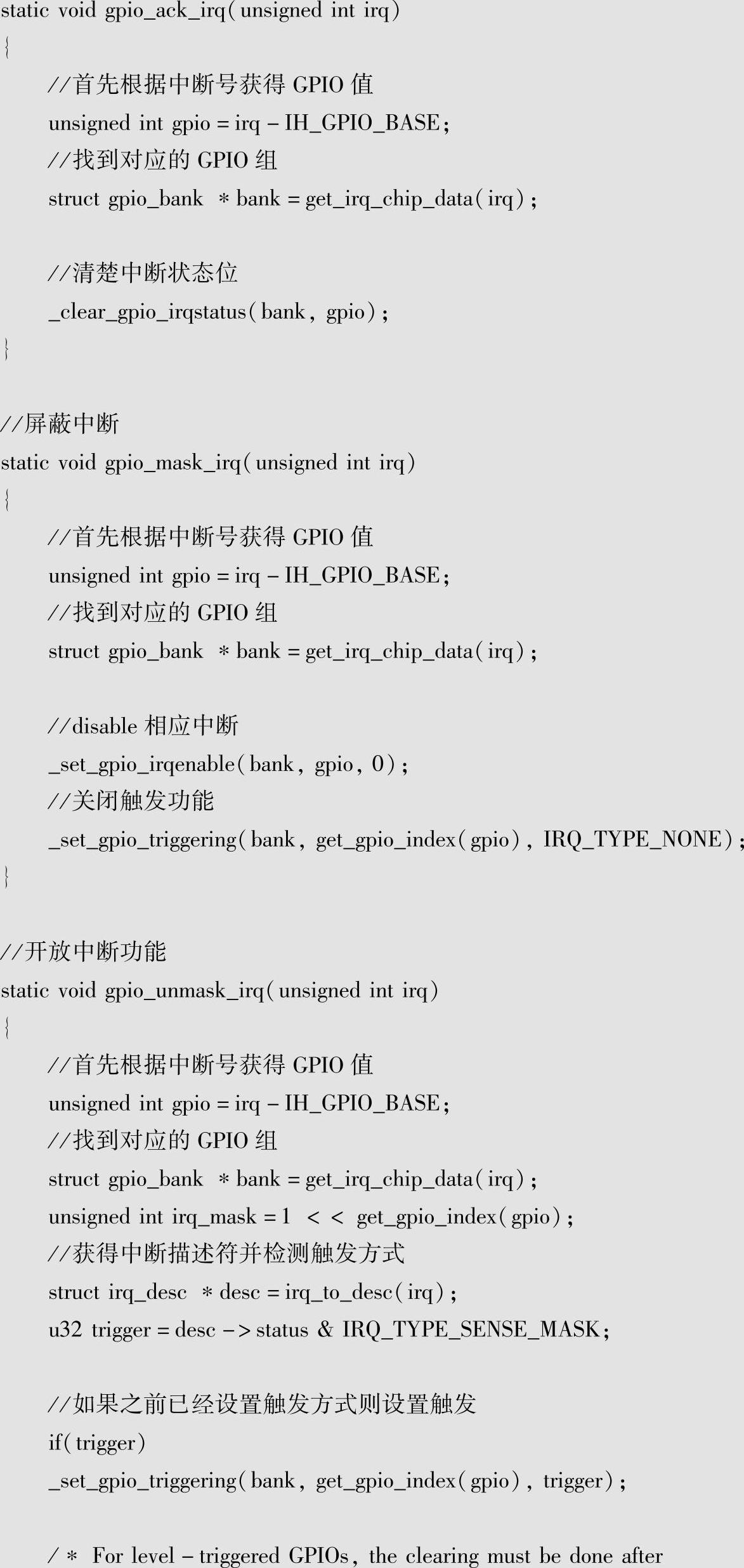

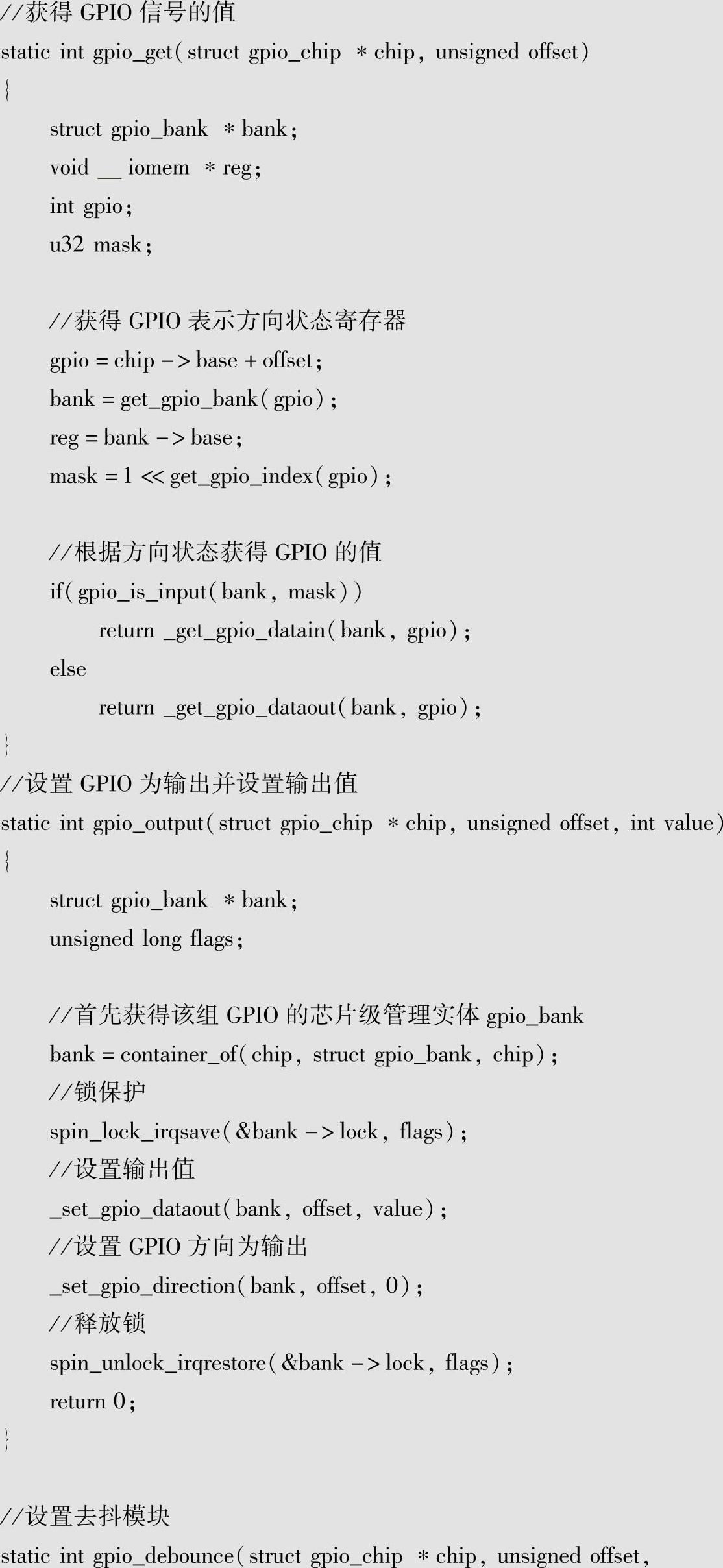

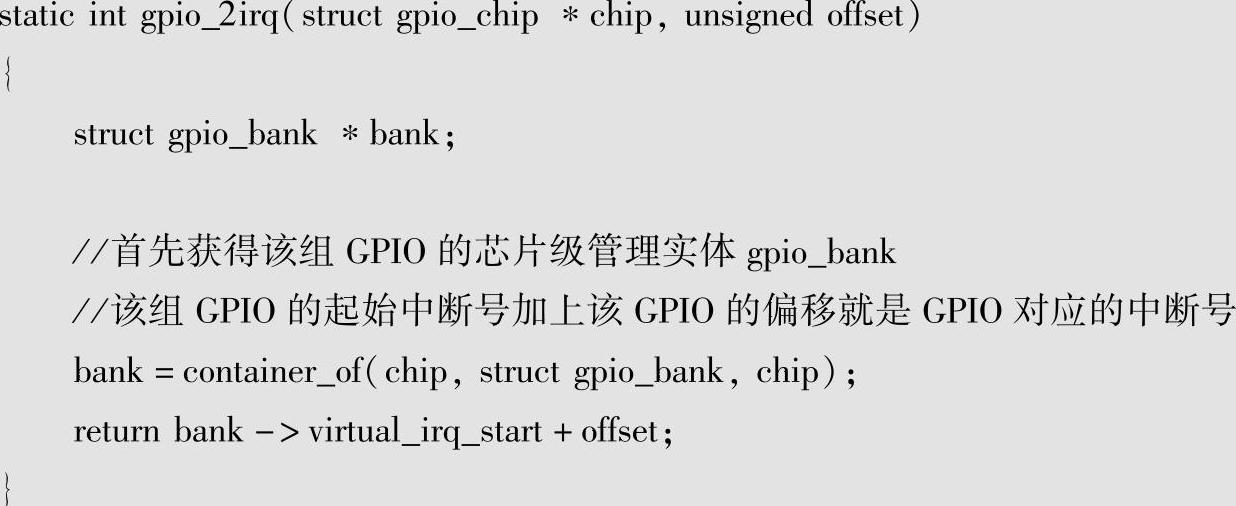

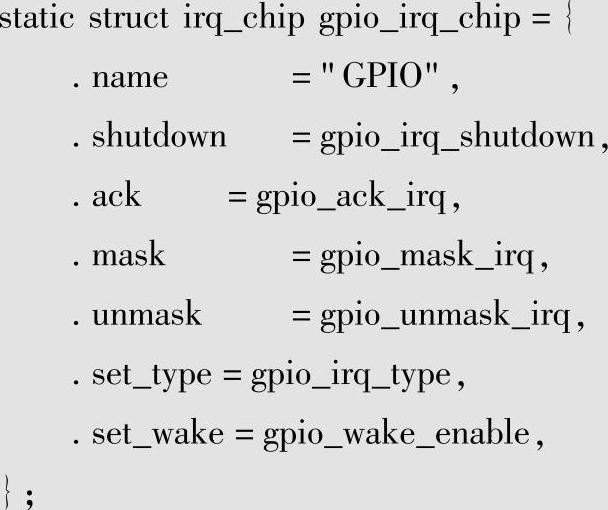

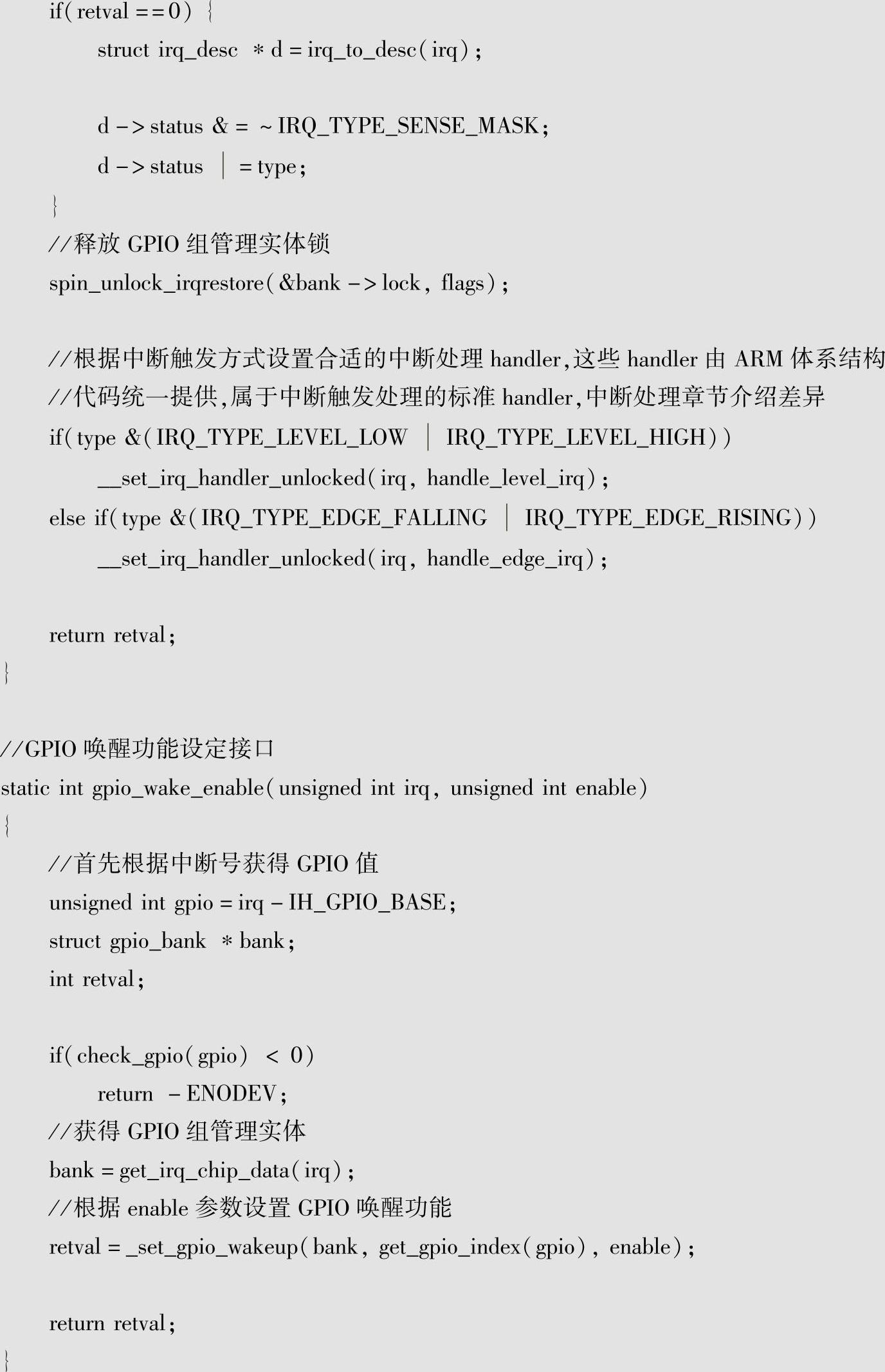

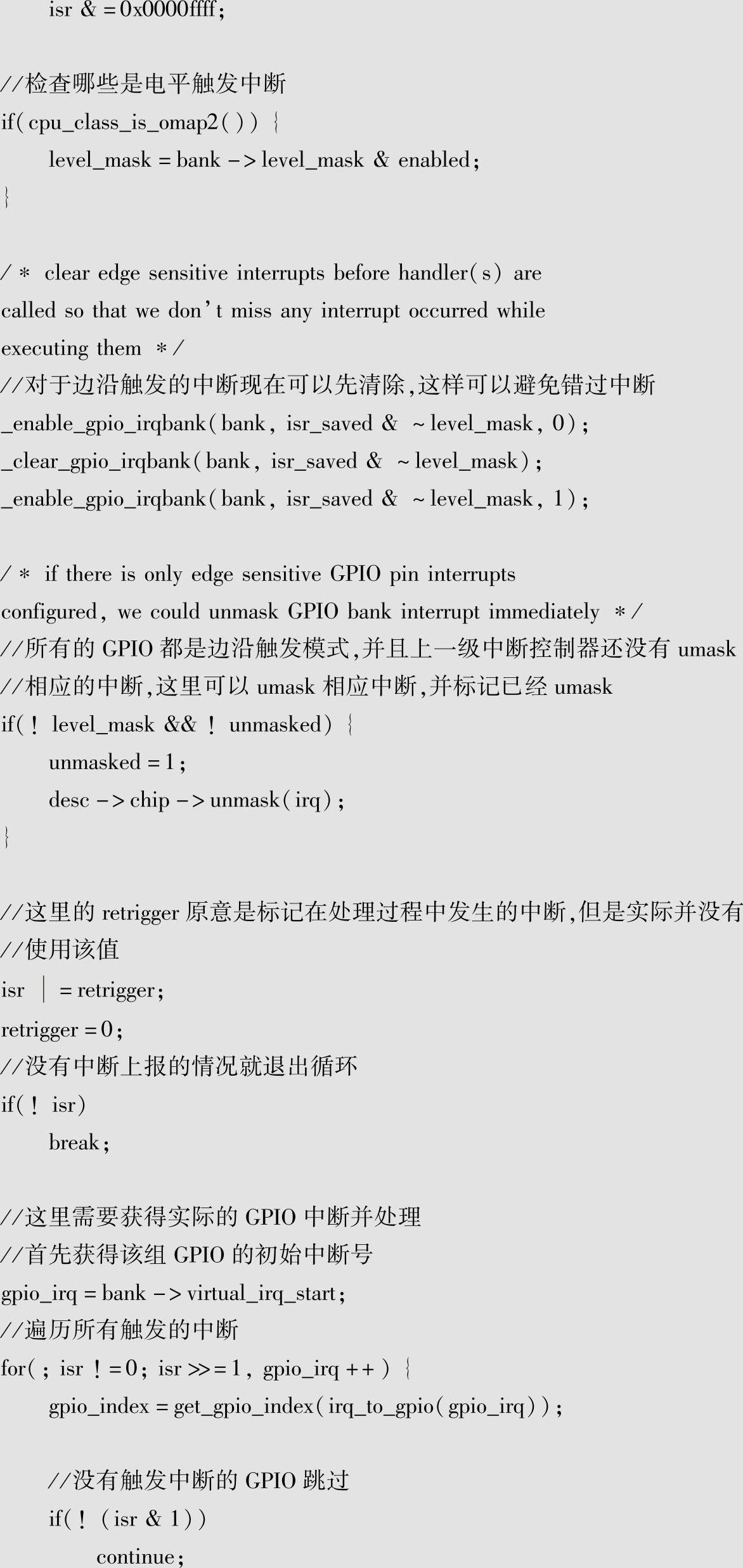

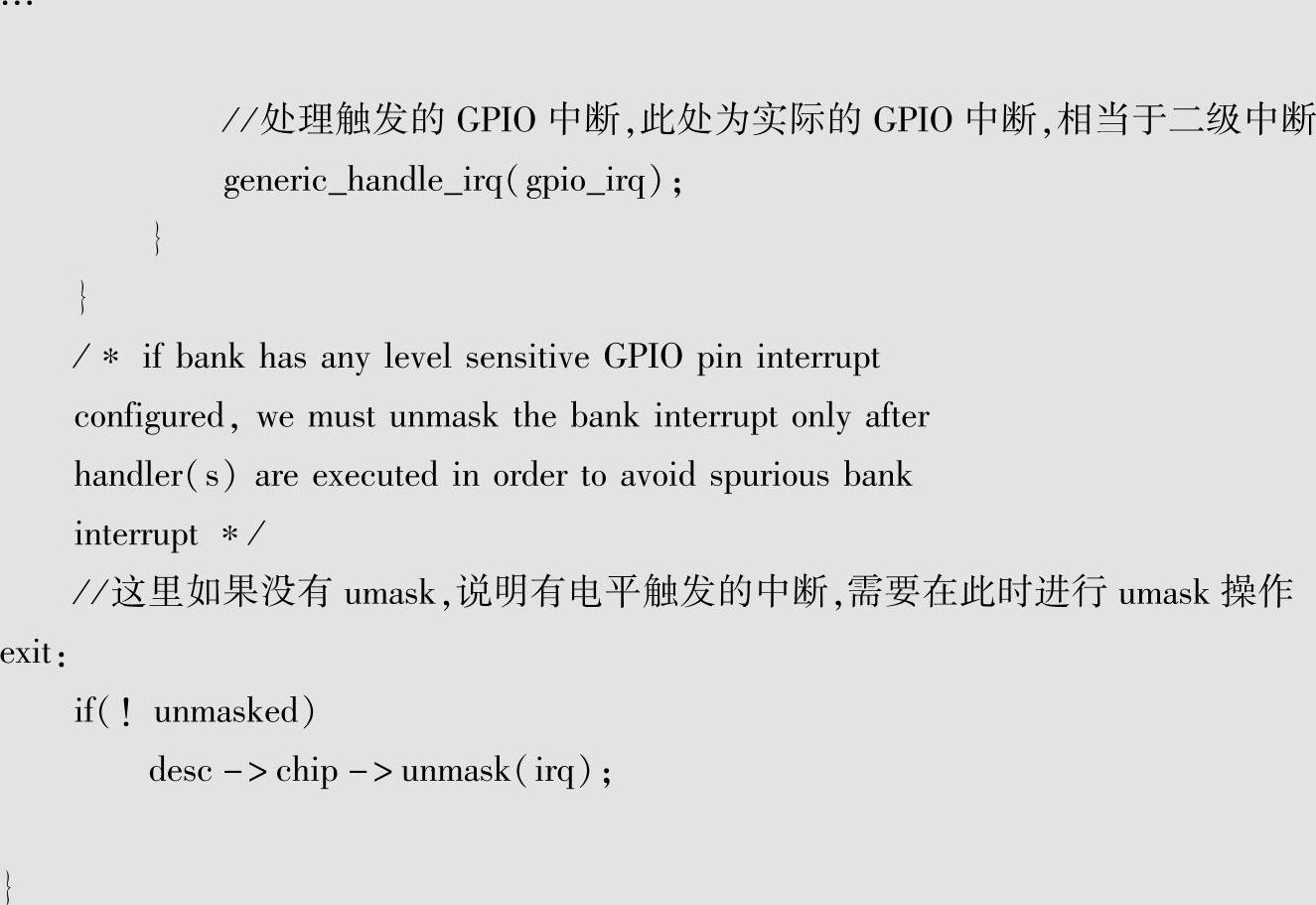

3ᤫGPIO中断相关实现

GPIO中断相关的实现,最主要的是中断控制器相关的接口实现以及中断级联中GPIO组的中断处理函数。

先来看看GPIO的中断控制器相关接口。这里实际实现了级联的中断处理。

该中断控制器负责一组GPIO的中断处理,详细的接口代码分析如下:

从中可见,GPIO不仅有基本的中断操作,还有唤醒系统的能力,所以提供了中断控制器中set_wake的接口(该接口是老的接口,但是可以通过新的接口irq_set_wake转换调用,内核中断处理框架irq_chip_set_defaults会建立这种转换)。

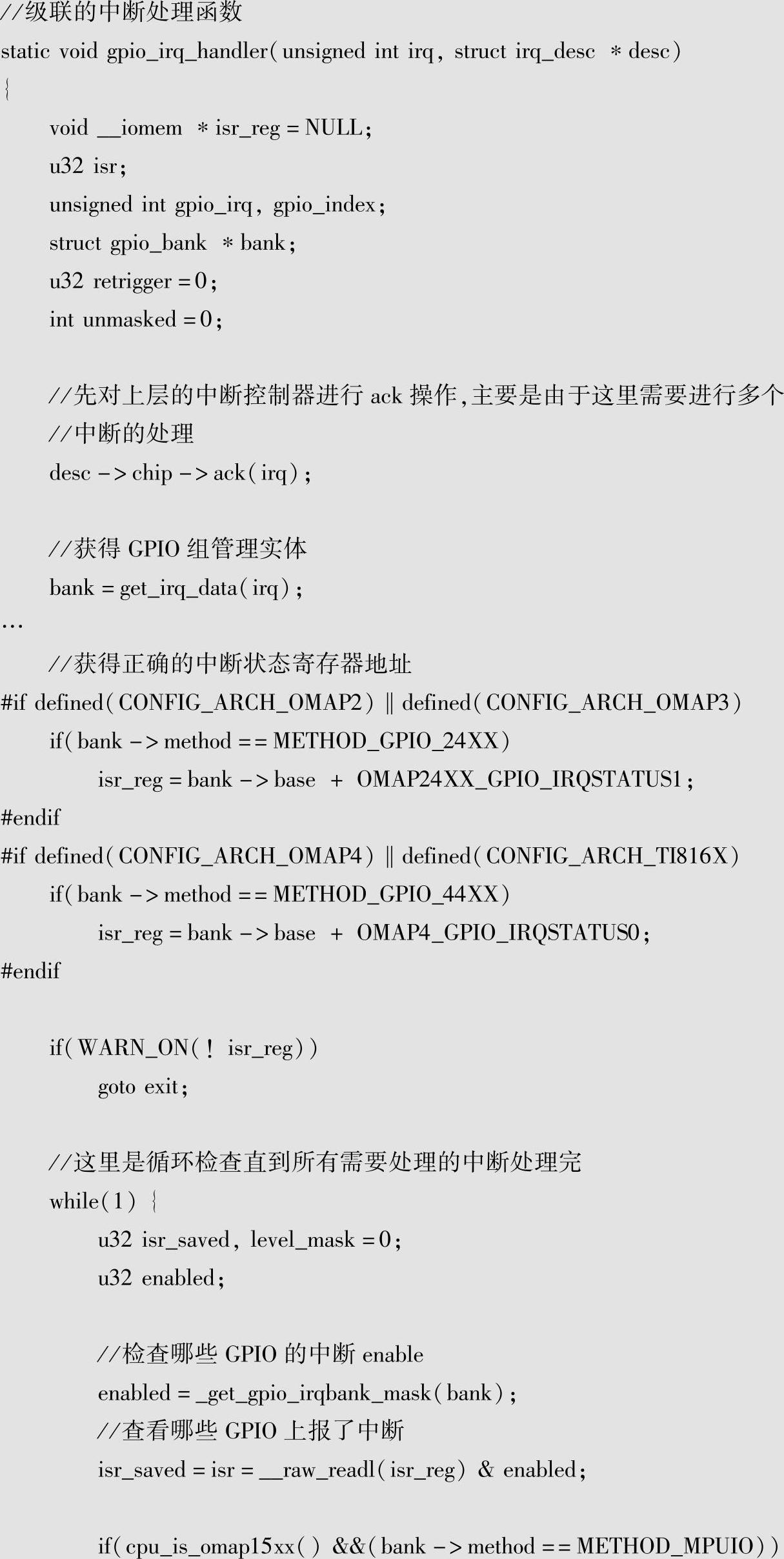

接下来解析一下级联的中断处理,由于ARM无法获得一组GPIO中具体哪个GPIO上报的中断,所以需要通过该级联中断处理,进行具体的解析并需要对具体的GPIO中断进行处理。

至此,关于GPIO的中断部分主要框架就分析完了。中断处理还要注意电平触发和边沿触发的流程是不同的,这些都要体现在级联的中断处理中。

(https://www.chuimin.cn)

(https://www.chuimin.cn)

相关推荐