要了解具体芯片的DMA使用和管理,首先要看一下硬件的设计。图4-44DM 3730 SDMA与其他模块联系系统框图从图4-44可见,SDMA共有96个DMA请求,用于设备请求DMA进行数据传输处理。SDMA可以访问到外设并可以响应芯片外部的DMA请求。为了提高整个的DMA性能,DMA提供多个中断信号给处理器,来加速系统对DMA处理数据过程的响应。DMA是很多驱动都需要使用的基础功能之一,以上进行了详细的代码级分析。......

2023-11-22

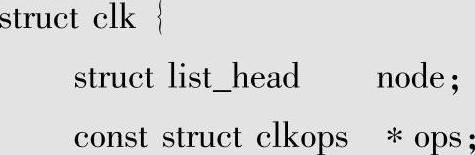

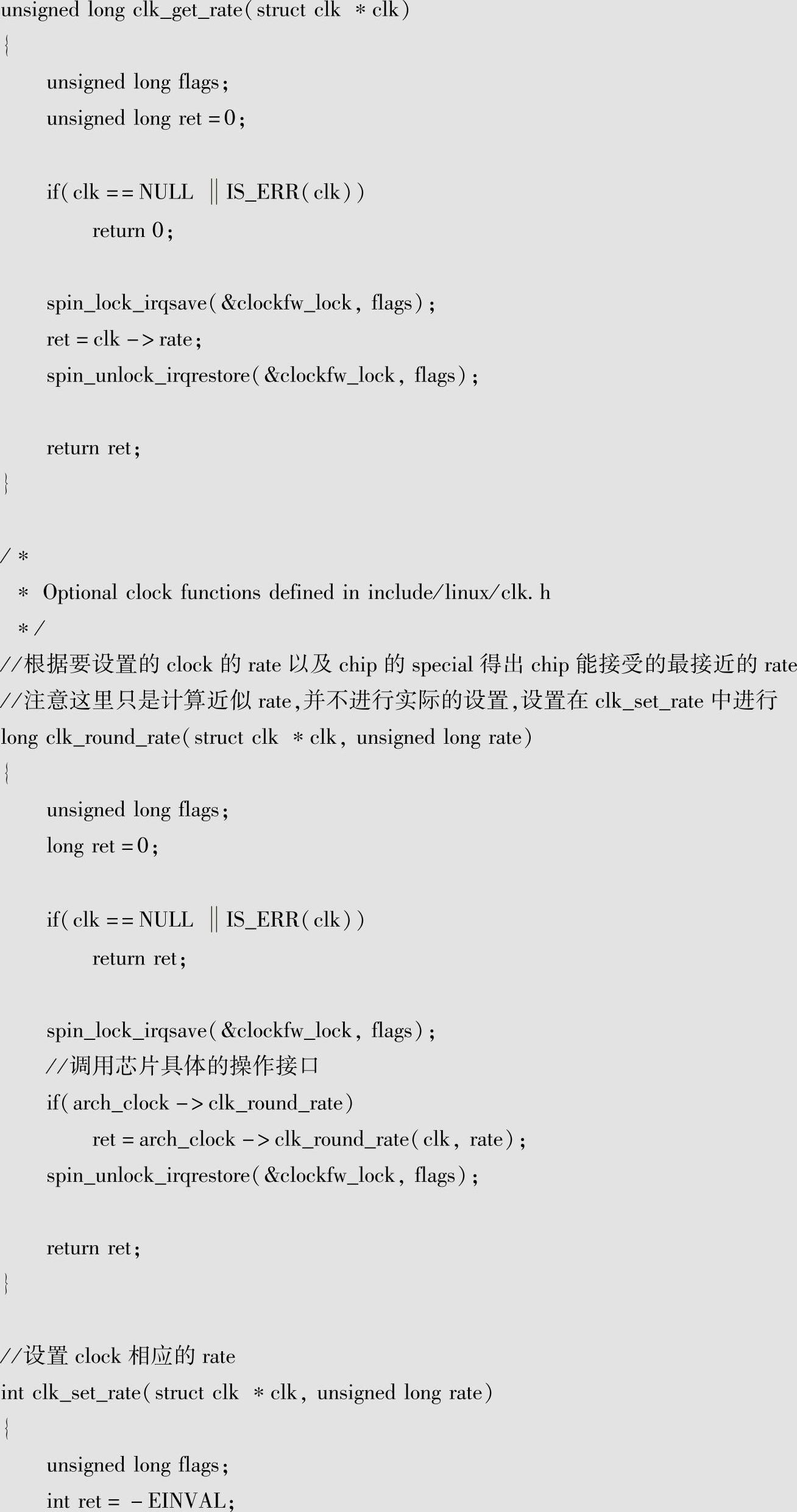

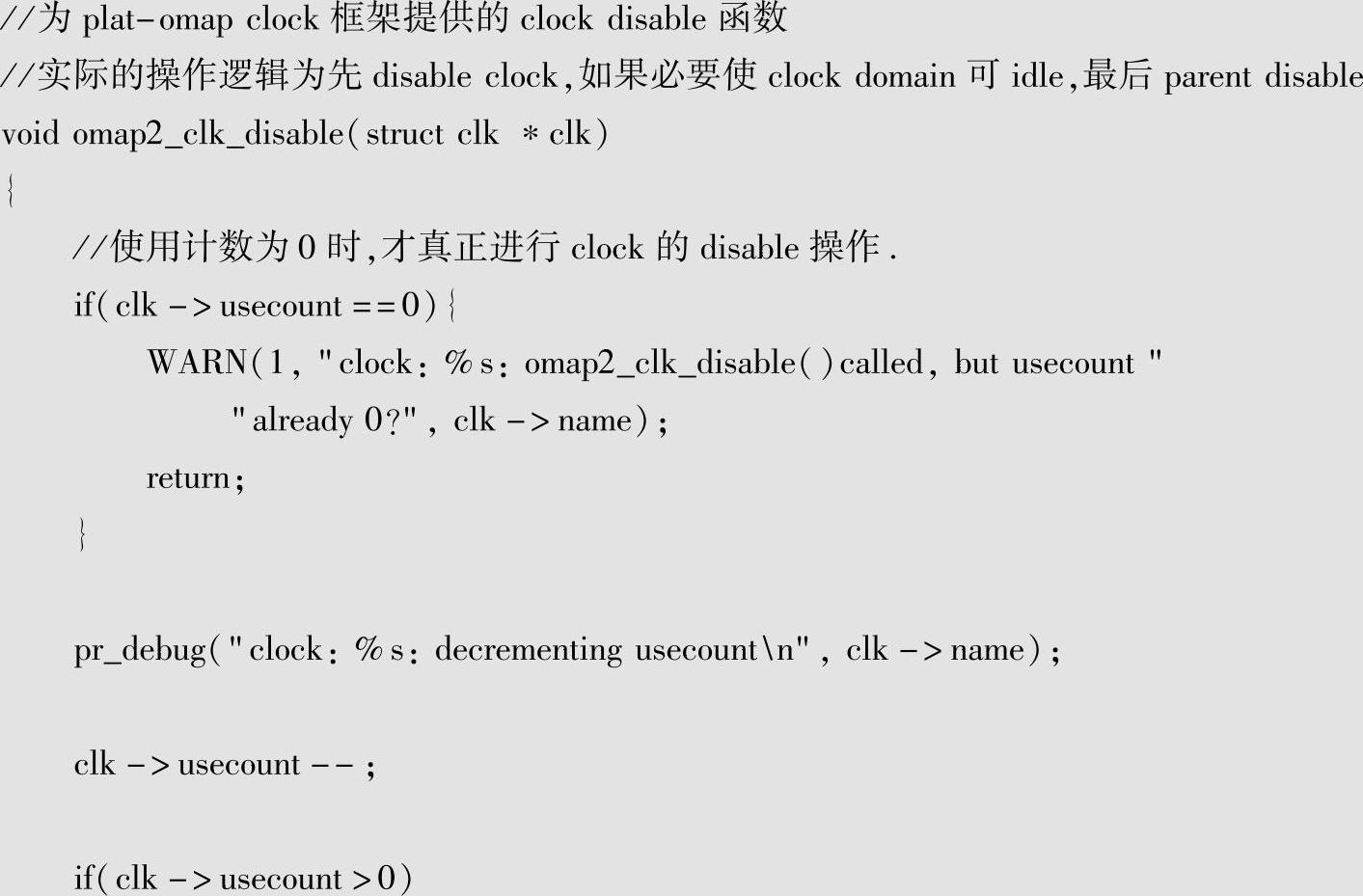

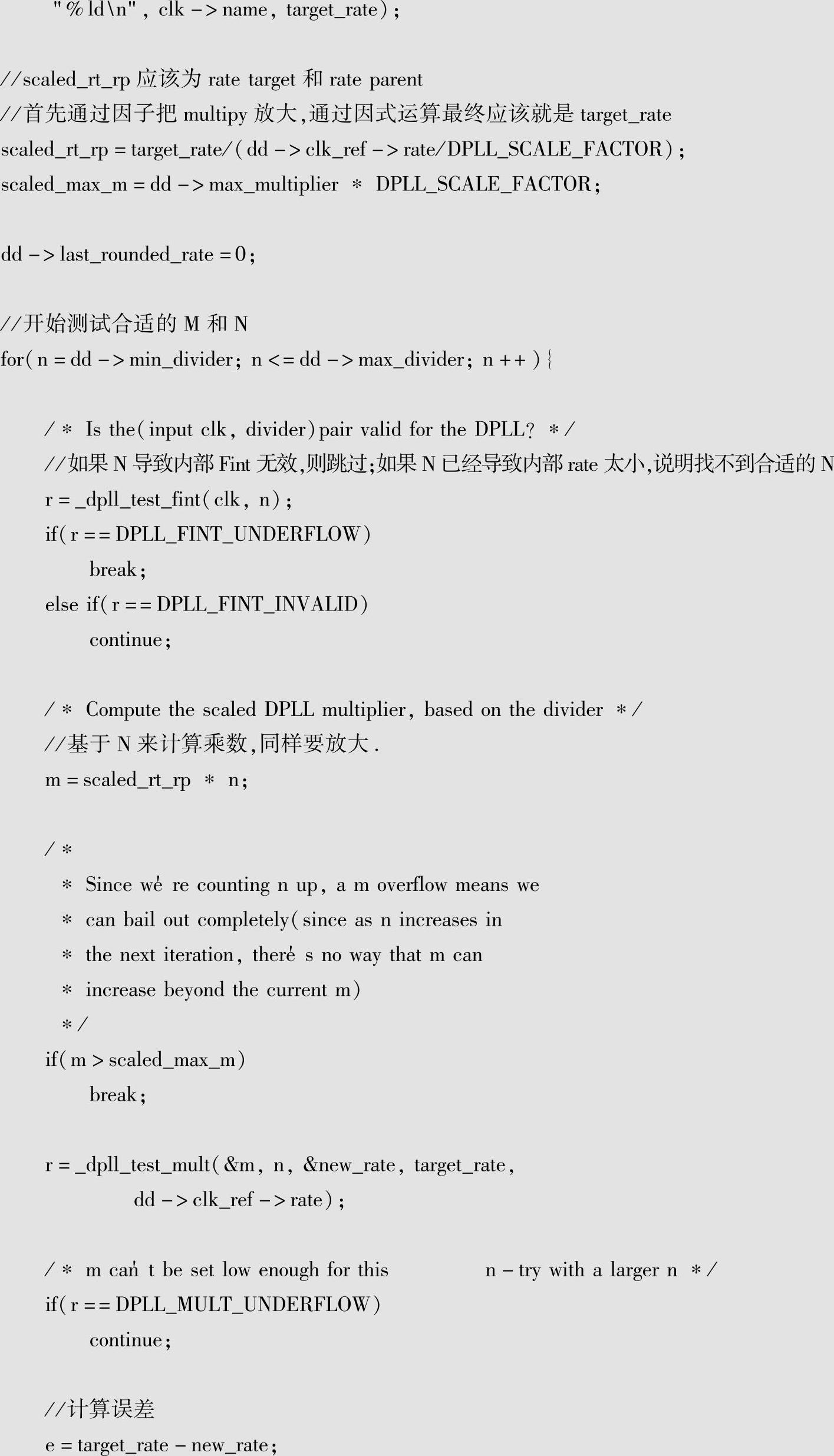

TI芯片(包括DM 3730和DM 816X)时钟管理框架的实现也是分层次的。在上层实现了Linux内核提供的接口函数作为抽象层,供其他模块使用;底层则是和芯片相关的具体接口实现。无论哪一层,相应的核心结构都是struct clk,该结构在arch/arm/plat-omap/in-clude/plat/clock.h中定义,具体内容如下:

其中包括了和树状管理相关的属性parent、children和sibling;使用计数的属性usec-ount;操作接口;以及特定时钟类型相关的属性,如clksel、dpll_data等。这里包含了完整的信息。时钟管理的具体实现就是围绕着该数据结构展开的。

下面按照层次来介绍时钟管理。

1ᤫ抽象层实现

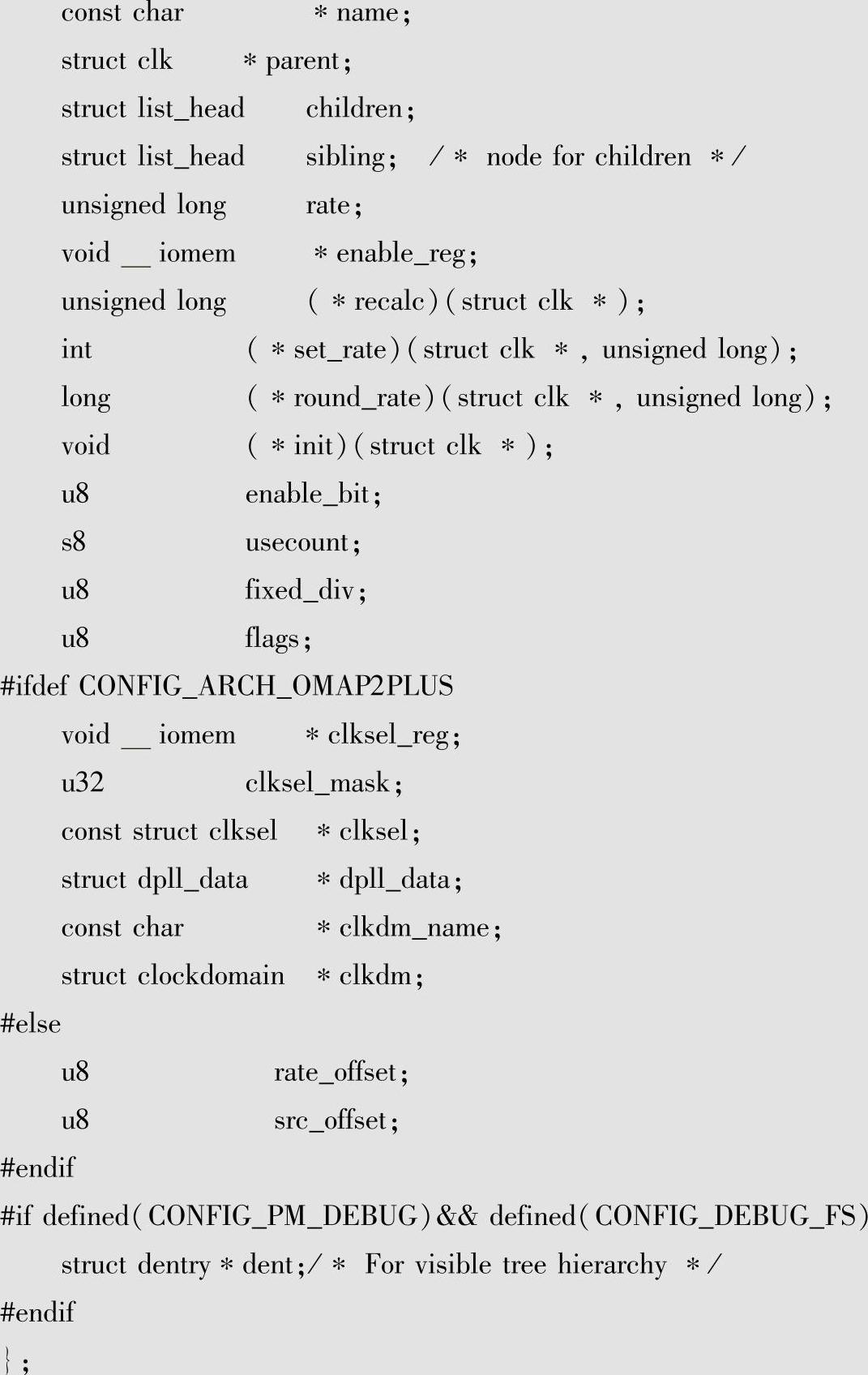

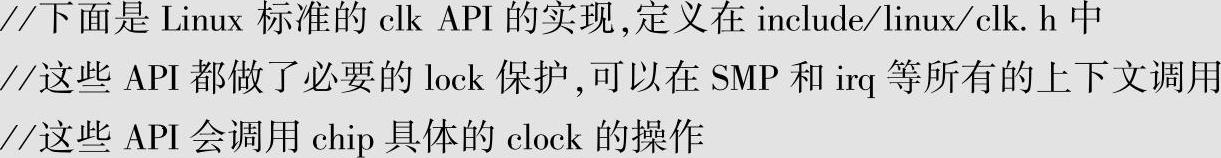

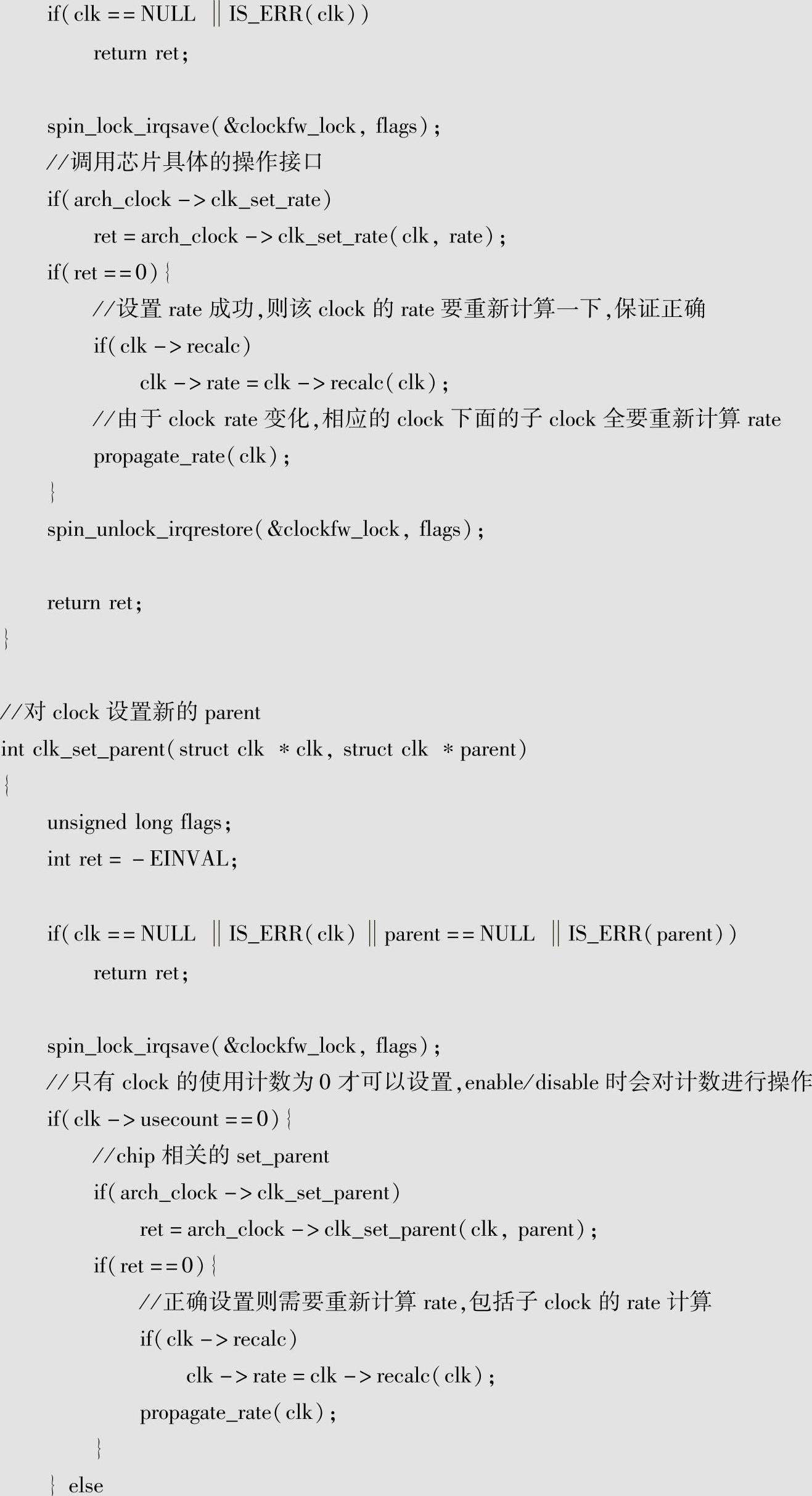

相应的抽象实现是在linux/arch/arm/plat-omap/clock.c文件中,具体实现了Linux内核中规定的一些接口,代码分析如下:

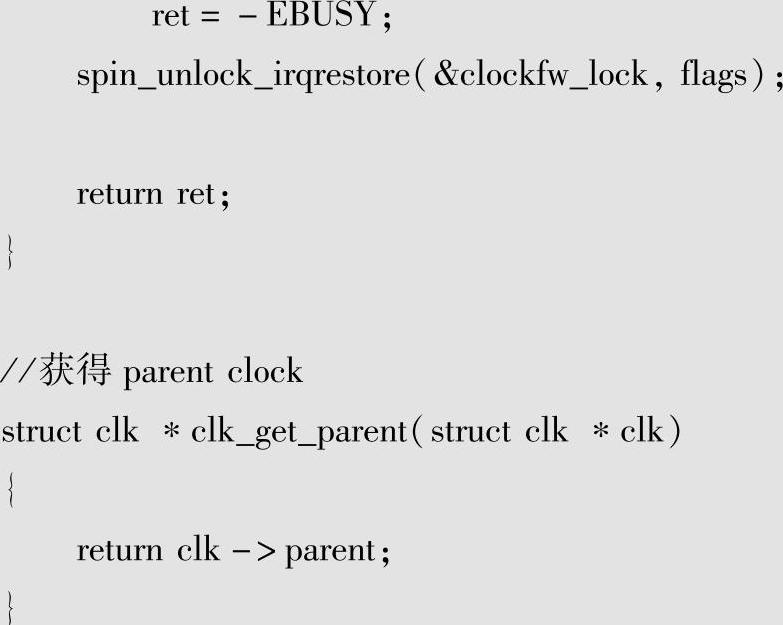

2ᤫ芯片时钟接口具体实现

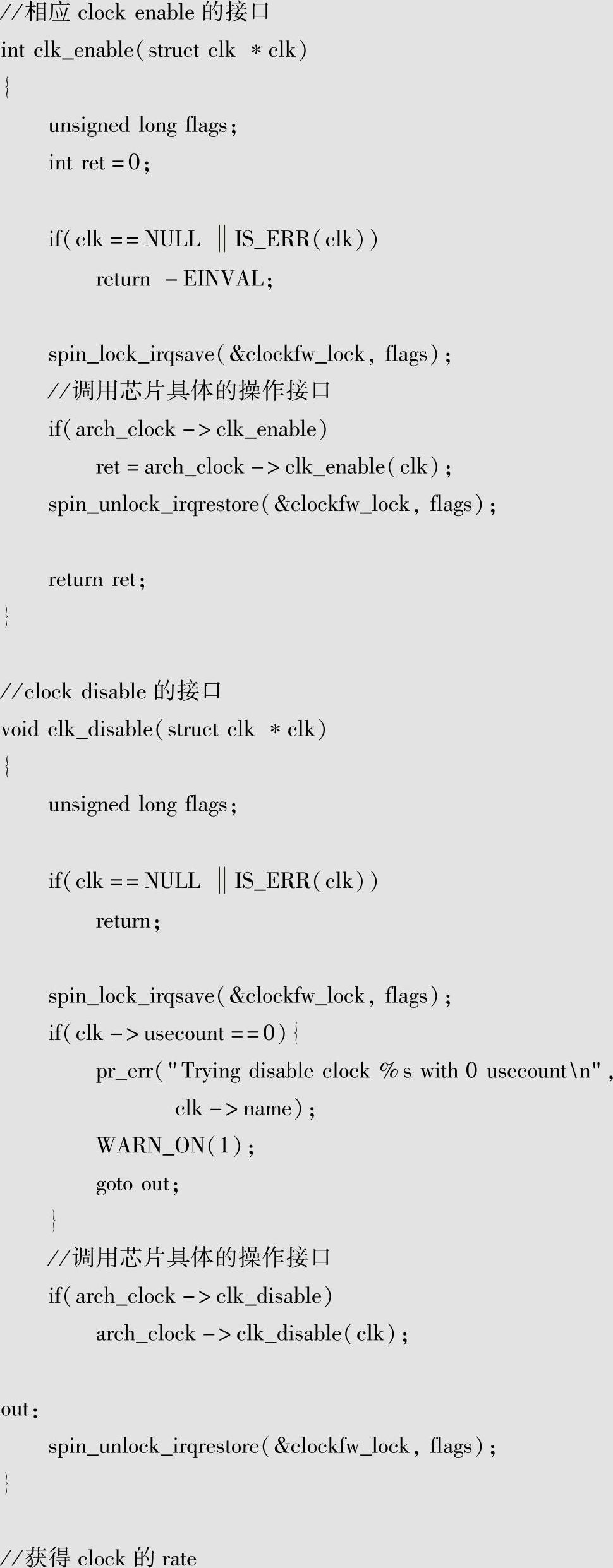

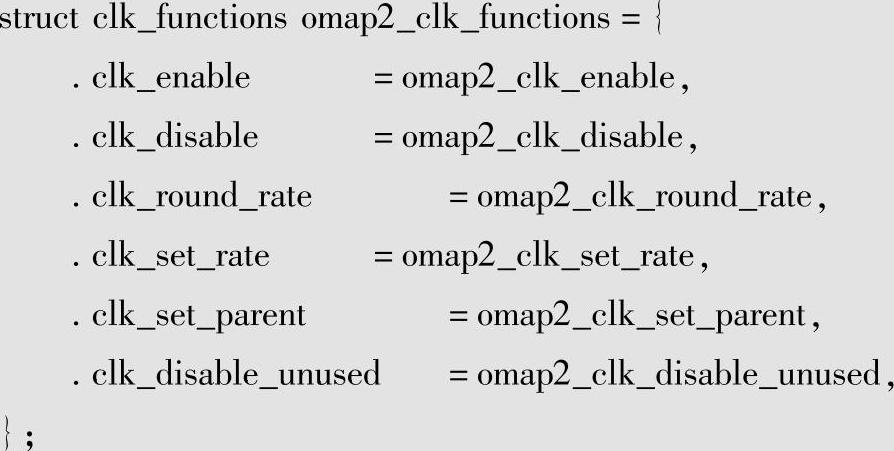

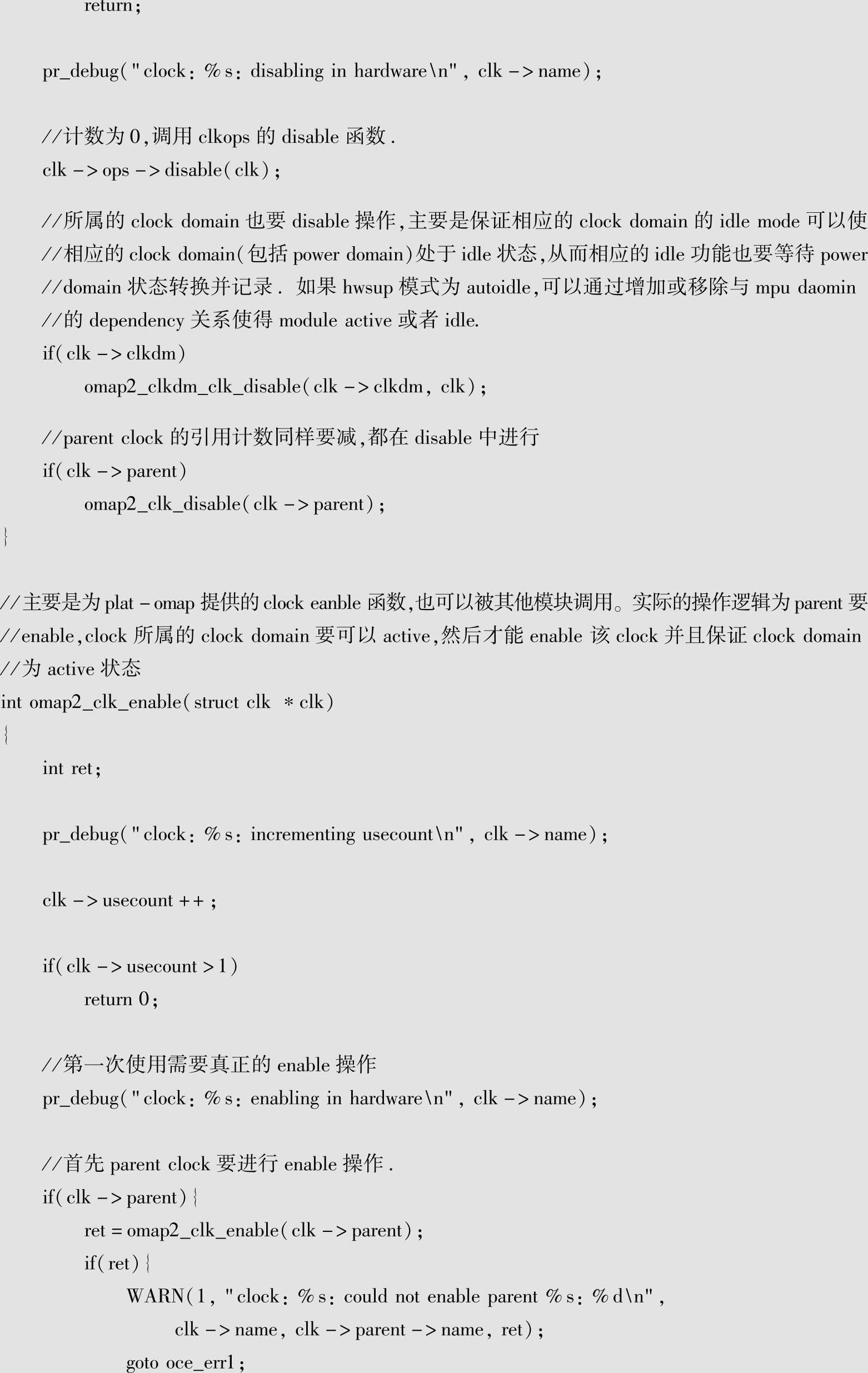

在抽象层看到很多接口都是调用芯片的具体实现来执行的,DM 3730和DM 816X相关的具体实现是在mach-omap2/clock.c中,操作接口综合成clk_functions。

相应的接口实现详细分析如下:

从代码中可见,对clock的操作中还要设置上层的clock domain,这符合芯片的电源管理设计框架。

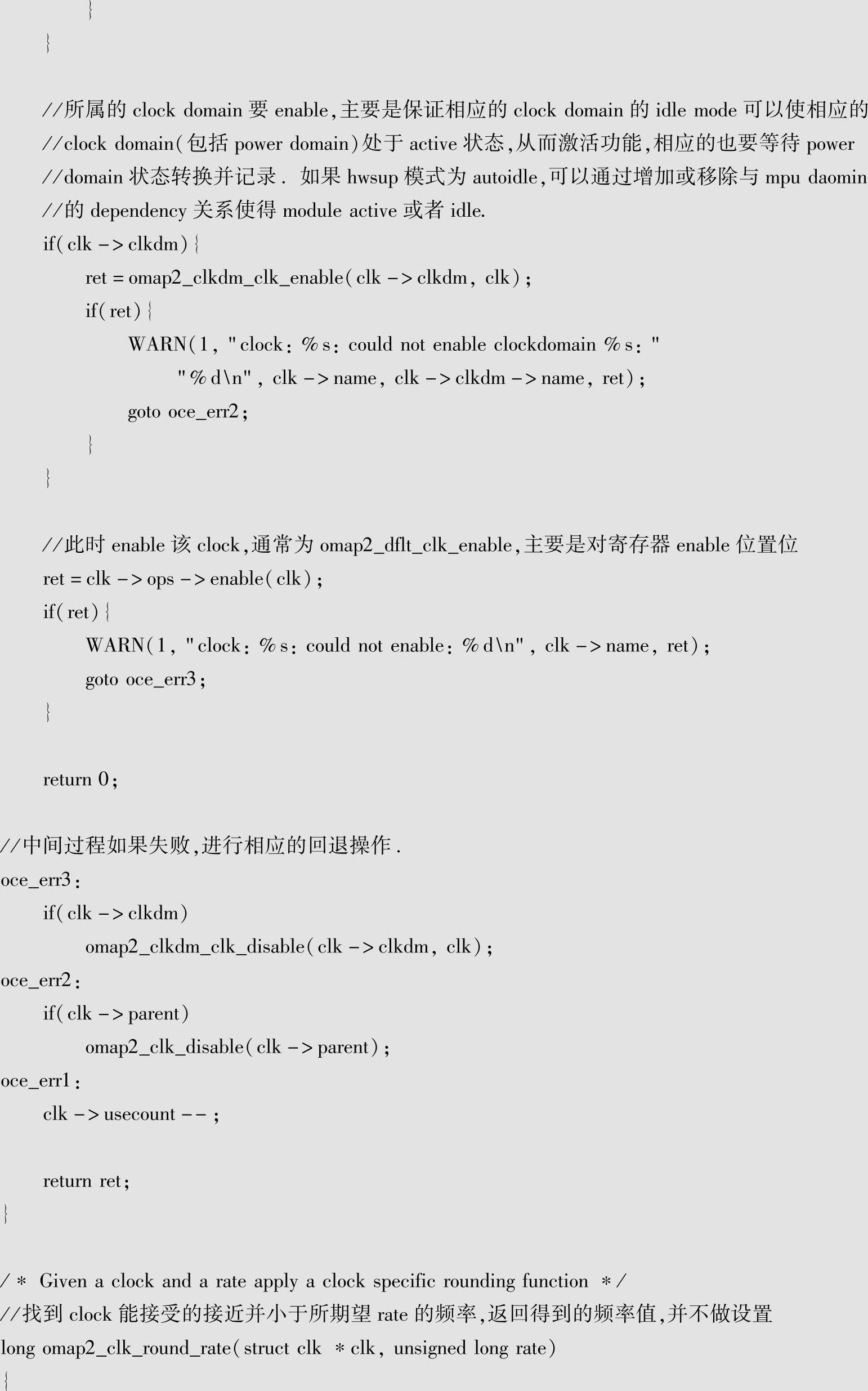

3ᤫ不同时钟类型的具体实现

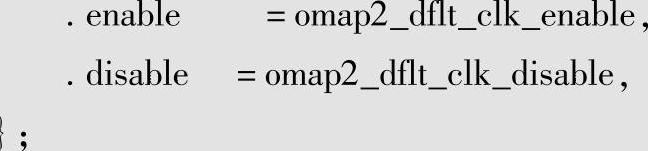

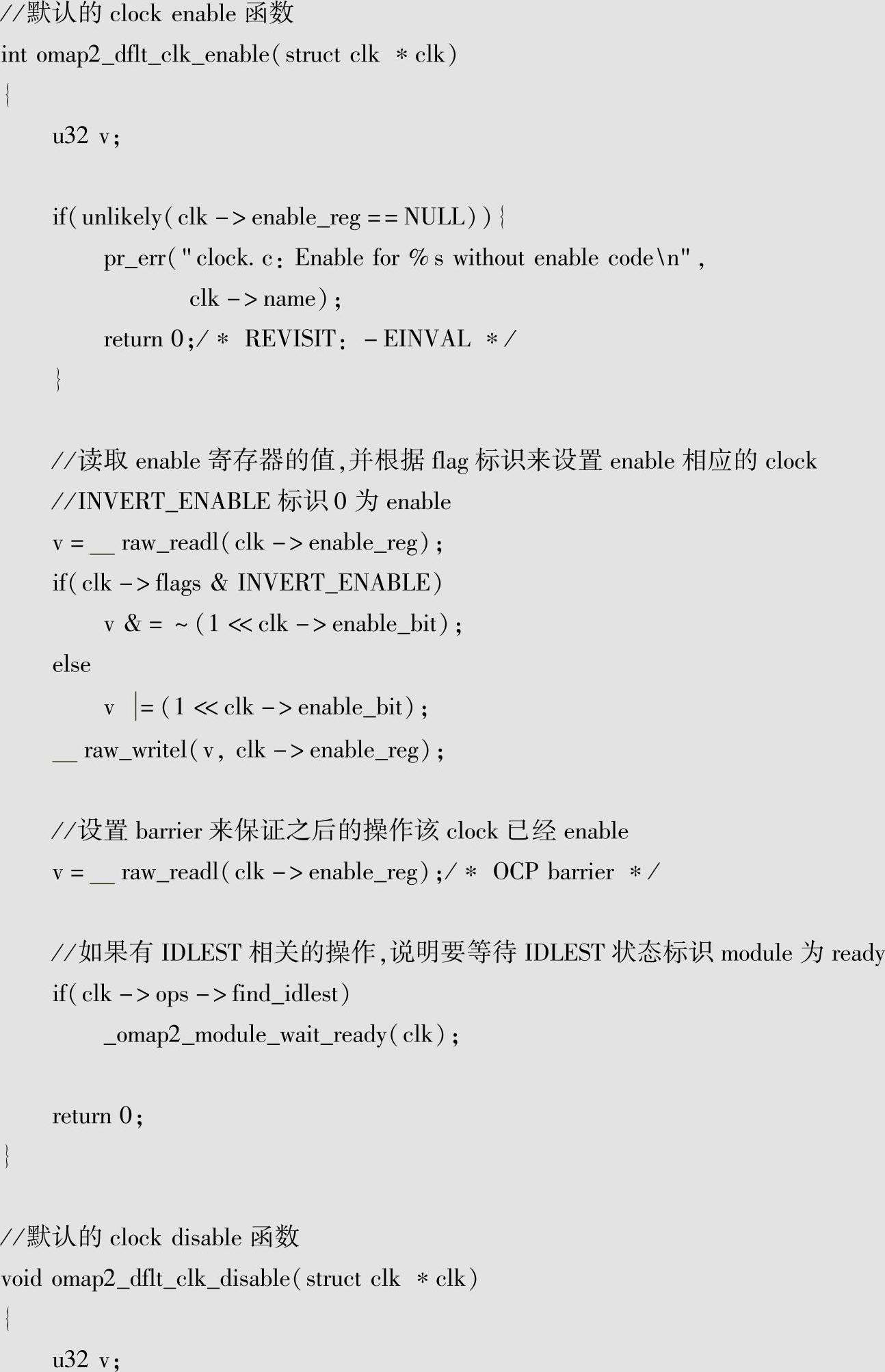

由之前的代码和struct clk中可见,操作接口有两种,一种是在struct clkops中表示的,另外一种是直接在struct clk中的,如set_rate等。这是为什么呢?仔细看struct clkops中的操作接口是和时钟enable和disable相关的,而struct clk中的操作接口是和频率设定相关的。把它们分开是因为这是两种完全不同的操作类型。对enable和disable相关的操作单独管理是由于很多模块会有不止一种时钟,通常会有接口时钟和功能时钟,而设备要能使用,需要在enable某种时钟时伴随着enable相应的伙伴时钟;或者某些时钟是由模块对外产生的,在enable时需要等待相应的模块到某种状态时才是真正的enable,只有等待到相应的状态时相关的操作才完整。而对时钟频率的操作则相对直接,只要根据不同的时钟类型进行正确的操作即可。

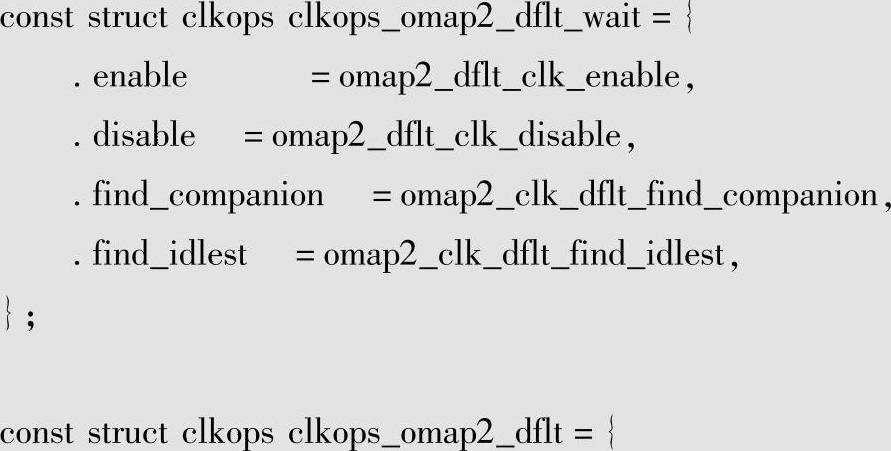

DM 3730提供了几类enable和disable的操作接口,具体如下:

(www.chuimin.cn)

(www.chuimin.cn)

可见主要的接口是enable和disable。下面来进行详细分析,在分析之前先进行说明,相应的接口主要操作的寄存器是功能时钟使能FCLKEN、接口时钟使能ICLKEN和状态检查IDLEST等寄存器。

针对时钟频率的操作,则要考虑两种类型的时钟,分别是通过寄存器选择的clock和dpll clock,这两种类型的时钟对应频率的操作是完全不同的。

先看看通过寄存器选择的时钟相关的操作接口实现:

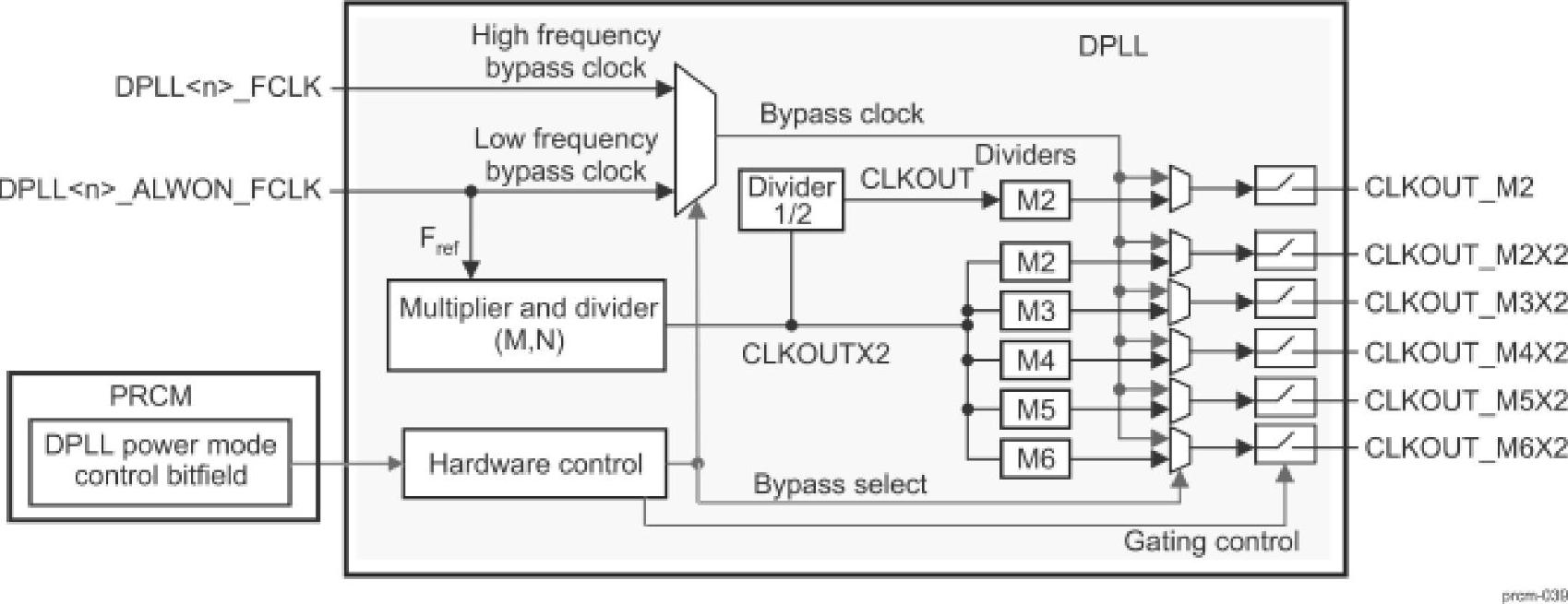

DPLL锁相环时钟会和芯片中究竟采用怎样的锁相环技术相关。DM 3730中使用的DPLL结构如图4-47所示。图4-47引自《DM 3730芯片手册》中第299页框图。

图4-47 DM 3730DPLL结构图

由图4-47可见,DM3730的DPLL主要是设置乘数和除数(M和N),另外DPLL有bypass模式。操作接口分析如下:

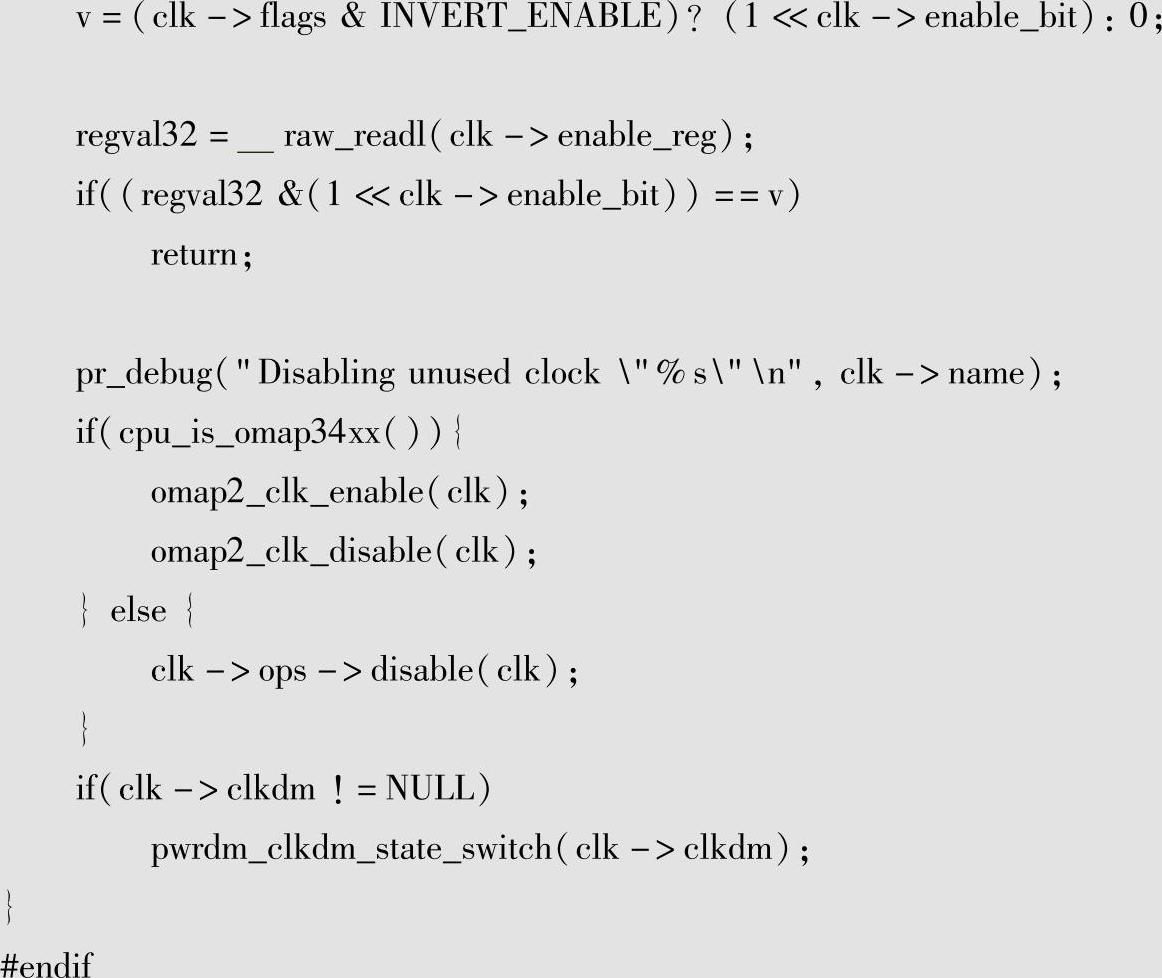

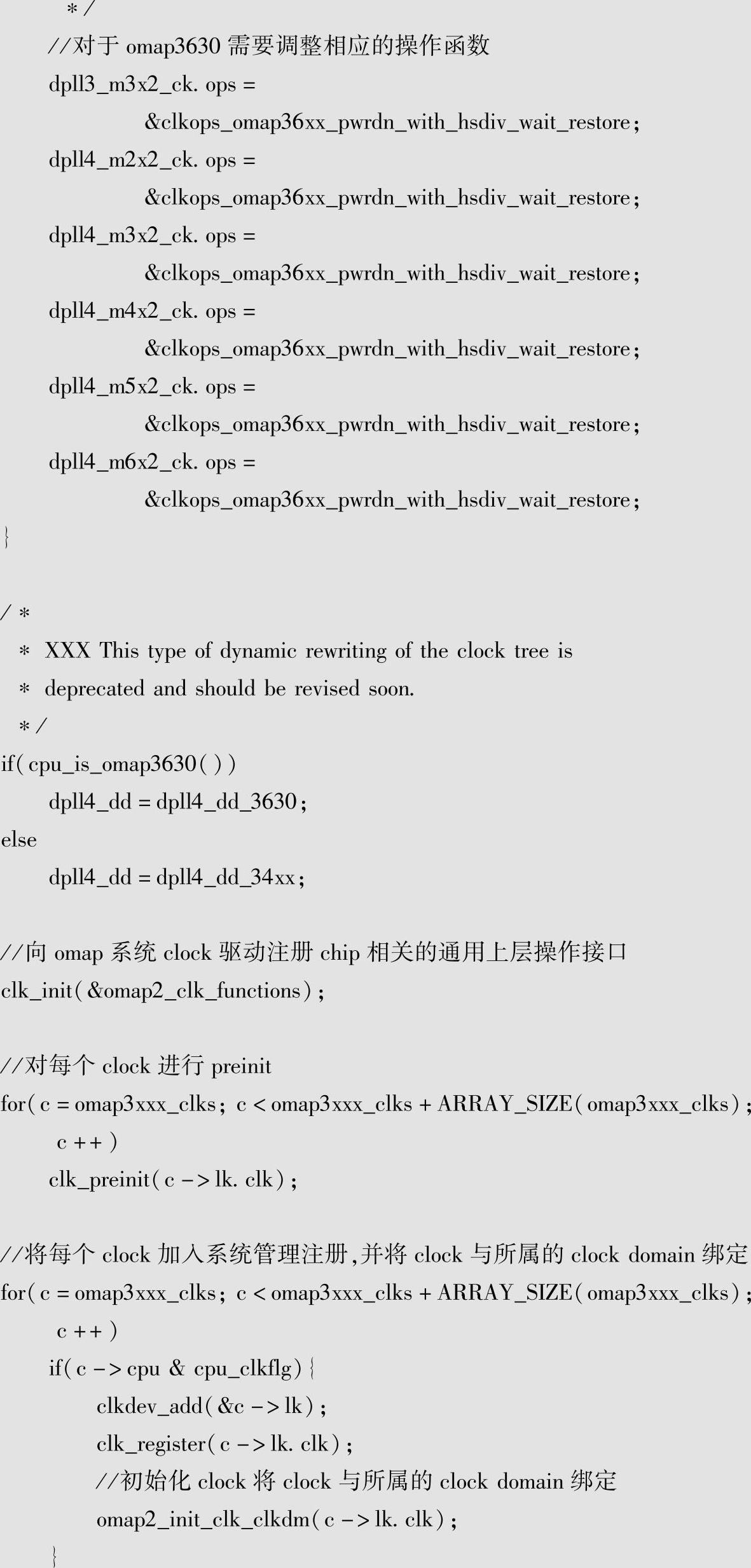

4ᤫ时钟管理初始化

实际的芯片中所有时钟的信息都在clockxxxx_data.c内,DM3730的时钟信息是在clock3xxx_data.c内,其中不仅包含了详细的时钟信息,还包含芯片相关的时钟管理初始化操作。详细分析如下:

注意,该操作是对整个系统的时钟的初始化函数,所以需要在系统初始化比较早的时候进行,对于DM 3730是在板级的中断初始化接口中调用。

至此,关于时钟管理的框架和主要接口分析完毕。

有关深入剖析Linux内核与设备驱动的文章

要了解具体芯片的DMA使用和管理,首先要看一下硬件的设计。图4-44DM 3730 SDMA与其他模块联系系统框图从图4-44可见,SDMA共有96个DMA请求,用于设备请求DMA进行数据传输处理。SDMA可以访问到外设并可以响应芯片外部的DMA请求。为了提高整个的DMA性能,DMA提供多个中断信号给处理器,来加速系统对DMA处理数据过程的响应。DMA是很多驱动都需要使用的基础功能之一,以上进行了详细的代码级分析。......

2023-11-22

DM 3730的MMC控制器框架如图7-11所示。图7-11DM 3730 MMC框架图从图7-11可见,MMC控制器中有复杂的命令和数据管理,控制器内部带有buffer用于数据缓冲,数据主要通过DMA读写。关于DM 3730 MMC的驱动部分,主要分析其相关的初始化和总线传输以及card状态变化的操作。......

2023-11-22

对DM 3730的开发板,相关的输入设备是电源管理芯片中的键盘矩阵,这里对相关的输入设备驱动进行分析。在硬件介绍中已经见到DM 3730与电源管理芯片是通过I2C总线进行连接的,所以该键盘驱动需要建立在I2C总线操作之上。具体获得相关信息的方法都是通过类似twl4030_read_kp_matrix_state的操作完成的,其中会进行实际的I2C总线操作,具体的细节会在总线部分进行介绍。在驱动获得硬件的信息后就是向输入设备框架汇报相应的事件,框架会上传给even than-dler,最终被用户读取。......

2023-11-22

SoC电源管理框架与SoC的设计息息相关。platform总线相关的电源管理功能已经在设备模型部分进行了介绍。接下来主要以DM 3730为例对TI芯片SoC电源管理实现进行介绍。从图8-1可见,DM 3730 SoC电源管理的核心是omap_device,其中包含了platform_de-vice和hwmod,platform_device部分包含了与platform bus相关的部分,而hwmod包含了DM3730中各个控制器的硬件信息。......

2023-11-22

接下来分步说明中断处理的具体实现。Linux内核irqdesc.h中有如下定义:这里可见宏NR_IRQS描述了所有中断的个数,这个数目应该是和处理器相关的。具体的级联中断的解决办法留到相应模块中进行详细说明。3中断控制器的处理接下来看看DM 3730的内核是如何实现中断控制器的管理的。图4-30引自《DM 3730芯片手册》中第2411页的框图。电源管理没有中断控制器唤醒的相关实现,由于这部分是在ARM主处理器的电源域中,并不需要这部分功能。......

2023-11-22

下面以4.1.1节所介绍的系统初始化流程为例,来看看不同的处理器启动流程的区别。图4-4和图4-5分别是DM 816X和DM 3730的启动流程。其中原因是芯片内部片内内存大小。接下来以TI芯片为基础进行整个系统的初始化过程详解。之前讨论内核初始化需求的时候,提到初始化代码应该在初始化之后释放相应的内存空间,这里可以看出Linux内核已经将初始化相关的代码统一存放并管理,一方面方便初始化时调用,另一方面可以在系统初始化之后将这部分空间释放。......

2023-11-22

1芯片片内内存使用TI芯片相关的内存管理,对片外内存来说,可以通过启动参数将需要内核管理的内存进行设置。这样做的原因是由于需要连续的物理内存空间,并且对内核的物理内存管理影响最小。3独立cmem管理之前简单说明芯片厂商的独立内存管理,针对于TI的视频芯片,TI提供了cmem的内存管理驱动,主要是连续内存管理。有了该内存管理功能,TI的多媒体框架和编解码库就可以使用连续的物理内存空间,高效地完成多媒体处理相关的功能。......

2023-11-22

相关推荐