【摘要】:TI为DM 3730设计了一系列电源管理芯片如TPS 65950等,这样使用DM3730再加上TPS 65950的配合就能够达到很好的待机功耗,TI的参考设计中也是这么实现的。

1.DM 3730使用的电源管理技术介绍

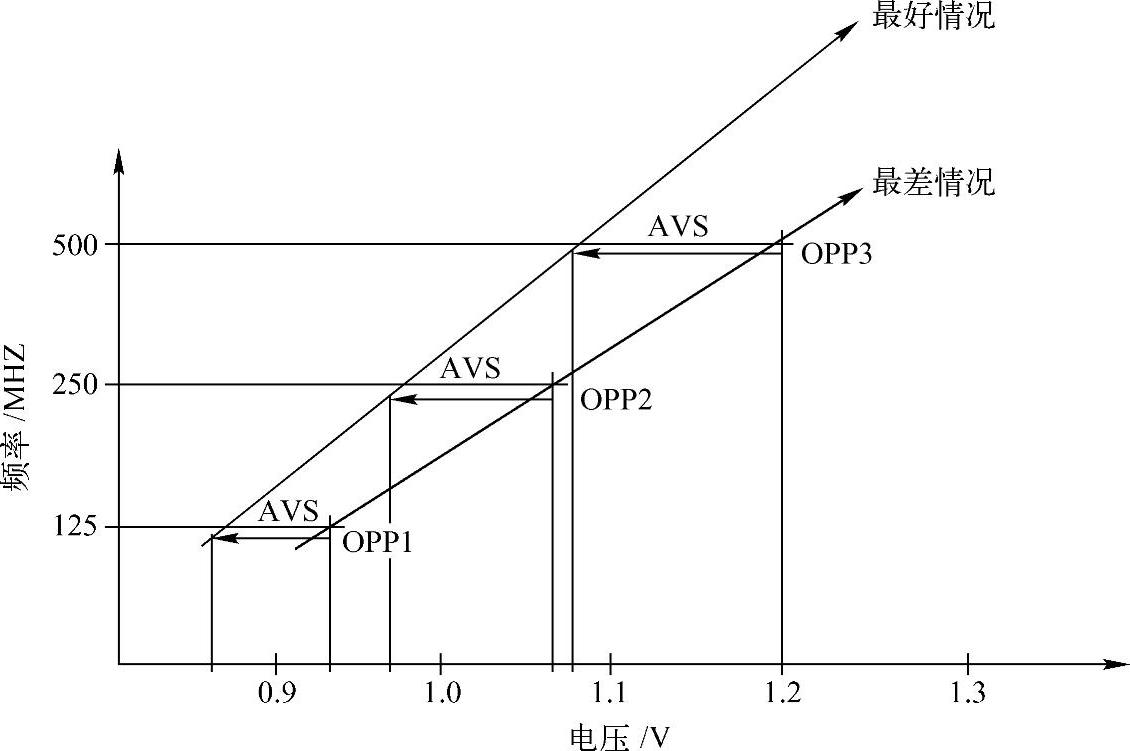

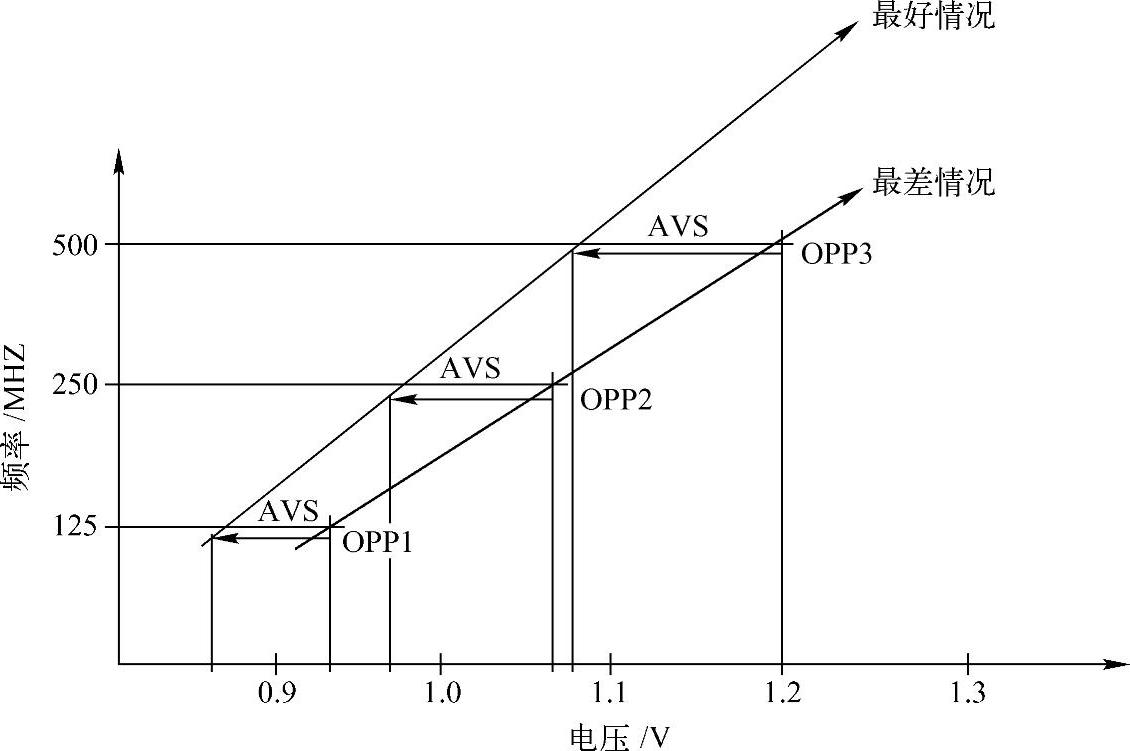

电源管理的相关技术都是以第1章讨论过的公式P=CV2F为原理出发的。DM 3730中使用了两个比较重要的电源管理技术DVFS(动态电压/频率调整)和AVS(电压适配调整)。先看看DVFS,从公式出发可以知道降低频率就可以降低功耗,然而直接降低频率对相同工作量的任务就需要更多的时间完成,如此看来并没有起到降低功耗的作用,执行时间变长了,用户体验也不好。从公式出发看看降低电压的效果,由于降低电压对芯片工作稳定性会有影响,所以一般在降低电压的同时是要降低频率的,这样一来完成相同的任务也会消耗更多的时间,所以降低电压会是一个连锁反应,但是从公式可以看到电压对功耗的影响是V2,可见电压影响更大。举个例子电压为1V时执行1s的任务如果消耗1J的能量,那么主频降为原来的一半时所需要的电压大概是0.7V,这样同样的任务大概需要2s,这样算下来消耗的功耗大概是0.5J,总体算下来降低电压和频率能使功耗大大降低,但是这种功耗的降低的代价就是要用时间来换,DVFS就是在不同的OPP(operating point,操作点)之间调节,每个OPP对应一组电压和频率。既然DVFS是通过时间来换取功耗的降低,那么有没有无代价的降低功耗的技术呢?答案是有的,这就是AVS,AVS从字面adaptive voltage scaling理解是电压适配调整,究竟怎么电压适配呢?图2-2说明了AVS的基本原理,适配这个词突出了芯片的个性和环境的差异,适配实际上就是适配芯片个体情况,对不同芯片的工作电压一定要保证适应最差的情况,如图2-2中OPP1、OPP2和OPP3连成的线,只有使用最差情况的设置才能满足所有芯片的需求。情况好的芯片,如果也要在最差情况的电压下工作,这就会产生功耗的浪费,所以需要适配来降低功能。

图2-2 电压适配调整原理

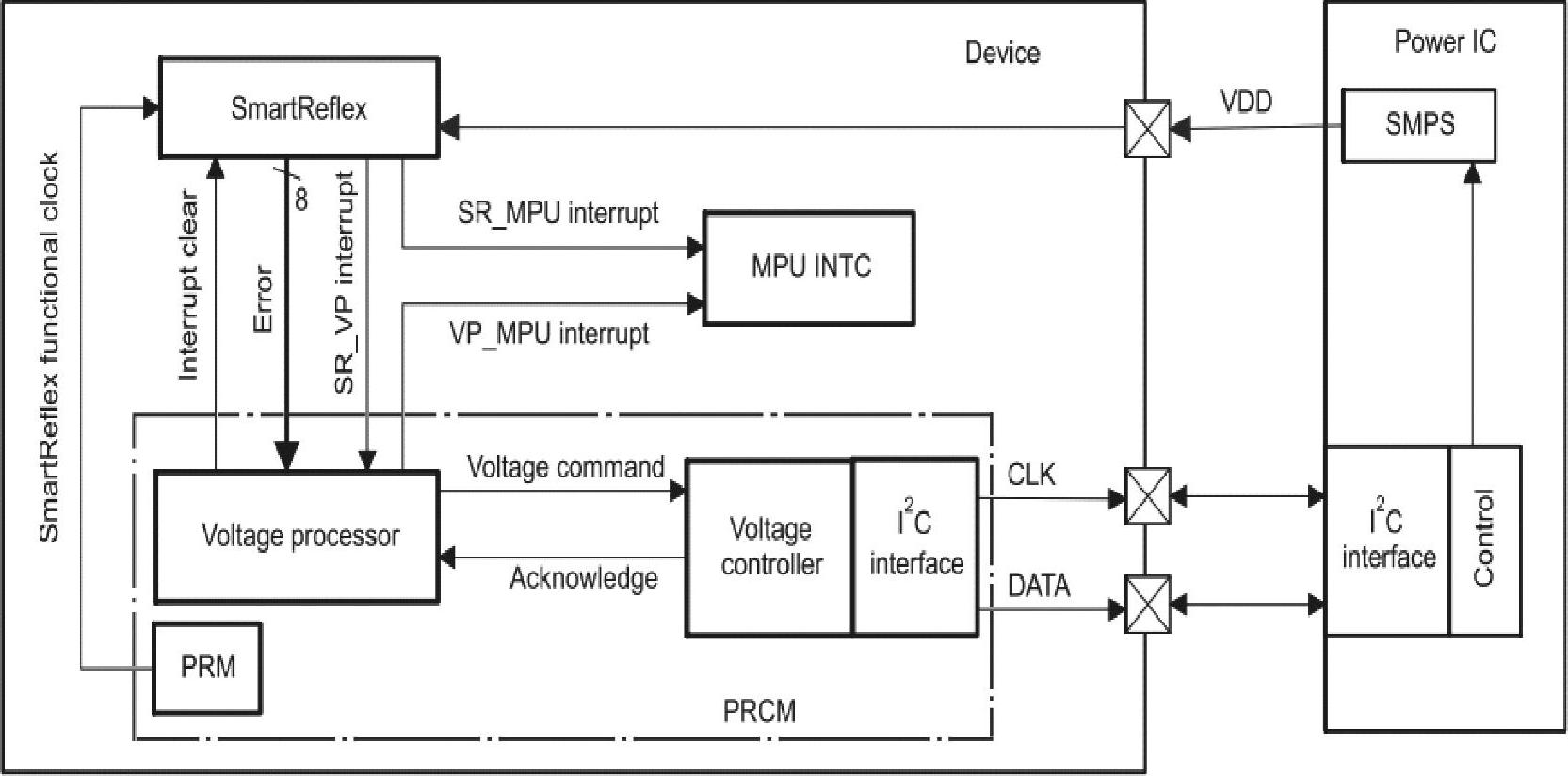

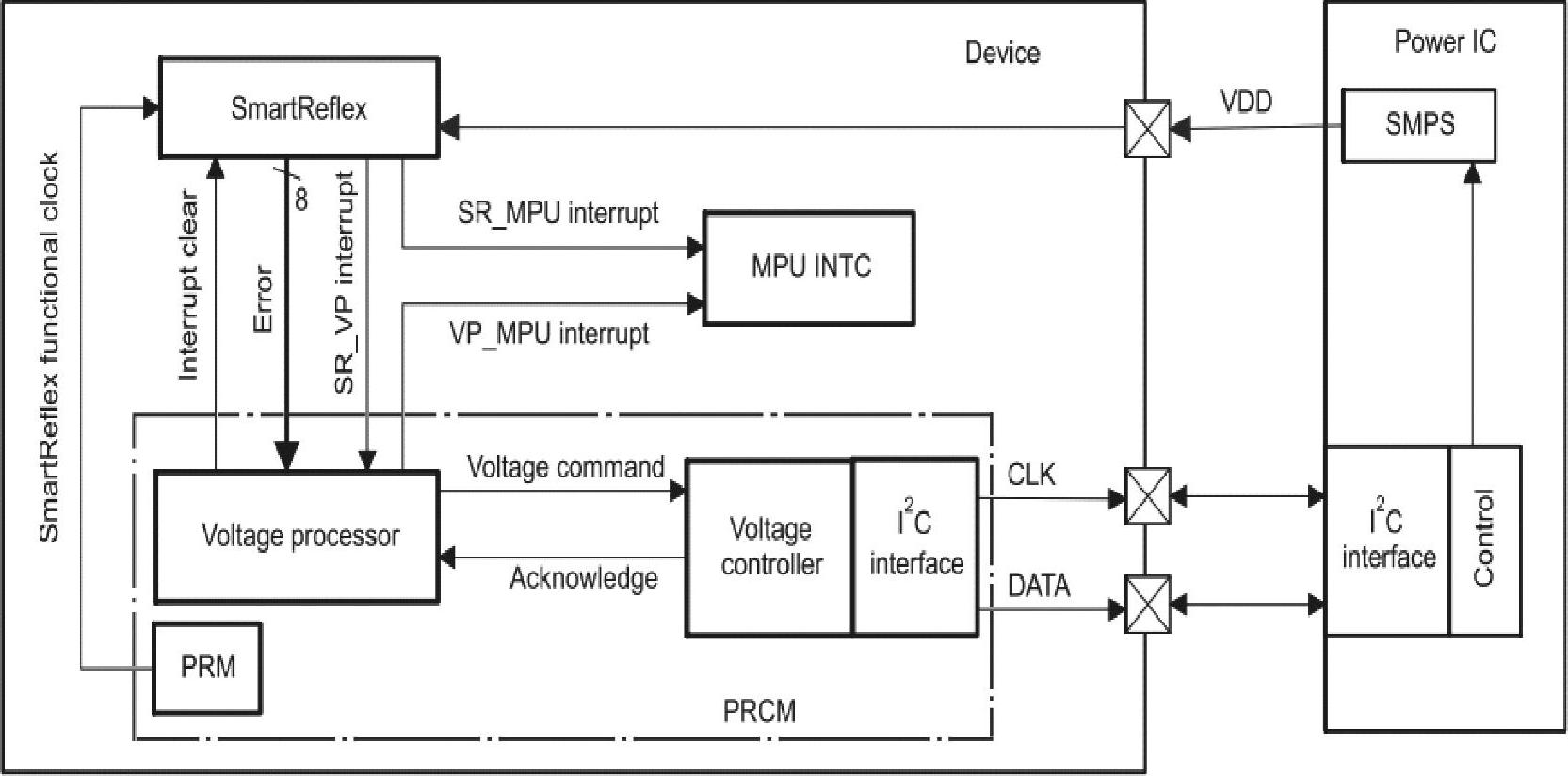

针对AVS的需要,TI设计了Smart Reflex智能反馈电压控制技术,实现框架如图2-3所示。该图引自TI的《DM 3730芯片手册》中第234页框图。

图2-3 Smart Reflex实现框架

从图2-3中可见,有Voltage processor(电压控制器)对当前芯片的个性数据进行计算,然后通过特定的I2C接口和电源管理芯片通信,控制电源管理芯片的电压输出,进而为芯片提供合适的电压。Smart Reflex会通过对输入电压进行检测以及提取芯片自身工作状态的数据为电压控制器提供操作的依据,这样就形成一套完整的反馈系统,合理根据芯片自身的工作情况调整工作电压使功耗最低,从而降低芯片的功耗。

电源管理技术中,DVFS是对电压的大范围的调整,而AVS是针对某个OPP情况下电压小范围的调整,两者完美的结合就能实现功耗最大的优化。

2.DM 3730电源管理模块详解

(1)与电源管理芯片相关的设计

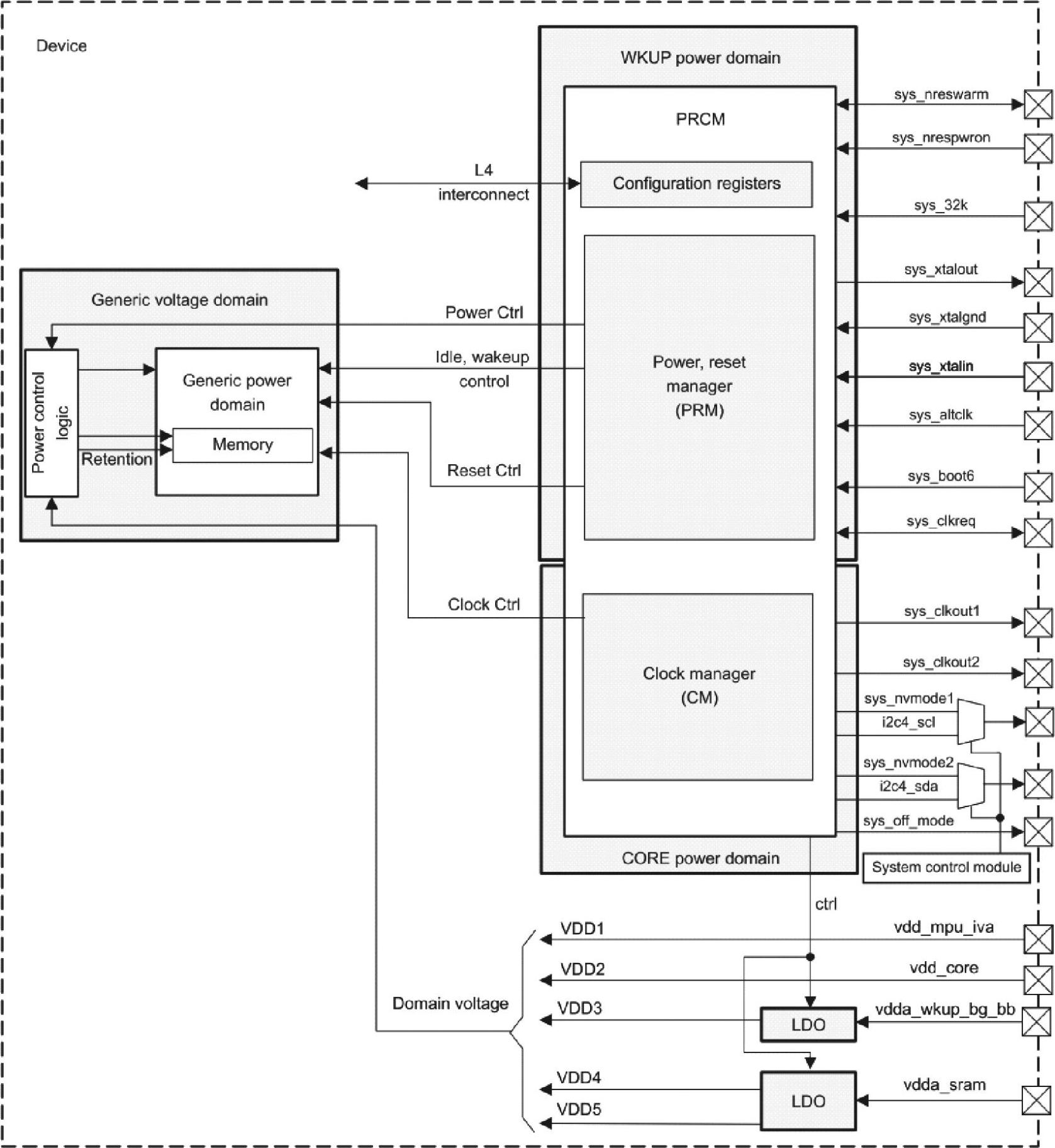

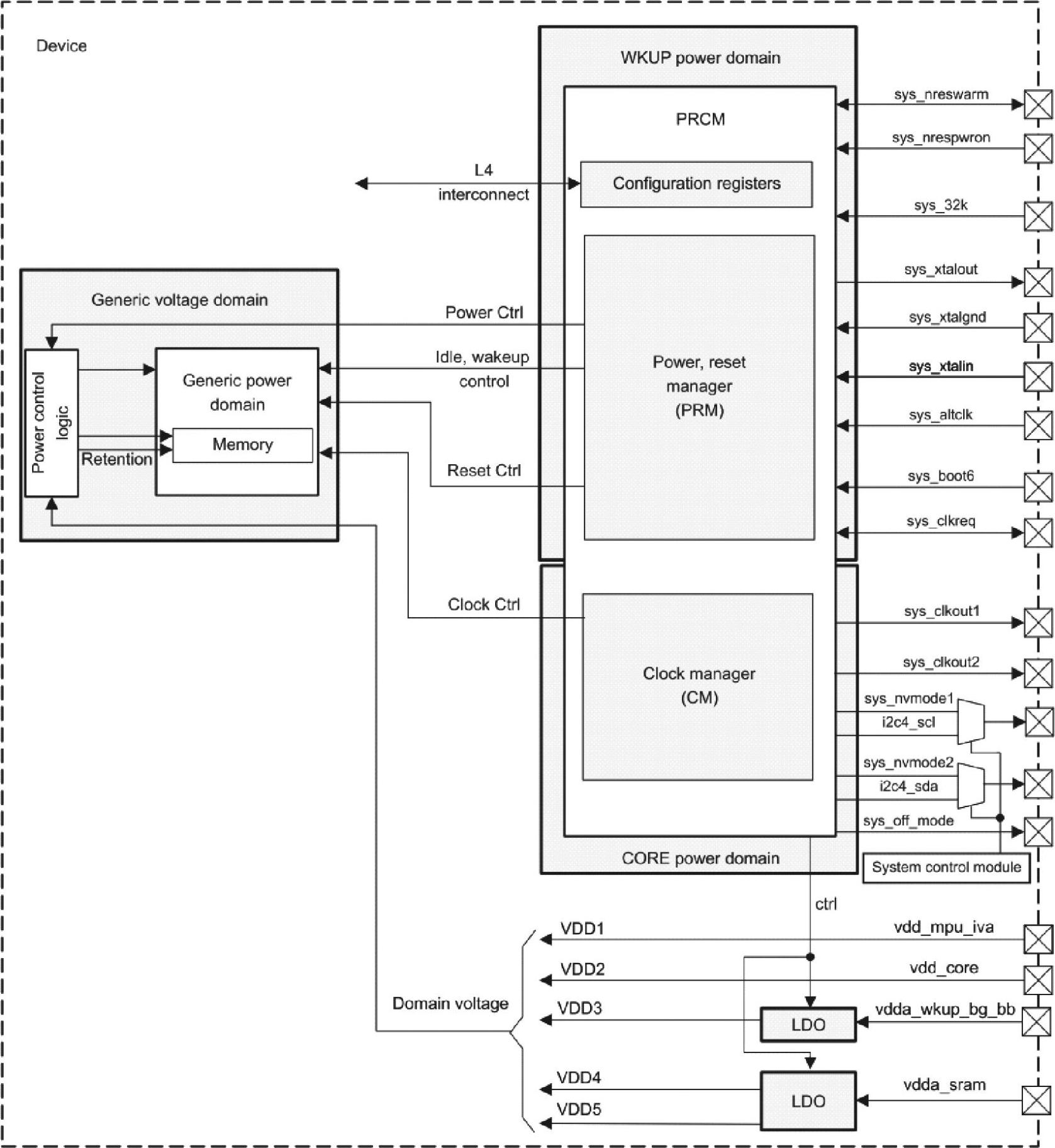

DM 3730中实现电源管理技术的模块是PRCM,PRCM是power reset clock management的缩写,从名字就可以看出该模块管理芯片内部的电源、启动和时钟信号。PRCM的系统框图如图2-4所示。

图2-4引自TI的《DM 3730芯片手册》中第237页框图,在该框图中我们明显看到有5个VDD,每个VDD对应一个voltage domain(电压域),它提供一种电压规格,可以为多个有相同电压需求的模块提供电源,voltage domain也可以理解为完整的物理供电线路。设计多个VDD的好处是可以隔离不同的电源需求,在DM 3730特性中已经介绍,它的待机功耗可以做到低于0.1mW,要实现这一点就必须将待机时工作的模块最小化,并且其他模块不能有漏电流,由于只要有电压差就会有漏电流,这就需要主要的模块在待机时电源完全关掉使电压降为0V。为了达到如此低的功耗,图2-4中的VDD1和VDD2在待机时都要降为0V。根据第1章的图1-4,可知VDD1~VDD5都是来源于电源管理芯片,所以如果要改变任意一个VDD的电压都是需要和电源管理芯片配合,由电源管理芯片完成实际的操作,可以说电源管理芯片就是按照DM 3730的要求进行操作,同样的VDD1和VDD2降为0V也是DM 3730请求电源管理芯片完成的,这个请求在DM 3730设计中采用了最简单的办法即通过一个引脚(图2-4中的sys_off_mode)极性的改变就完成了。在第1章有个遗留问题是关于最小系统框图中为什么有两个时钟(一个是32kHz Crystal,另一个是26MHz Oscillator)。现在可以说明一下,图2-4中实际也有两个时钟信号,分别是sys_32k(接入32k时钟信号)和sys_xtalin(接入26M时钟信号),在提供系统内部时钟的时候,是需要锁相环进行倍频的,由于内部最高达到1GHz的频率,所以需要26MHz时钟来倍频,可以说26MHz时钟是内部所有时钟的“父亲”。这样就遇到一个问题,在待机的时候如果还是使用26MHz这种高速的时钟,那么功耗就会有比较多的浪费,DM3730设计的时候考虑到该问题,当待机时只要提供32kHz的时钟就能保证必要的模块待机,从而尽量减少功耗。由于时钟也是电源管理芯片输出的,如果要停掉高频时钟也需要一个信号,这个信号就是图2-4中的sys_clkreq信号。可以看到DM 3730的很多电源管理功能还是需要电源管理芯片的特殊支持,所

图2-4 PRCM系统框图

以要达到好的电源管理效果需要能支持这些特殊功能的电源管理芯片。TI为DM 3730设计了一系列电源管理芯片如TPS 65950等,这样使用DM3730再加上TPS 65950的配合就能够达到很好的待机功耗,TI的参考设计中也是这么实现的。

(2)芯片内部电源控制设计

图2-4中的左侧可以看到两个名词:voltage domain和power domain,voltage domain中包含power domain。voltage domain已经做过介绍就是电压域,power domain从名字可知是和power相关的概念,它是电源控制的基本单元,控制整个域电源的开关。在优秀的电源管理设计中,不使用的模块应该是可以完全切断电源的,这样可以达到降低功耗的目的。power domain正是基于这个概念设计的。由于设计的复杂度也是要考虑的因素,权衡下来,把那些能够一起开关的模块放在一起,形成一个power domain。可见,power domain实际上是个逻辑的概念,逻辑上一起开关的模块都可以做到power domain中,这样有一个问题就是volt-age domain是和物理电压相关的概念,而power domain则是逻辑的概念,那么这两个概念之间的关系就不是纯粹的包含与被包含,而是相互重叠的概念,比如一个power domain可以在不同的voltage domain中,这些都取决于设计需求。有了power domain之后,系统在不需要某些功能的时候就可以将相应的power domain完全关断以节省电能,可以说是按需取能,该功能不仅在电池供电的设备中需要,在提倡节能环保的今天可以说所有的电子设备都需要,为了能使设备的某些功能按照需要进行开关,Linux设计了runtime power management框架。

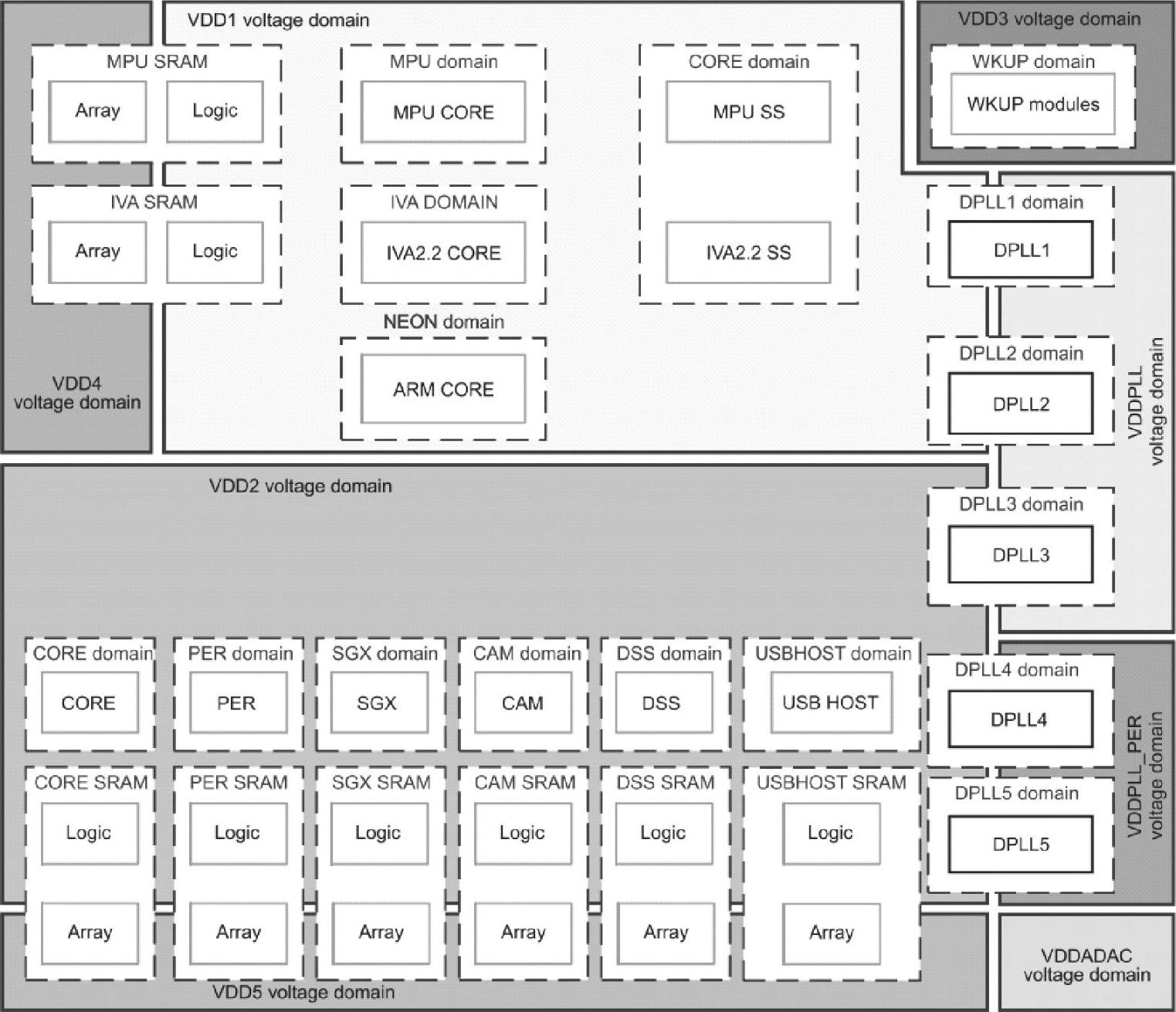

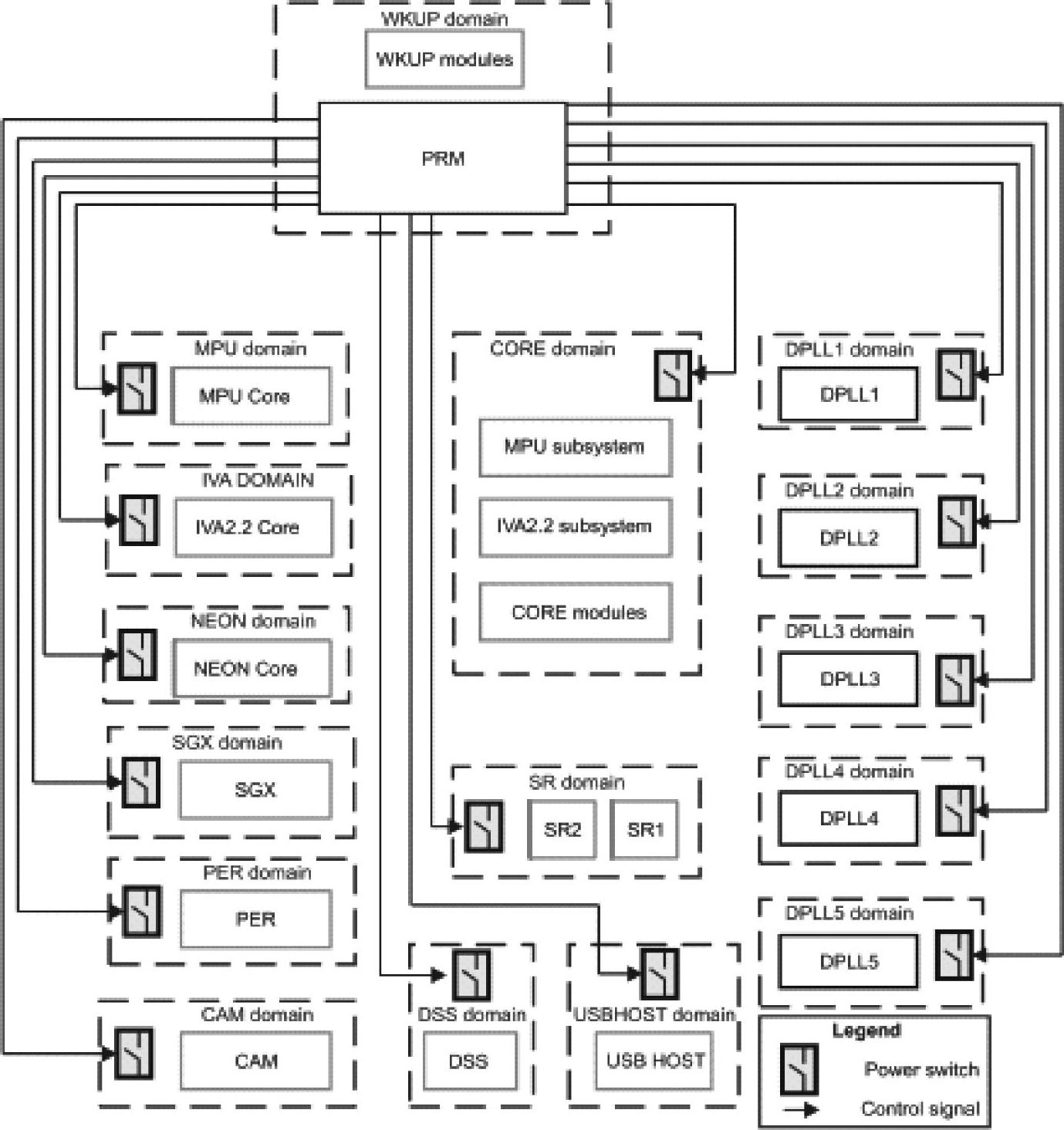

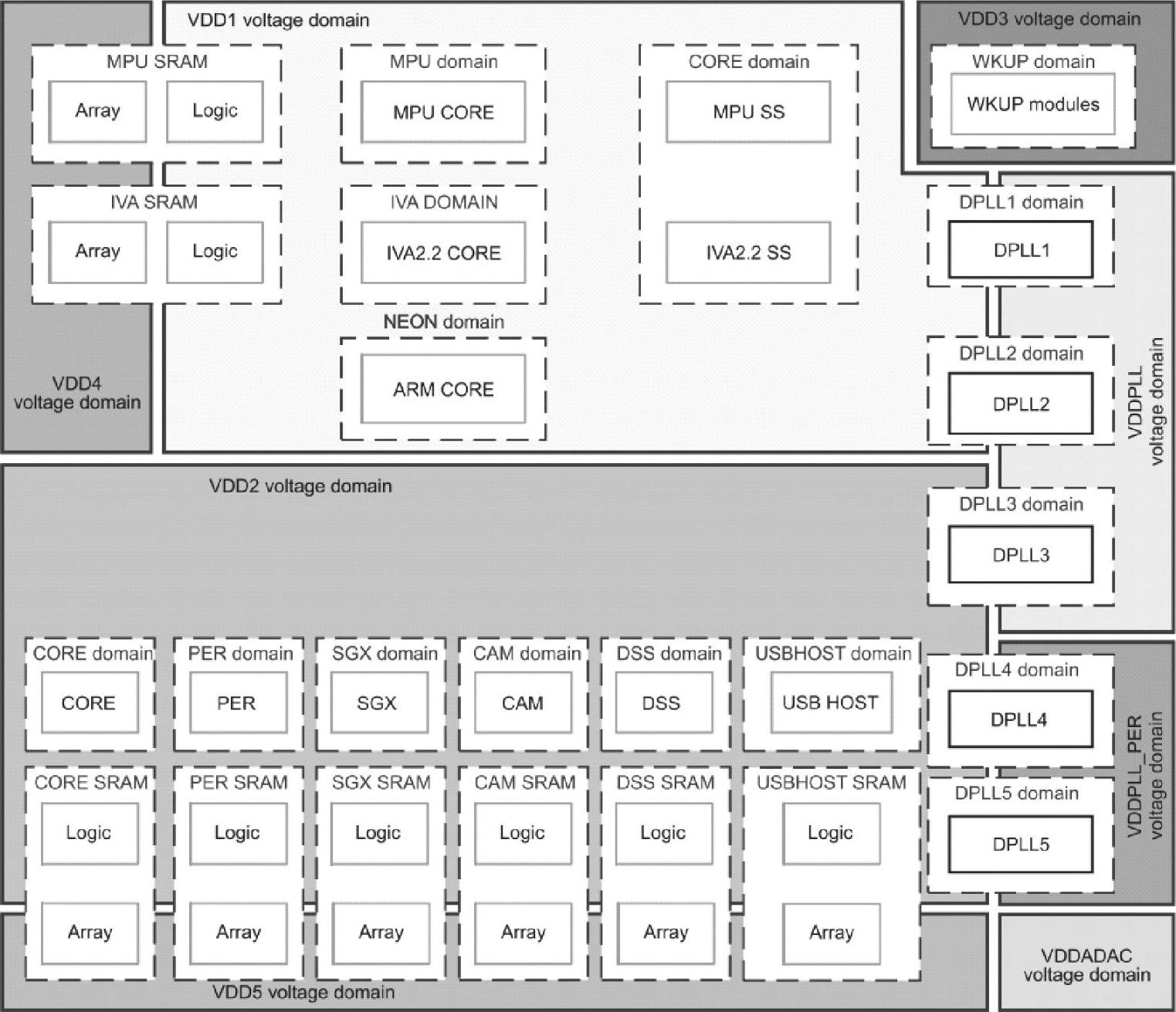

回过头来继续讨论voltage domain和power domain在DM 3730中的实现,图2-5引自TI的《DM 3730芯片手册》中第371页框图,其中描述了DM 3730中voltage domain和power domain的具体关系。

图2-5中需要注意两个部分:(www.chuimin.cn)

其一,就是VDD3 voltage domain和其中的WKUP domain。从图2-4中可以看出VDD3是由vdd3_wkup_bg_bb单独提供的一路电源,在图2-5中可以看出只有VDD3 voltage domain中包含唯一的power domain即WKUP domain,也就是说WKUP domain单独由一路电源供电,可见WKUP domain的重要性。WKUP domain之所以重要是因为在整个DM 3730的各个pow-er domain中需要一个一直保持上电的模块,这个模块需要功能最小,在需要低功耗的时候其他power domain都关闭,留下该domain当守卫,监视外部环境。如果有外部信号需要系统启动工作,该模块还需要唤醒系统,WKUP是wakeup的缩写,表示该模块上电之后一直保持清醒,可见这是一个很辛苦很重要的模块。WKUP domain中包括一组GPIO、一个通用定时器和一个看门狗定时器,这些都是在系统进入待机状态后能唤醒系统所需要的基本硬件,从中可以看出要设计有良好的电源管理功能的芯片需要考虑很多细节。

其二,就是框图中有些部分在两个voltage domain内,例如很多模块的SRAM分为Logic和Array两部分,并且分别在两个不同的voltage domain内。SRAM是每个模块内部的memory,比如cache、line buffer等。这部分的逻辑和存储分开是有好处的,可以保证存储的内容和访问操作完全分离,保证逻辑和存储可以单独设置电源管理等级,可以保证在信息不丢失的情况下尽量减少功耗。另外对逻辑(Logic)部分会根据不同的OPP调节电压,而对memory部分则没有这种需求,这也要求逻辑和存储部分的电源分离。DPLL部分也在两个voltage domain中,则是由于最终的输出时钟的使用者是有不同的OPP,如果整个DPLL的逻辑完全支持不同的OPP,设计复杂度要高,另外DPLL的时钟输入没有多个电压规格的要求,这样时钟本身在输入和输出中就可能有不同,设计时将DPLL放在两个voltage domain中就可以起到隔离的作用。另外这样的设计可以降低软件的复杂度,由于VDD1和VDD2这两个volt-age domain的状态是由软件管理的,如果DPLL完全放入这两个voltage domain,意味着软件要完全管理DPLL的状态,由于DPLL本身的状态多样,而且管理该模块需要很多硬件的知识和背景,这样由软件管理的复杂度就比较高。如果设计中将其分离,一部分DPLL的开关逻辑由硬件实现,另外一部分的时钟和所连接的模块在一个voltage domain中,这样硬件中可以自动处理一些电源管理的功能,以简化软件设计,这也是综合考虑软件和硬件的结果。可见要设计好的系统不仅要考虑硬件的实现还要考虑软件如何控制,如果软件复杂度过高则说明系统的耦合度高,需要做硬件的简化隔离来降低整个系统的复杂度,同样在板级设计过程中也要考虑软件系统设计复杂度的问题,毕竟在嵌入式系统中最终的体验和稳定性是软件和硬件整体的结果。

图2-5 voltage domain和power domain关系框图

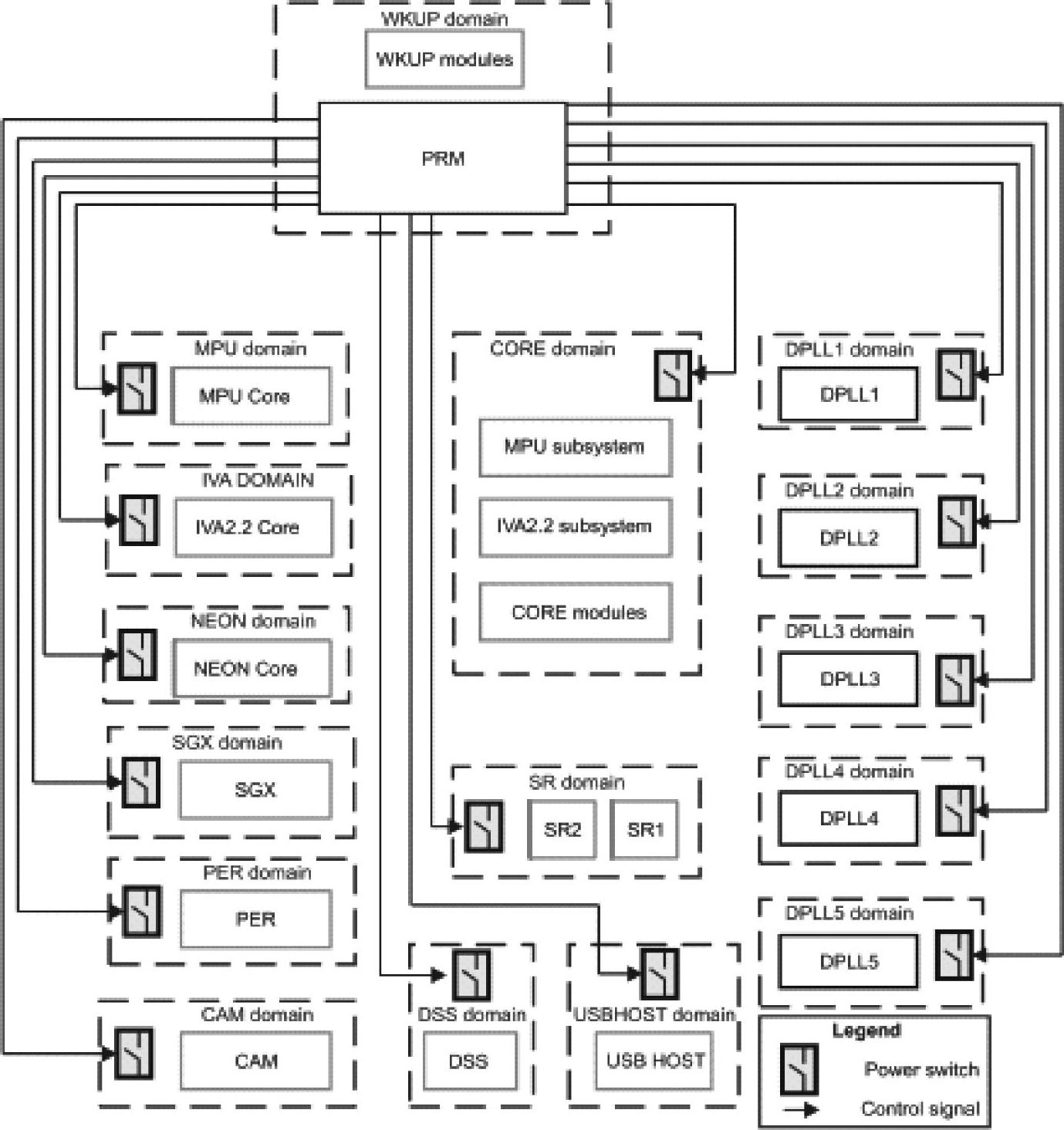

看了图2-5之后,读者也许会有疑问,既然power domain的电源开关是可以控制的,那么这个控制模块是什么?又在哪个power domain中呢?其实图2-4已经给出了基本的原理,所有power domain的控制都是由PRM模块执行的,PRM、voltage domain和power domain由power Ctrl、idle/wakeup control和reset ctrl三个控制信号连接。power ctrl信号控制voltage do-main的电源输出逻辑,决定是否为对应的power domain输出电源;idle/wakeup control让power domain中的模块进入idle模式或者唤醒系统;reset ctrl使模块进入reset状态。从图2-4可以看到PRM在WKUP domain中。这个很好理解,这里使用反证法证明,如果PRM不在WKUP domain这个唯一保持清醒的power domain中,而是在某个基本power do-main中并可以进入待机状态,那么当系统需要被唤醒的时候,就需要一个模块唤醒PRM所在的power domain,这就和PRM管理所有基本power domain这种设计思想相矛盾,所以PRM必然在WKUPpower domain中。各个power domain、PRM和WKUP domain之间的详细关系如图2-6所示。

图2-6 各个power domain详细关系框图

图2-6引自TI的《DM 3730芯片手册》中第280页框图,从中可以看到所有的power domain以及WKUP domain中的PRM和这些power domain的控制关系。

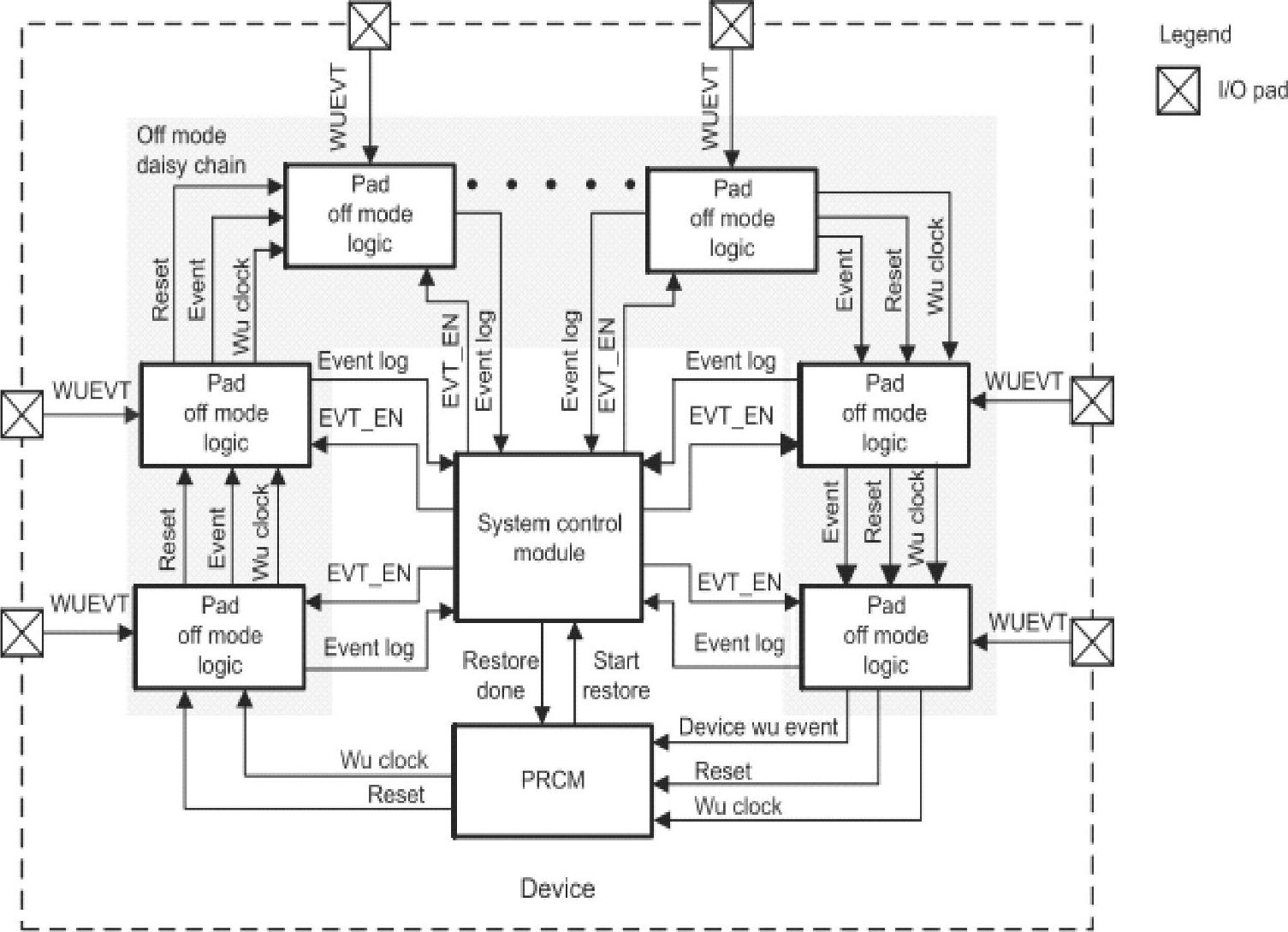

(3)引脚唤醒

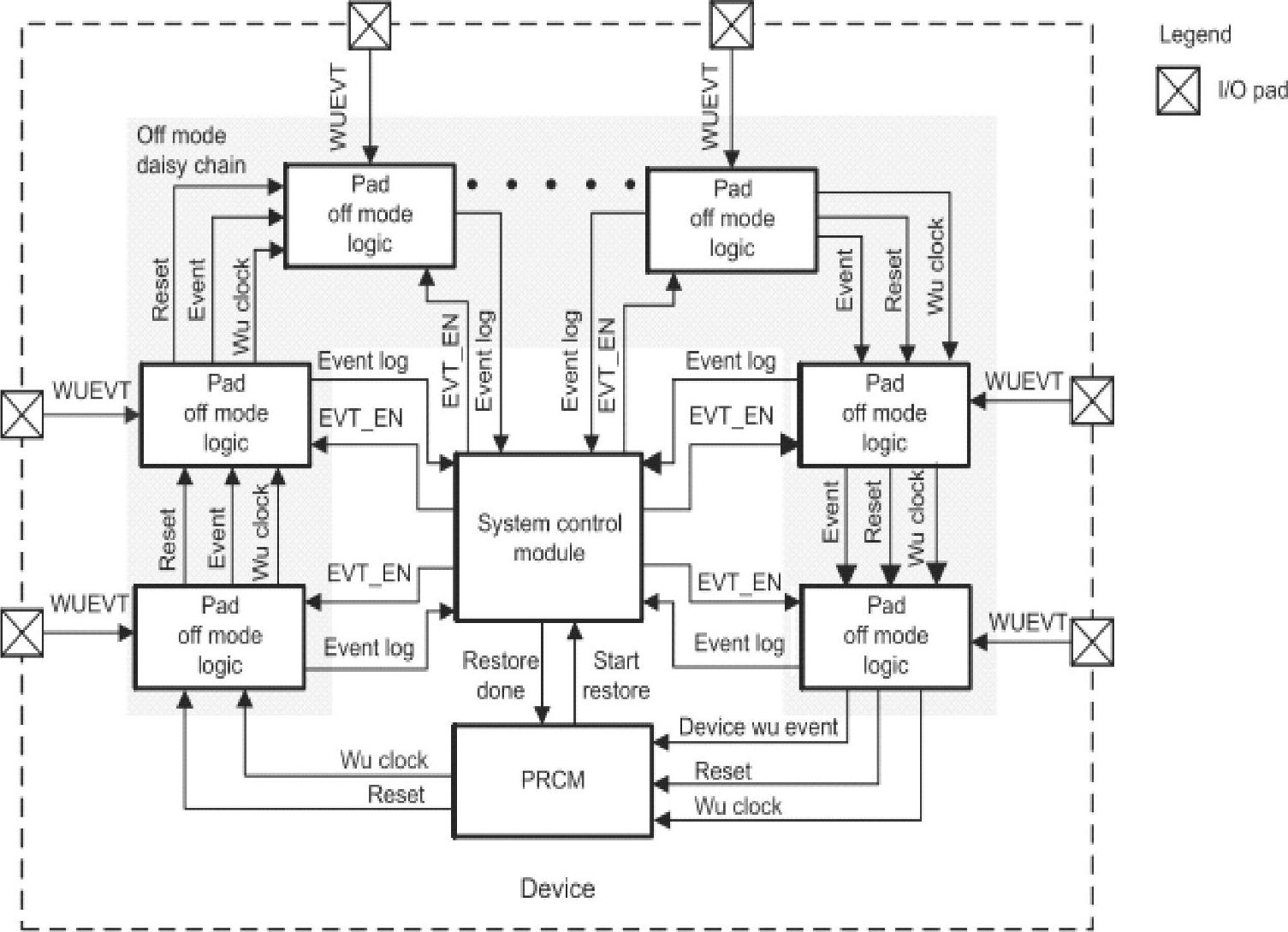

当系统进入待机状态后需要能从外部唤醒系统。这就需要DM 3730中的部分外部信号能在系统进入待机状态时监测外部信号的变化。之前说明中提到,WKUP domain中有一组GPIO可以作为外部的唤醒源来实现唤醒系统的功能,但是只有一组GPIO是无法满足需求的,终端开发厂商希望外部接口同样有唤醒系统的功能。如何实现呢,笔者认为DM 3730中采用了比较精巧的方法,其基本原理的框架如图2-7所示。

图2-7 DM 3730待机管理基本原理框图

图2-7引自TI的《DM 3730芯片手册》中第391页框图。当系统进入待机off模式时,引脚的工作模式通过pad off mode logic来接管执行,如果已经通过System control module(主要是控制引脚功能的模块)使能待机唤醒事件上报的功能,则该引脚会检测唤醒事件,一旦有相应的事件发生信号就会通过pad形成的菊花链通知一直清醒的模块(PRCM中的PRM),从而唤醒系统,系统被唤醒后再由相应的驱动程序检查是否由事件唤醒系统,如果是,则要进行后续的操作。可见这里硬件提供了唤醒系统和查询状态的机制,具体实现则还是依赖软件完成,所以不能孤立地看硬件实现,还是要关注软件如何进行操作,提供一个方便简单的操作逻辑对系统的实现以及其稳定性都至关重要。

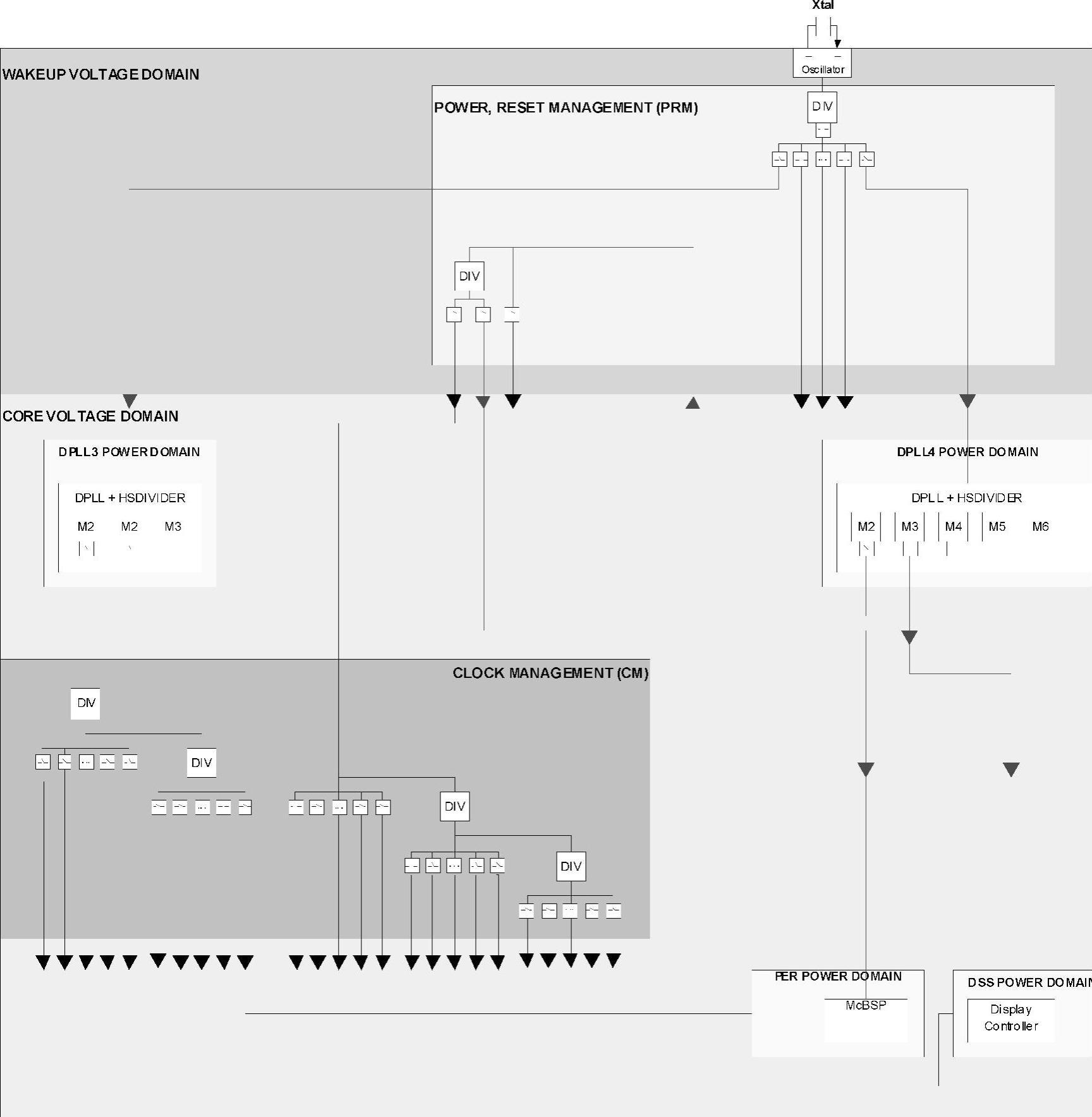

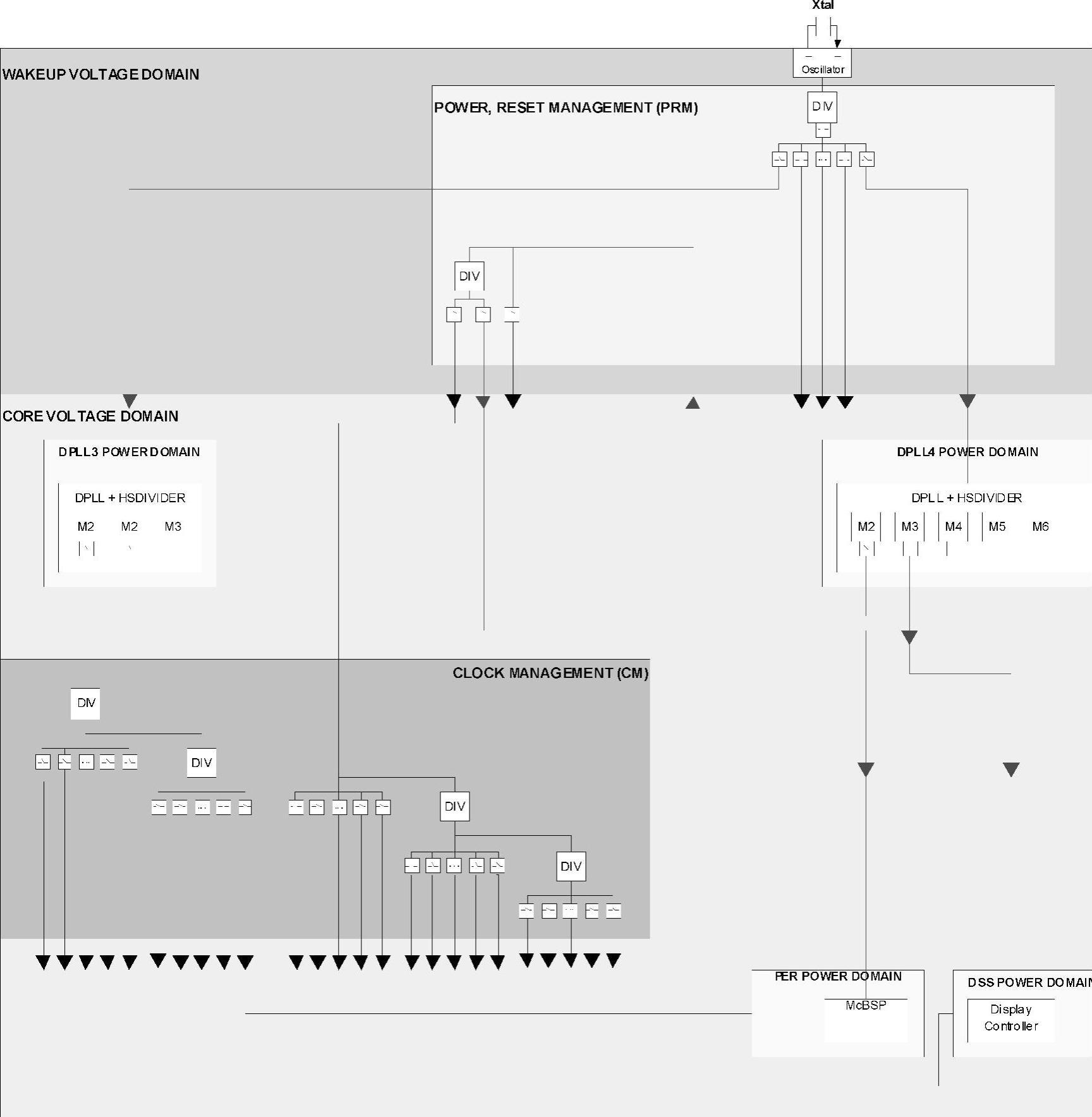

(4)时钟管理

至此,PRCM中PRM相关的功能和实现方法已经做了基本介绍,在PRCM中还有一部分就是CM(Clock Management,时钟管理),这部分主要负责各个模块的时钟产生,整个DM 3730的时钟树框图如图2-8所示。注意图2-8是示意图,从中基本可以理解时钟树的层次,具体的实现有更多的细节,但是层次的概念是相同的。从图2-8中可以看到两个voltage domain分别是wakeup voltage domain和core power domain,clock management是在core voltage domain中,为什么CM不放在wakeup voltage domain中呢?芯片设计人员这样设计还是为了能够降低待机功耗,毕竟管理所有clock的模块复杂度不会太低,而且在待机状态时外设模块都应该关掉,这样把CM放入可以关掉的core voltage domain中也是理所当然的。当然wakeup voltage domain中的PRM要执行,同样需要时钟,这样设计时就将外部的晶振或者外部提供的时钟直接接入PRM,保证这部分一直可以执行。另外图2-8中可以看到CM的输出有很多的时钟,而且每个输出时钟都有开关可以控制,这些时钟都接到了具体的模块,也就是说每个模块的输入时钟都可以控制其开关,这样就可以通过软件控制设备的时钟输入,从而达到较好的电源管理效果。时钟管理自然也是电源管理框架中的重要一环,时钟作为设备运行的必需资源需要按需开关,按需开关时钟在设备驱动程序中是非常重要的操作。

图2-8 时钟树示意框图

具体的设备模块中通常会有两种时钟,一种是interface clock(接口时钟,通常用于访问寄存器),另一种是function clock(功能时钟,主要是模块运行需要的时钟)。这两种时钟通常可以单独控制,设计两种时钟是因为寄存器通常对模块进行设置或者获取其状态,而不同设备的功能时钟频率是不同的,如果使用同一种时钟,那么寄存器操作这部分就要针对每个设备模块单独设计,增加系统复杂度。

至此,DM 3730电源管理相关设计介绍完毕,可见好的电源管理方案设计还是很复杂的,要考虑方方面面的问题。

相关推荐