基金会现场总线,是在过程自动化领域得到广泛支持和具有良好发展前景的技术。屈于用户的压力,这两大集团于1994年9月合并,成立了现场总线基金会,致力于开发出国际上统一的现场总线协议。基金会现场总线分低速H1和高速H2两种通信速率。H1的传输速率为31.25 kbit/s,通信距离可达1900 m,可支持总线供电,支持本质安全防爆环境。H2总线标准也已形成。......

2023-11-22

由于控制算法运行所需的RAM空间已经远远超出STM32F407ZG所能提供的用户RAM空间,而且,控制算法也需要额外的空间进行存储。所以,需要在系统设计时做一定的RAM空间扩展。

在电路设计中扩展了两片RAM,一片SRAM为CY62177EV30,一片MRAM为MR4A16B。设计之初,将SRAM用于控制算法运行,将MRAM用于控制算法存储。但后期通过将控制算法的存储态与运行态结合后,要求外扩的RAM要兼有控制算法的运行与存储功能,所以,必须对外扩的SRAM做一定的处理,使其也具有数据存储的功能。

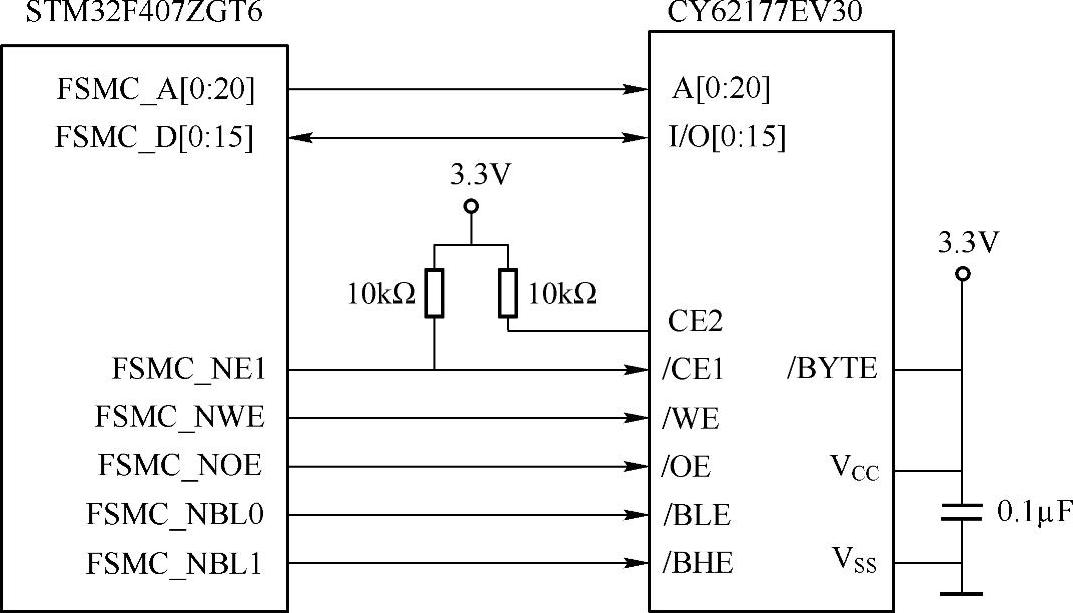

CY62177EV30属于常规的静态随机存储器,具有高速、宽范围供电和静默模式低功耗的特点。一个读写周期为55ns,供电电源可以从2.2V到3.7V,而且静默模式下的电流消耗只有3μA。CY32177EV30具有4MB的空间,而且数据位宽可配置,即可配置为16位数据宽度,也可配置为8位数据宽口。CY62177EV30通过三总线接口与微控制器连接,CY62177EV30与STM32F407ZG连接图如图11-12所示。

图11-12 CY62177EV30与STM32F407ZG的连接图

功能选择引脚/BYTE是CY62177EV30的数据位宽配置引脚,/BYTE接VCC时,CY62177EV30工作于16位数据宽度;/BYTE接VSS时,工作于8位数据宽度。(www.chuimin.cn)

扩展的第二个RAM为MR4A16B,属于磁存储器,具有SRAM的读写接口与读写速度,同时具有掉电数据不丢失的特性,即可做控制算法运行用,也可用于控制算法的存储。

MR4A16B的读写周期可以做到35ns,而且读写次数无限制,在合适的环境下数据保存时间长达20年。在电路设计中,可以替代SRAM、FLASH和E2PROM等存储器以简化电路设计,增加电路设计的高效性。而且,作为数据存储设备时,MR4A16B标称比后备电池供电的SRAM具有更高的可靠性,甚至可用于脱机存档使用。

MR4A16B的数据宽度是固定的16位,其电路设计与CY62177EV30类似,而且比CY62177EV30的电路简单,因为MR4A16B的供电直接使用控制卡上的3.3V电源,不需要使用后备电池。MR4A16B也是通过三总线接口与微控制器STM32F407ZG的FSMC模块连接,而且连接到FSMC的Bank1的region2。

其他电路的详细设计限于篇幅就不再赘述了。

有关现场总线及其应用技术的文章

基金会现场总线,是在过程自动化领域得到广泛支持和具有良好发展前景的技术。屈于用户的压力,这两大集团于1994年9月合并,成立了现场总线基金会,致力于开发出国际上统一的现场总线协议。基金会现场总线分低速H1和高速H2两种通信速率。H1的传输速率为31.25 kbit/s,通信距离可达1900 m,可支持总线供电,支持本质安全防爆环境。H2总线标准也已形成。......

2023-11-22

在对方控制卡出现故障时,一方控制卡必须能够及时发现,并接管对方的工作,同时还要向上位机报告故障情况。双机冗余电路包括上电竞争电路和状态监测电路。状态监测电路由两个D触发器实现,利用D触发器的状态转换机制可有效地完成两个控制卡间的状态监测。......

2023-11-22

PCI总线是由Intel公司提出的。PCI总线不是由ANSI通过的标准,但由于它是由厂家自发制定执行的标准,具有众多的优点,拥护者,执行者众多,成了事实上的标准。PCI总线共有100个引脚,如果只作为目标设备,至少需要47条,如作为主设备则需要49条。本设计使用位命令字,其定义如下:3.PCI总线基本协议PCI上的基本总线传输机制是突发成组传输。......

2023-11-22

现场总线控制网络处于企业网络的底层,或者说,它是构成企业网络的基础。从图中可以看出,除现场的控制网络外,上面的ERP和MES都采用以太网。图中的ERP与MES功能层大多采用以太网技术构成数据网络,网络节点多为各种计算机及外设。控制网络的主要作用是为自动化系统传递数字信息。这些都需要在现场控制层内部,在FCS与MES、ERP各层之间,方便地实现数据传输与信息共享。......

2023-11-22

INTERBUS定义了该模型的第1、2、7层。INTERBUS具有强大的可靠性、可诊断性和易维护性。INTERBUS采用了集总帧型的数据环通信。强大的诊断功能是INTERBUS区别于其他总线所独有的。INTERBUS CLUB负责向设备生产厂家提供INTERBUS的接口方案和接口芯片,向其成员提供信息,帮助解决技术问题及为特定的应用找寻合适的INTERBUS产品。INTERBUS的技术发起人为德国菲尼克斯公司。另外,在美国和中国也设有INTERBUS技术中心。......

2023-11-22

ControlNet是目前世界上增长最快的工业控制网络之一。因而,ControlNet是开放的现场总线。SIG开发的成果经过同行们审查再提交CI的技术审查委员会,经过批准,其设备行规将成为ControlNet技术规范的一部分。所有的这些现实问题推动了ControlNet的开发和发展,它正是满足不同需要的一种实时的控制层的网络。ControlNet协议的制定参照了OSI 7层协议模型,并参照了其中的1、2、3、4、7层。ControlNet中网络和传输层的任务是建立和维护连接。......

2023-11-22

WorldFIP技术硬件体系由两个互补的部分组成:通信控制器和通信介质器件。5)用于WorldFIP连接的费用要求。WorldFIP现场总线第一个通信控制器是在1987年开发成功的。图8-9 WorldFIP现场总线通信站的连接......

2023-11-22

LonWorks技术所采用的LonTalk协议封装在被称为Neuron的芯片中并得以实现。LonWorks技术的不断推广促成了神经元芯片的低成本,而芯片的低成本又反过来促进了LonWorks技术的推广应用,形成了良好循环。据称目前已有4000多家公司在不同程度上卷入LonWorks技术;1000多家公司已经推出了LonWorks产品,并进一步组织起LonMark互操作协会,开发推广Lon Works技术与产品。LonWorks技术已经被美国暖通工程师协会ASHRE定为建筑自动化协议BACnet的一个标准。......

2023-11-22

相关推荐