现场总线的基础是数字通信,通信就必须有协议。现场总线有两种编码方式:Manchester和NRZ。现场总线传输介质主要有有线电缆、光纤和无线介质。现场总线网络中的设备可以是主站,也可以是从站。应用层的功能是进行现场设备数据的传送及现场总线变量的访问。......

2025-09-30

POWERLINK是一个实时以太网的技术规范和方案,它是一个技术标准,用户可以根据这个技术标准自己开发一套代码,也就是POWERLINK的具体实现。POWERLINK的具体实现有多个版本,如ABB公司的POWERLINK运动控制器和伺服控制器、赫优讯的从站解决方案以及SYSTEC的解决方案等。

OperPOWERLINK是一个C语言的解决方案,它最初是SYSTEC的商业收费方案,后来被B&R公司买断版权。为了推广POWERLINK,B&R将源代码开放。现在这个方案由B&R公司和SYSTEC共同维护。

目前常用的POWERLINK方案有两种:基于MCU/CPU的C语言方案和基于FPGA的Verilog HDL方案。C语言的方案以OpenPOWERLINK为代表。下面仅介绍C语言方案。

1.C语言实现方案

该方案最初由SYSTEC开发,B&R公司负责后期的维护与升级。该方案包含了POWER-LINK完整的3层协议:物理层、数据链路层和CANopen应用层。其中数据链路层和CANo-pen应用层采用C语言编写,因此该方法可运行于各种MCU/CPU平台。该方案性能的优劣取决于运行该方案的软硬件平台的性能,例如MCU/CPU的主频、操作系统的实时性等。

(1)硬件平台

该方案可支持ARM、DSP和X86 CPU等平台,物理层采用MCU/CPU自带的以太网接口或者外接以太网。该方案如果运行于FPGA中,需要在FPGA内实现一个软的处理器,如Nios或Microblaze。数据链路层和CANopen应用层运行于MCU/CPU之上。

(2)软件平台

该方案可支持VxWorks、Linux和Windows等各种操作系统。在没有操作系统的情况下,也可以运行。POWERLINK协议栈在软件上需要高精度时钟接口和以太网驱动接口。由于POWERLINK协议栈的行为由定时器触发,即什么时刻做什么事情,因此如果需要保证实时性,就需要操作系统提供一个高精度的定时器,以及快速的中断响应。有些操作系统可以提供高精度的时钟接口,有些则不能。定时器的精度直接影响POWERLINK的实时精度,如果定时精度在毫秒级,那么POWERLINK的实时性也只能达到毫秒级,例如在没有实时扩展的Windows上运行POWERLINK,POWERLINK的最短周期、时隙精度都在毫秒级。如果希望POWERLINK的实时精度达到微秒级,则需要提供微秒级的定时器接口给POWERLINK协议栈。大部分操作系统无法提供微秒级的定时器接口,对于这种情况,需要用户根据自己的硬件编写时钟的驱动程序,直接从硬件上得到高精度定时器接口。另外,POWERLINK需要实时地将要发送的数据发送出去,对接收到的数据帧要实时处理,因此对以太网数据收发的处理,也会影响POWERLINK的实时性,故需要以太网的驱动程序也是实时的。对于有些系统,如VxWorks,POWERLINK可以采用操作系统本身的以太网驱动程序,而对于有些系统,需要用户根据自己的硬件编写以太网驱动程序。

(3)基于Windows的方案

基于Windows的OpenPOWERLINK解决方案,以太网驱动采用Wincap。由于Windows本身的非实时性,导致该方案的实时性成本不高,循环周期最短为3~5ms,抖动为1ms左右,因此该方案可用于实时性要求不高的应用场合,或者用于测试。

该方案的好处是运行简单,不需要额外的硬件,一台带有以太网的普通PC就可以运行。

(4)基于Linux的方案

OpenPOWERLINK需要Linux的内核版本为2.6.23或者更高。

(5)基于VxWorks的方案(https://www.chuimin.cn)

POWERLINK运行在MUX层之上。

该方案使用了VxWorks本身的以太网驱动程序,OpenPOWERLINK需要一个高精度的时钟,否则性能会受到影响。基于VxWorks的高精度的时钟,通常由硬件产生,用户往往需要根据自己的硬件编写一个高精度时钟的驱动程序。

(6)基于FPGA的方案

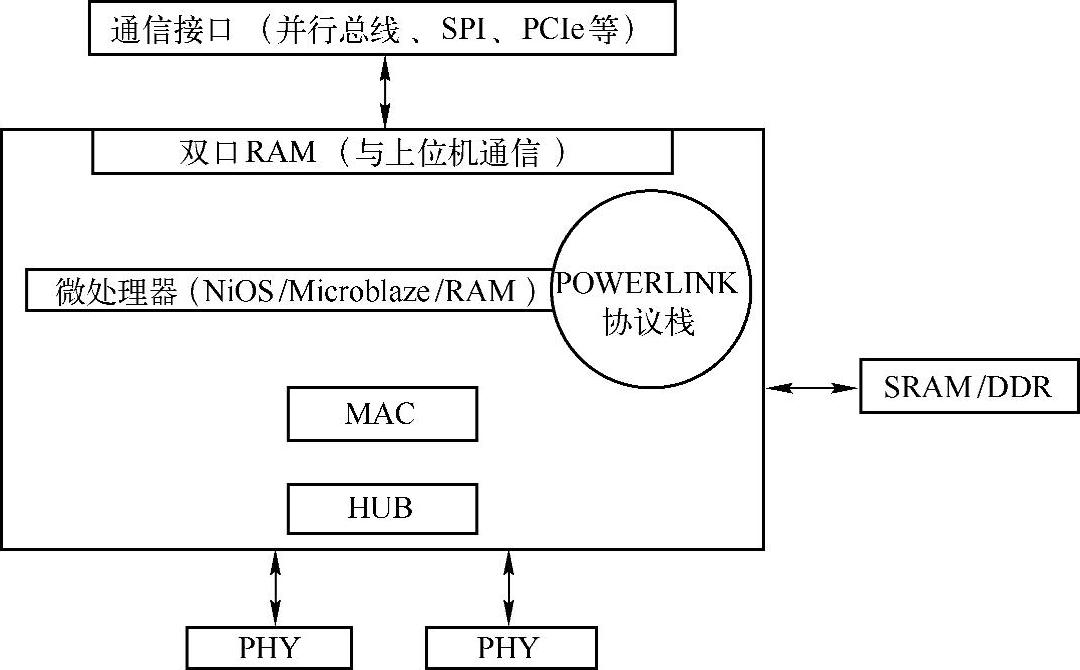

OpenPOWERLINK采用C语言编写,如果要在FPGA中运行C语言编写的程序,需要一个软核,其结构如图10-10所示。

一个基于FPGA的POWERLINK最小系统需要如下硬件:

1)FPGA:可以选用ALTERA或者XILLINX。需要逻辑单元数在5000Les以上,对于ALTERA可以选择CYCLONE4CE6以上,对于XILLINX可以选择spartan6。

2)外接SRAM或SDRAM:需要521 kB的SRAM或者SDRAM,与FPGA的接口为16位或者32位。

图10-10 基于FPGA的POWERLINK的结构

3)EPCS或者FLASH配置芯片:需要2MB以上的EPCS或FLASH配置芯片来保存FP-GA的程序。

4)拨码开关:因为POWERLINK是通过节点号来寻址的,每个节点都有一个Node ID,可以通过拨码开关来设置节点的Node ID。

5)以太网的PHY芯片:需要1个或2个以太网PHY芯片。我们在FPGA里用VHDL实现了一个以太网HUB,因此如果有两个PHY,那么在做网络拓扑的时候就很灵活,如果只有一个PHY那就只能做星形拓扑。POWERLINK对以太网的PHY没有特别的要求,从市面上买的PHY芯片都可以使用。注意,建议PHY工作在RMII模式。

可以把FPGA当作专门负责POWERLINK通信的芯片。FPGA与用户的MCU之间可以通过并行16/8位接口、PC104、PCIe或者SPI接口通信。我们在FPGA里实现了一个双口RAM,作为FPGA中的POWERLINK与用户MCU数据交换区。

在同一个FPGA上,除了实现POWERLINK以外,用户还可以把自己的应用加到该FP-GA上,例如用FPGA做一个带有POWERLINK的I/O模块,该模块上除了带有POWERLINK外,还有I/O逻辑的处理。

相关文章

现场总线的基础是数字通信,通信就必须有协议。现场总线有两种编码方式:Manchester和NRZ。现场总线传输介质主要有有线电缆、光纤和无线介质。现场总线网络中的设备可以是主站,也可以是从站。应用层的功能是进行现场设备数据的传送及现场总线变量的访问。......

2025-09-30

WorldFIP技术硬件体系由两个互补的部分组成:通信控制器和通信介质器件。5)用于WorldFIP连接的费用要求。WorldFIP现场总线第一个通信控制器是在1987年开发成功的。图8-9 WorldFIP现场总线通信站的连接......

2025-09-30

2005年基于以太网的SERCOSⅢ面世,并于2007年成为国际标准IEC 61158/61784。迄今为止,SERCOS已发展了三代,SERCOS接口协议成为当今唯一专门用于开放式运动控制的国际标准,得到了国际大多数数控设备供应商的认可。目前已有200多万个SERCOS站点在工业实际中使用,超过50个控制器和30个驱动器制造厂推出了基于SERCOS的产品。SERCOS接口规范使控制器和驱动器间数据交换的格式及从站数量等可以进行组态配置。......

2025-09-30

为满足实时性要求,也为了实现工业网络的低成本,现场总线采用的通信模型大都在OSI模型的基础上进行了不同程度的简化。图2-24 OSI与部分现场总线通信参考模型的对应关系图2-24中的H1指IEC标准中的61158。图2-25是OSI模型与另两种现场总线的通信参考模型的分层比较。其中LonWorks采用了OSI模型的全部七层通信协议,被誉为通用控制网络。......

2025-09-30

OSI参考模型和TCP/IP参考模型有很多相似之处。TCP/IP参考模型最初没有明确区分服务、接口和协议,虽然后来人们试图改进它以便接近于OSI。因此,OSI模型中的协议比TCP/IP参考模型的协议具有更好的隐藏性,在技术发生变化时能相对比较容易地替换掉。OSI参考模型产生在协议发表之前。而TCP/IP却正好相反。现在我们从一般问题转向更具体一些,两个模型间明显的差别是层的数量:OSI模型有7层,而TCP/IP模型只有4层。......

2025-09-30

CAN遵从OSI模型,按照OSI标准模型,CAN结构划分为两层:数据链路层和物理层。图4-1 CAN的分层结构和功能LLC子层的主要功能是:为数据传送和远程数据请求提供服务,确认由LLC子层接收的报文实际已被接收,并为恢复管理和通知超载提供信息。MAC子层的功能主要是传送规则,亦即控制帧结构、执行仲裁、错误检测、出错标定和故障界定。CAN技术规范2.0B定义了数据链路中的MAC子层和LLC子层的一部分,并描述与CAN有关的外层。MAC子层是CAN协议的核心。......

2025-09-30

PCI总线是由Intel公司提出的。PCI总线不是由ANSI通过的标准,但由于它是由厂家自发制定执行的标准,具有众多的优点,拥护者,执行者众多,成了事实上的标准。PCI总线共有100个引脚,如果只作为目标设备,至少需要47条,如作为主设备则需要49条。本设计使用位命令字,其定义如下:3.PCI总线基本协议PCI上的基本总线传输机制是突发成组传输。......

2025-09-30

图1-8 通过互连构建一体化的企业网络图1-9 通过控制网络构建一体化的企业网络3)将现场总线控制网络与Intranet集成,如图1-10所示。图1-10 现场总线控制网络与Intranet集成在该方案中,动态数据库处于核心位置,它一方面根据现场信息动态地修改自身数据,并通过动态浏览器的方式为监控站提供服务;另一方面接受监控站的控制信息对其进行处理并送往现场。此外,为了保证控制的实时性,控制信息也可不经过动态数据库而直接下发到现场。......

2025-09-30

相关推荐