在上述结构损伤量化公式的推导中,并未考虑钢架结构中大量存在的各类节点及其损伤对于结构损伤的影响。当涉及多个构件连接处的端部时,节点自身的转动刚度同时受其远端支撑情况的影响。由式可见,框架节点的弯矩分配系数由连接于节点的各构件远端支撑条件决定。同时,当节点刚度因节点损伤发生变化时,则需考虑节点处的损伤对于结构层次损伤的影响。......

2025-09-30

神经元芯片的11个I/O可以定义为并行I/O对象、串行I/O对象支持与主机的通信。从数据速率和通信方式上看,神经元芯片提供的串行接口有很大的局限性。当速率要求大于4800 bit/s的情况下,串行I/O对象无法实现。因此,根据具体应用的要求,可以采用神经元芯片预定义的并行I/O口对象。

与普通神经元节点比较,Host-Bost结构节点增加了一个主处理器8515,进行数据采集和处理的应用电路接到主处理器8515的端口上,而不是直接接到神经元芯片的I/O端口上。8515与神经元芯片之间通过单字节FIFO的并行接口进行数据交换。

1.硬件电路

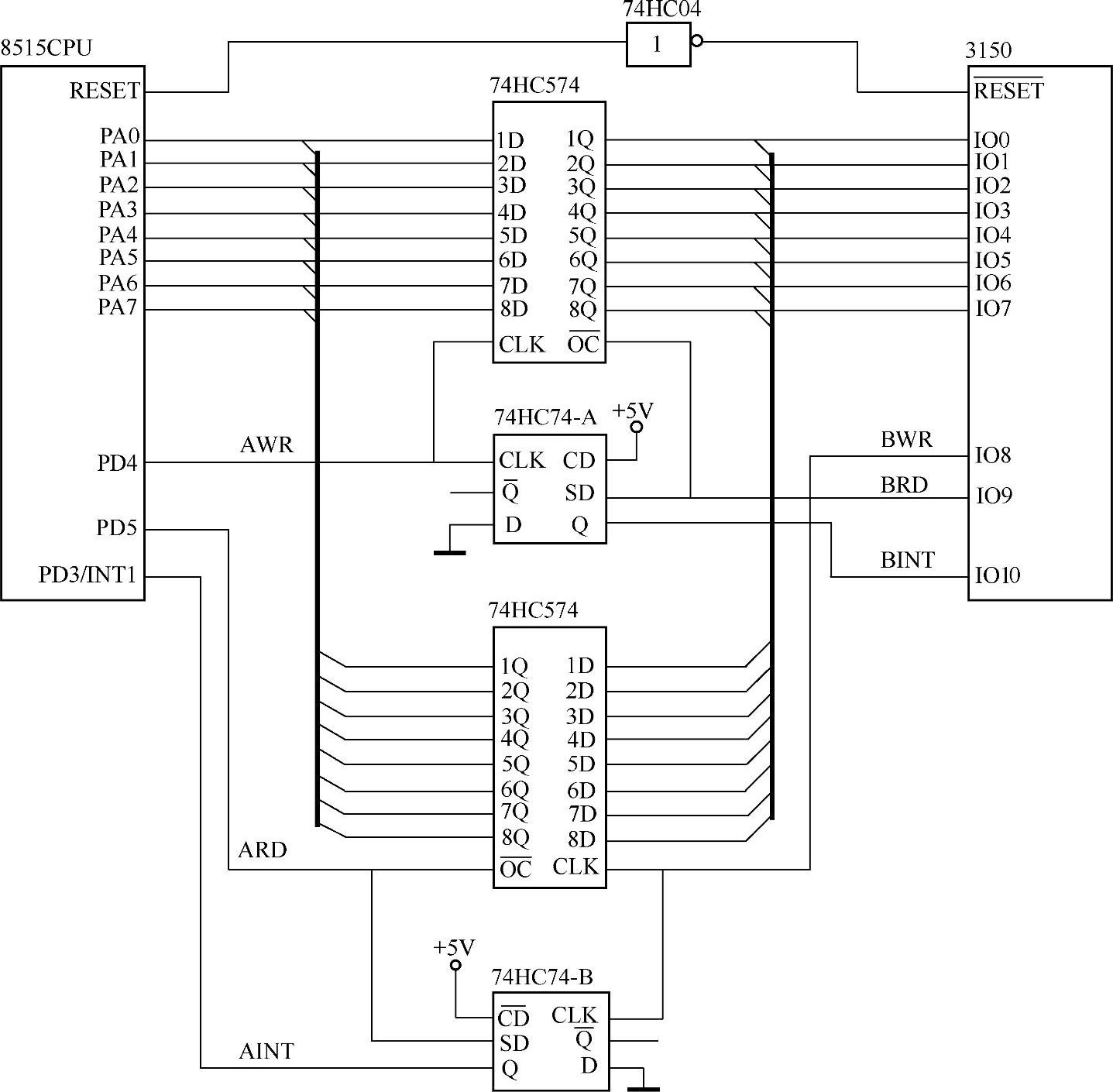

Host-Base结构节点的硬件电路如图5-38所示。

图5-38 并行接口连接图

图5-38中,8515是Atmel公司生产的Mega8系列中的一款8位单片微控制器,它采用了RISC精简指令,指令可以在一个时钟周期内执行,具有高速的数据处理速度;32个通用寄存器使指令运算更灵活,这些功能使它具有比AT89S52更高的性价比。它为40引脚PDIP封装,内含8KB的Flash Memory,512B的内部RAM,最高工作频率是20 MHz。8515单片微控制器PA口的8条I/O口线与神经元芯片进行数据交换,PD4为写控制信号线(AWR),PD5为读控制信号线(ARD),INT1外部中断1是读/写请求联络信号线(AINT)。其中,PA口工作在普通的I/O功能而不是用作数据线。

2.工作原理

在神经元芯片这一侧,它的11个I/O口配置成并行I/O接口,其中IO0~IO7提供了数据线,IO8、IO9和IO10分别是神经元芯片一侧的写控制信号线(BWR)、读控制信号线(BRD)和读/写请求联络信号线(BINT)。

单字节的并行接口由两片74HC574和一片74HC74组成。74HC574是带三态输出控制的8D触发器,数据的输入由CLK信号的上升沿控制,数据的输出由OC信号的低电平选通。74HC74是带预置端和清除端的双D触发器。在图5-38中,74HC74的D引脚接地,CLK引脚的上升沿使输出为低电平,SD引脚的低电平使输出为高电平。并行接口的两端分别接主处理器8515和Neuron芯片。以下简称8515为A机,Neuron芯片为B机。并行通信设计的关键是协调好双方的收发进程。

从8515CPU向Neuron芯片发送单个字节的过程如下:(https://www.chuimin.cn)

1)通过8515CPU的PA口把数据送入图5-38中上边的74HC574锁存器的输入端1D~8D。

2)使8515CPU的PD4变高,ARW产生上升沿,数据被74HC574锁存,同时使得BINT信号变低,通知B机读取数据。

3)B机检测到BINT后,将BRD置低,把74HC574中锁存器的数据送到BD0~BD7上,同时置高BINT,清除请求信号。

4)B机从BD0~BD7读取到数据后,置高BRD,释放数据总线BD0~BD7。

5)B机将BWR置高,产生上升沿,使AINT变低,通知A机可以继续发数据。

6)A机的INT1收到AINT后,把ARD置低,使AINT变高,消除B机的请求信号。

7)A机将ARD置高,释放BD0~BD7。

重复上述过程就能实现从8515CPU到Neuron芯片的多字节传送。从Neuron芯片发送数据到8515的过程与上面相同。

另外,上电后Neuron芯片和8515CPU在初始化所用的时间不同,神经元芯片要有很多复位处理任务,耗时较长。为了让8515CPU与Neuron芯片尽量同步开始工作,设计时把Neuron芯片的复位输出经74HC04取反后接到8515CPU的复位引脚上。当Neuron芯片在运行中如果出现复位,则这种电路保证8515CPU也进行同步的复位初始化,从而保证了节点出现意外时能可靠地工作。

相关文章

在上述结构损伤量化公式的推导中,并未考虑钢架结构中大量存在的各类节点及其损伤对于结构损伤的影响。当涉及多个构件连接处的端部时,节点自身的转动刚度同时受其远端支撑情况的影响。由式可见,框架节点的弯矩分配系数由连接于节点的各构件远端支撑条件决定。同时,当节点刚度因节点损伤发生变化时,则需考虑节点处的损伤对于结构层次损伤的影响。......

2025-09-30

图5.1 以Pixhawk开源飞控为核心的四旋翼飞行器FCS连接图无人机系统所涵盖的硬件数量本已庞大,随着任务要求的不断深入,应用领域的不断扩展,硬件种类还在持续增加。在本书中,将无人机系统硬件细分为六个部分:飞行控制系统、动力系统、被控对象、有效负载、地面系统和能量单元。有效负载对任务实现的重要性是非常直接的,同时它也影响着无人机系统功能、结构设计、机型选择、硬件组成等方方面面。......

2025-09-29

可以从节点核心区的受力机理进一步了解斜裂缝的产生原因,了解纵向钢筋的锚固和箍筋的作用。图6-18 节点核心区a)受力示意图 b)核心区混凝土破碎 c)钢筋成灯笼状图6-19 节点的拉杆—压杆模型a)实测得到的斜向压应变 b)拉杆—压杆模型我国规范采用了保证核心区的抗剪承载力的设计方法,配置节点核心区的箍筋以抵抗斜裂缝的开展,要求在梁端钢筋屈服以前,核心区不发生剪切破坏,体现了强节点的要求。......

2025-09-30

槽孔长度不应超过开孔件厚度的10倍,最小及最大槽宽规定与塞焊孔的最小及最大孔径规定相同。连续角焊缝的受力性能较好,应用较为广泛;断续角焊缝两端的应力集中较严重,一般只用在次要构件或次要焊缝连接中。图3-11 T形、十字形、角接接头防止层状撕裂的节点构造设计承受静载荷的节点,在满足接头强度计算要求的条件下,用部分焊透的对接与角接组合焊缝代替完全焊透坡口焊缝。......

2025-09-30

图6.23第一代路由器硬件结构示意图图6.23中,物理接口仅负责完成IP包的接收和发送,CPU 负责提取IP包首部信息、查询路由表、决定转发出口等工作。图6.25第三代路由器硬件结构示意图现在的核心网中部署的大型路由器需要处理大量的数据包,具有极高的处理速......

2025-09-29

“Z”字形拼接节点的特点在于需要保证轴向受力可靠,同时可承担弯矩和剪力的要求。图3.4胶合木梁“Z”字形拼接节点受力特点胶合木结构在加工、施工过程中都有误差,如果拼接缝隙较大,现场均要采用垫板的方式确保接缝顶紧。图3.5胶合木梁“Z”字形拼接节点为了验证以上计算及分析,进行了膨胀性试验,将胶合木安装螺钉,装入木箱模拟潮湿环境,让胶合木发生膨胀。......

2025-09-30

表5.14-2 编码器真值表表5.1中,“x”表示不定位,可以是“0”,也可以是“1”,根据真值表写出Verilog实现代码,如例5.2所示。例5.2 4-2编码器示例主要使用casex语句实现编码过程,其测试文件如例5.3所示。例5.3 4-2编码器测试文件编码结果如图5.12所示。例5.5 四分频器测试代码仿真结果如图5.13所示。......

2025-09-29

硬件测试系统包含本项目所使用的硬件设备,主要包括传感器、信号调理器、数据采集设备和计算机等部分。物流包装材料无害化生产过程数据采集系统硬件设备主要包括塑料注塑成型机、计算机、数据采集卡、传感器、信号调理器等。通过数据采集卡获取数据是主要的渠道,系统采用了NI公司基于PCI总线的数据采集卡PCI6221以及USB接口的数据采集卡USB6221,采集卡集成了A-D转换和数字I/O等功能。图6-13 测试系统硬件设计方案表6-3 采集所用的各种传感器......

2025-09-29

相关推荐