基金会现场总线,是在过程自动化领域得到广泛支持和具有良好发展前景的技术。屈于用户的压力,这两大集团于1994年9月合并,成立了现场总线基金会,致力于开发出国际上统一的现场总线协议。基金会现场总线分低速H1和高速H2两种通信速率。H1的传输速率为31.25 kbit/s,通信距离可达1900 m,可支持总线供电,支持本质安全防爆环境。H2总线标准也已形成。......

2023-11-22

LON网络智能适配器包括硬件设计、配置空间的定义以及驱动程序的开发。

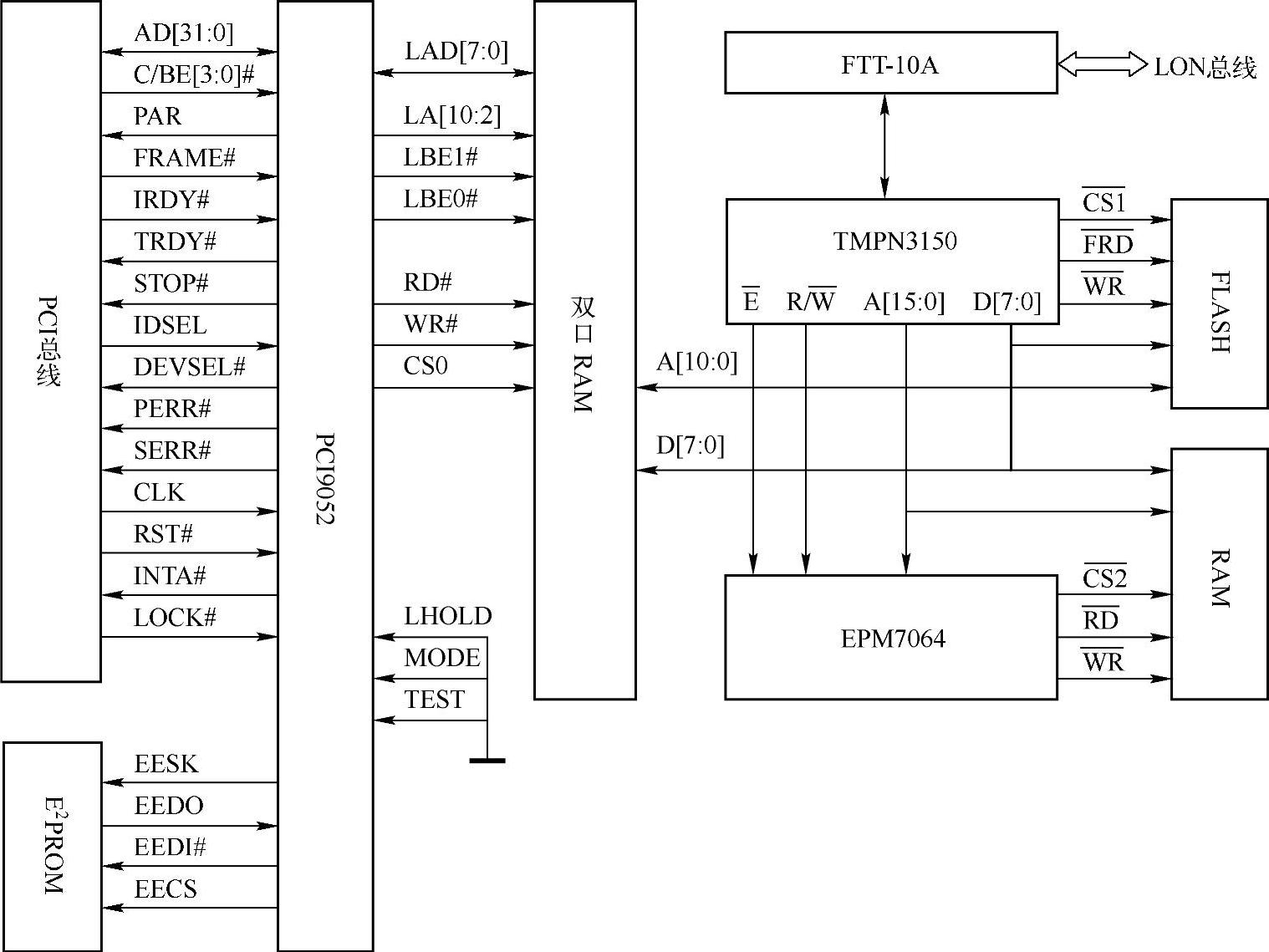

智能适配器硬件可分成两部分,一部分是属于PC一侧的,它通过PCI总线实现了与PC的联系,包括PCI桥接芯片(PCI9052)和串行E2PROM(93LC46B);另一部分是属于神经元芯片一侧的,它实现了与LON总线的数据交换,硬件还包括神经元芯片TMPN3150、扩展的FLASH、扩展的RAM以及LON收发器。在这两部分之间通过一个双口RAM(IDT7130)作为数据缓冲区进行数据交换,以实现PC和LON总线之间的双向数据传送。

双口RAM提供了两个完全独立的端口,每个端口都有完整的地址、数据和控制线。对器件的使用者而言,它与一般RAM并无大的区别,只有在两边同时读写同一地址单元时,才发生争用现象。通过双口RAM提供的指示信号,采用适当的通信规则就可以避免争用。设计中选用了1KB的IDT7130双口RAM。

PCI总线的协议比较复杂,各种规则限制繁多,尤其对时序要求非常严格。为了简化设计,选用了第三方生产的PCI专用接口芯片。

PCI设备分为主模式和从模式。主模式桥芯片可以进行DMA操作,而从模式只能进行读写操作。现有的PCI接口芯片主要有AMCC公司的AMCCS59xx系列、PLX公司的PCI905x系列、Cypress公司的CY7C09449和TI公司的PCI2031等。各公司推出的PCI器件的主要特点见表5-14。

表5-14 不同PCI器件的特点

PCI总线的数据吞吐量(最大132 Mbit/s)可以满足LON的传输速率(最大1.25 Mbit/s)的需要,不需要进行DMA操作。在LON智能适配器的开发过程中,采用了PLX公司的PCI9052从模式接口芯片。PCI9052的主要特点如下:

1)支持直接从方式数据传送模式。这种方式指的是由PCI主设备发起数据传送,通过PCI9052直接访问局部总线。

2)ISA模式。支持PCI总线到ISA总线的单周期存储器(8位或16位)读写和I/O访问。

3)中断产生器。由局部总线的两个中断信号LINTi可以产生一个PCI中断信号INTA#。

4)PCI9052的局部总线与PCI总线的时钟相互独立运行。局部总线的时钟频率范围为0~40 MHz,PCI的时钟频率范围为0~33 MHz。

5)4个局部设备片选信号。各设备的基址、地址范围及其映射可由串行E2PROM或主机编程实现。

6)可编程实现读写信号选通的延迟和写周期的保持。

7)5个局部地址空间基址、地址范围及其映射可由串行E2PROM或主机编程实现。

8)支持Big/Little Endian模式字节的交换,适用于不同的计算机体系。

9)PCI9052包括一个64B的FIFO写和一个32B的FIFO读,从而支持预取模式,即突发操作。

10)PCI主控设备可以通过锁定信号独占对PCI9052的访问。

11)局部总线等待状态除了用于握手的等待信号LRDYi#外,PCI9052还有一个内部等待发生器(包括地址到数据周期、数据到数据周期和数据到地址周期的等待)。

PCI9052支持从PCI到ISA总线的单周期读写访问,能实现ISA到PCI接口的转换,但其转换电路烦琐。在设计中,采用直接数据转换模式即PCI到局部总线的内存映射和I/O映射的突发读写。

局部总线端的时钟信号LCLK可以由PCI总线的时钟通过串接一个50Ω的电阻引入,也可以直接引入神经元芯片的10 MHz的时钟。本设计没有使用中断功能,必须接上拉电阻以防止LINTi信号线的电平不确定。

LON网络智能适配器的系统组成示意图如图5-35所示。

(www.chuimin.cn)

(www.chuimin.cn)

图5-35 LON网络智能适配器系统组成示意图

图5-35中,MODE接地,表示局部总线(Local Bus)采用了非复用模式;LHOLD接地,表示PCI9052一直是局部总线的主控设备,掌握对局部总线的控制权,也就是说,可以主动对双口RAM进行读或写。值得注意的是,从PCI9052到IDT7130的地址线的高9位由LA[10:2]提供,而低两位由LBE1#和LBE0#提供。

PCI的资源是动态配置的,即PCI插槽内插上智能适配器后,操作系统能够根据PCI配置寄存器的内容自动分配128B物理内存,映射到局部配置寄存器,同样也分配128B I/O空间映射到局部配置寄存器,并分配1KB的物理内存映射到1KB的双口RAM。分配的地址随内存和I/O空间的使用情况是不同的,例如,对一台PC配置后,其地址空间分配如下:

1)映射到局部配置寄存器的内存空间:E000H~E07FH。

2)映射到局部配置寄存器的I/O空间:E010H~E08FH。

3)映射到1KB双口RAM的内存空间:80000000H~800003FFH。

在设计完硬件电路后,要对智能适配器进行有关的PCI资源配置,PCI配置寄存器的初始值是由串行E2PROM提供的。

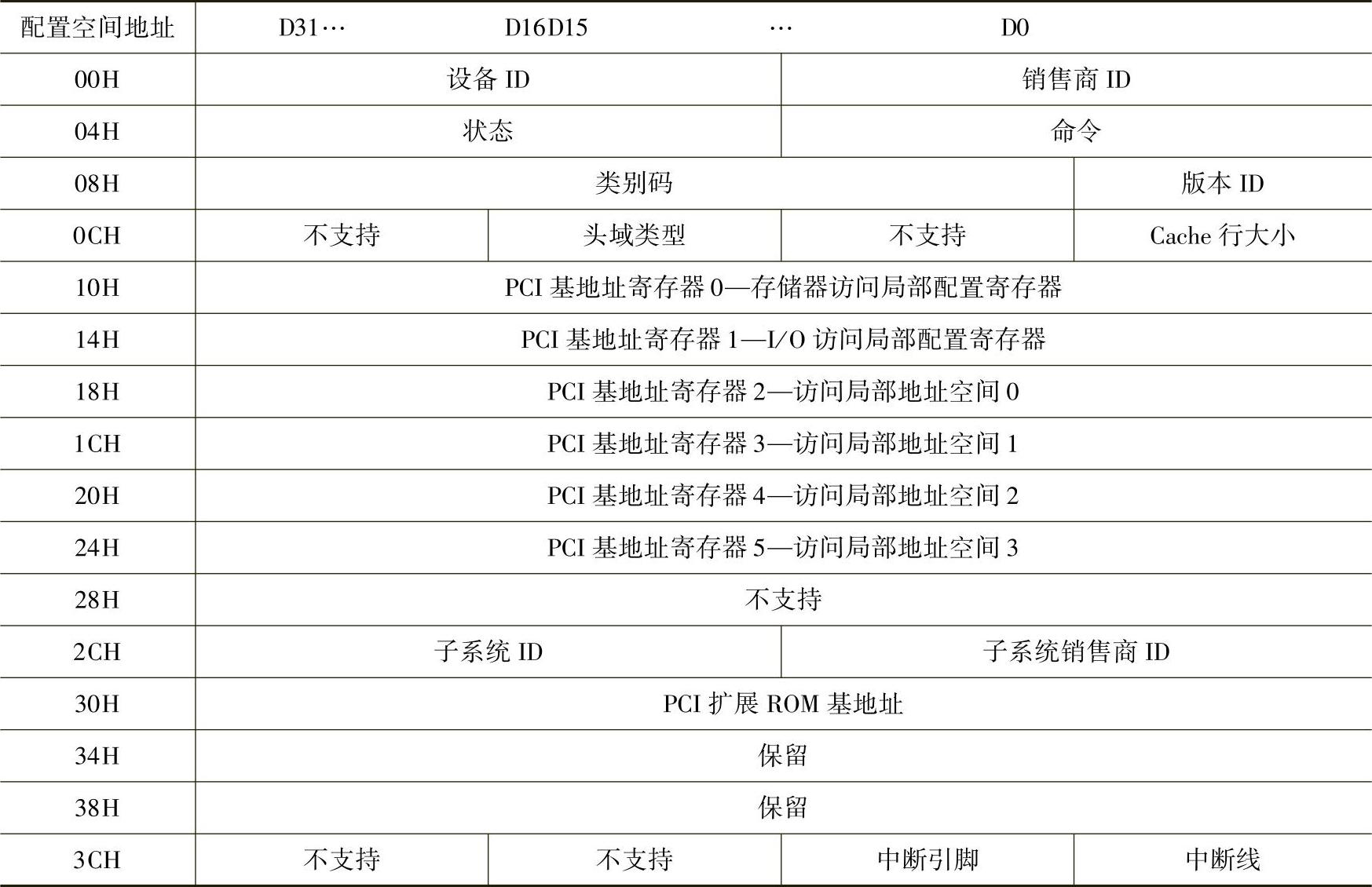

PCI9052上电后,将串行E2PROM的值读取到内部PCI配置寄存器和局部配置寄存器中。串行E2PROM要支持连续读功能,推荐使用93LC46B。串行E2PROM的值可以由编程器写入,也可以由PLX公司提供的PLXMon软件写入,PCI9052的配置空间寄存器见表5-15。

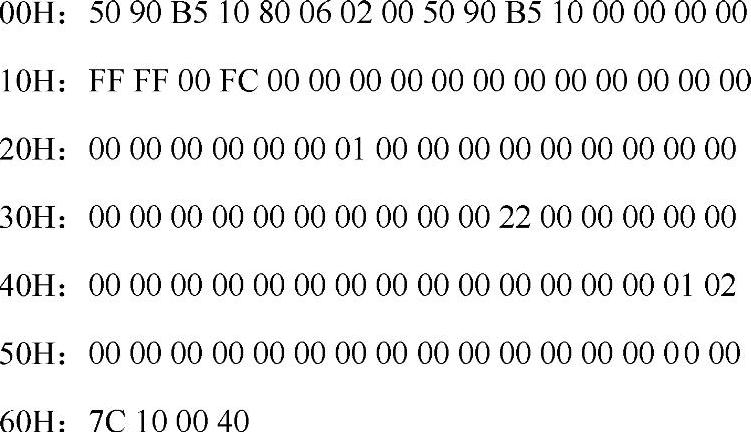

93LC46B中的内容如图5-36所示。

表5-15 PCI9052配置空间寄存器

图5-36 93LC46B数据格式

00H字单元中的9050是PLX公司给出的PCI9052的设备标识;02H字单元中的10B5是设备商标识符,随厂家不同而不同,这里是代表PLX公司;04H字单元中的0680是类别码,代表了桥设备的类型;06H字单元中的0002是代表PCI9052以区别于PCI9050;08H字单元中9050是此系统的标识符;0AH字单元中的10B5是此系统生产商标识符。

PCI9052有5个局部地址空间,可以任意选取。现选取Local Address Space 0扩展1KB的IDT7130,与其有关的寄存器有四个:PCI-to-Local地址空间范围0寄存器(10H~12H)规定了地址空间的大小,值为0xFFFFFC00,类型是不可预取的;PCI-to-Local Re-map地址空间范围0寄存器(24H~26H)的值为0x00000001,表明映射到内存空间;De-scriptors for Local Address Space 0寄存器(38H~3AH)规定了时序等,值为0x00000022;使用PCI9052的CS0#作为IDT 7130的片选信号,CS0#片选信号的起始地址和地址范围是由CS0#Base and Range寄存器(4CH~4EH)设置,值为0x00000201。

串行E2PROM、PCI9052初始化的控制寄存器(60H~62H)规定了是否遵从PCI r2.1协议等,值为0x107C4000。由于没有使用中断功能,与中断有关的寄存器的值设为0。其他的PCI-to-Local和CS片选信号相关的寄存器的值可以置为0。

PLX公司提供的PLXMon软件可以进行93LC46B的读写、局部配置寄存器和局部总线的读写,实现对配置资源的检验,方便了硬件的调试。

IDT7130的争用问题采用PCI9052的局部总线数据准备好信号LRDYi#来解决。神经元芯片TMPN3150只有同步工作方式,而PC只允许异步工作方式,在双方同时访问IDT7130芯片时,应优先满足神经元芯片的访问请求。当PCI总线访问IDT7130,同时神经元芯片也在访问时,则IDT7130在PC一侧的忙信号(/BUSY)变低,将此信号取反接至PCI9052的LRDYi#信号线,使PC自动插入若干等待周期,主动延长对IDT7130的访问。

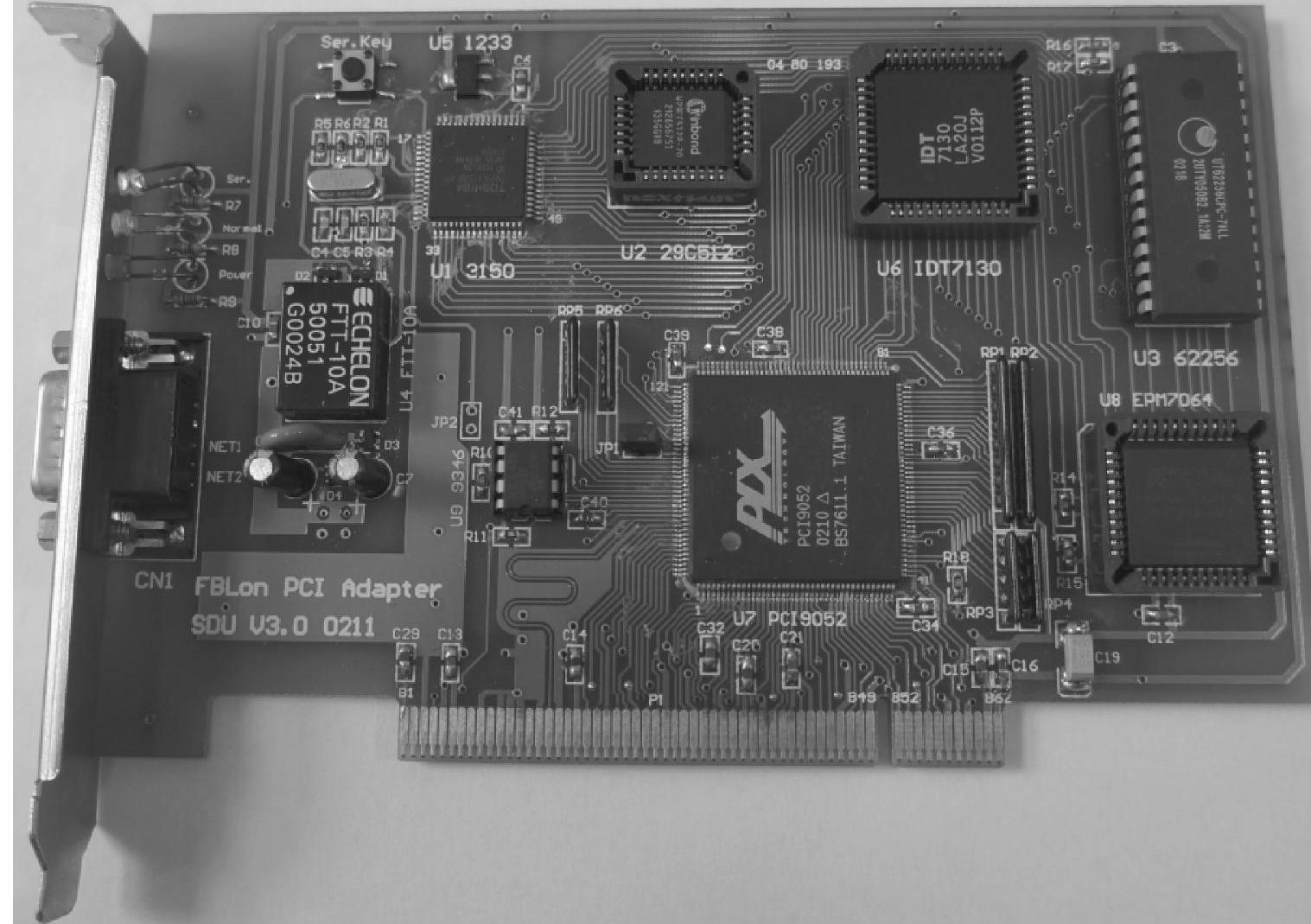

LON网络智能适配器以神经元芯片TMPN3150为核心,在设计中采用非易失性存储器FLASH(29C512)存放LonTalk协议固件、智能适配器通信管理程序以及网络配置信息,收发器采用多功能自由拓扑的FTT-10A,也可以根据实际的环境、速率等需要来选择不同的收发器。

LON网络智能适配器的外形如图5-37所示。

图5-37 LON网络智能适配器的外形

有关现场总线及其应用技术的文章

基金会现场总线,是在过程自动化领域得到广泛支持和具有良好发展前景的技术。屈于用户的压力,这两大集团于1994年9月合并,成立了现场总线基金会,致力于开发出国际上统一的现场总线协议。基金会现场总线分低速H1和高速H2两种通信速率。H1的传输速率为31.25 kbit/s,通信距离可达1900 m,可支持总线供电,支持本质安全防爆环境。H2总线标准也已形成。......

2023-11-22

PCI总线是由Intel公司提出的。PCI总线不是由ANSI通过的标准,但由于它是由厂家自发制定执行的标准,具有众多的优点,拥护者,执行者众多,成了事实上的标准。PCI总线共有100个引脚,如果只作为目标设备,至少需要47条,如作为主设备则需要49条。本设计使用位命令字,其定义如下:3.PCI总线基本协议PCI上的基本总线传输机制是突发成组传输。......

2023-11-22

现场总线控制网络处于企业网络的底层,或者说,它是构成企业网络的基础。从图中可以看出,除现场的控制网络外,上面的ERP和MES都采用以太网。图中的ERP与MES功能层大多采用以太网技术构成数据网络,网络节点多为各种计算机及外设。控制网络的主要作用是为自动化系统传递数字信息。这些都需要在现场控制层内部,在FCS与MES、ERP各层之间,方便地实现数据传输与信息共享。......

2023-11-22

INTERBUS定义了该模型的第1、2、7层。INTERBUS具有强大的可靠性、可诊断性和易维护性。INTERBUS采用了集总帧型的数据环通信。强大的诊断功能是INTERBUS区别于其他总线所独有的。INTERBUS CLUB负责向设备生产厂家提供INTERBUS的接口方案和接口芯片,向其成员提供信息,帮助解决技术问题及为特定的应用找寻合适的INTERBUS产品。INTERBUS的技术发起人为德国菲尼克斯公司。另外,在美国和中国也设有INTERBUS技术中心。......

2023-11-22

ControlNet是目前世界上增长最快的工业控制网络之一。因而,ControlNet是开放的现场总线。SIG开发的成果经过同行们审查再提交CI的技术审查委员会,经过批准,其设备行规将成为ControlNet技术规范的一部分。所有的这些现实问题推动了ControlNet的开发和发展,它正是满足不同需要的一种实时的控制层的网络。ControlNet协议的制定参照了OSI 7层协议模型,并参照了其中的1、2、3、4、7层。ControlNet中网络和传输层的任务是建立和维护连接。......

2023-11-22

功能块的算法由块的类型和控制参数确定。在一个功能块内参数的名字是唯一的。为了支持静态参数值跟踪,相关联的块将增加静态修订参数ST REV的值,而且每次静态参数值被修改后都被当作发生一次更新事件。由于这些参数的属性经常改变,所以它们通常不被组态设备所跟踪,即不改变ST REV的值。一个功能块的输入参数连接到其他某功能块的输出参数,并获得数据进行运算。......

2023-11-22

现场总线基金会于1998年开始起草HSE,2003年3月,完成了HSE的第一版标准。图1-27 HSE协议的体系结构HSE的物理层、数据链路层采用了100 Mbit/s标准。DHCP的目的就是在一个HSE系统里为现场设备动态地分配IP地址。SNTP主要用来监控HSE现场设备的物理层、数据链路层、网络层和传输层的运行情况。3)由HSE连接设备连接H1网段和HSE网段。......

2023-11-22

三种PROFIBUS均使用一致的总线存取协议。在PROFIBUS中,第二层称为现场总线数据链路层。因此,PROFIBUS总线存取协议,主站之间采用令牌传输方式,主站与从站之间采用主从方式。在PROFIBUS中,令牌传递仅在各主站之间进行。以3个主站7个从站构成的PROFIBUS系统为例。第二层的另一重要任务是保证数据的可靠性,PROFIBUS第二层的数据结构格式可保证数据的高度完整性。......

2023-11-22

相关推荐