PCI总线是由Intel公司提出的。PCI总线不是由ANSI通过的标准,但由于它是由厂家自发制定执行的标准,具有众多的优点,拥护者,执行者众多,成了事实上的标准。PCI总线共有100个引脚,如果只作为目标设备,至少需要47条,如作为主设备则需要49条。本设计使用位命令字,其定义如下:3.PCI总线基本协议PCI上的基本总线传输机制是突发成组传输。......

2023-11-22

1.简介

CY7C09449PV是Cypress公司生产的半导体PCI-DP系列的PCI接口控制器之一,它提供了可与多种常用的微处理器直接连接的PCI主/从接口,一个128 Kbit的双端口SRAM用作局部微处理器和PCI总线间的共享存储器。CY7C09449PV给设计者提供了一种将应用连接到PCI总线的简单方法。它同时提供一个I2O(Intelligent Input&Output)消息单元,具有消息队列和中断能力。

CY7C09449PV控制器的主要特点为:具有128 Kbit的双端口共享存储器;可以作为主设备和从设备接口使用,符合PCI 2.2规范;内置主桥能力;可以直接与多种微处理器接口;具有I2O信息传送单元,包括4个深度为32的FIFO;它的局部总线时钟频率最高可达50 MHz;采用单一3.3V电源供电,与3V和5V的PCI总线信号兼容。

2.功能说明

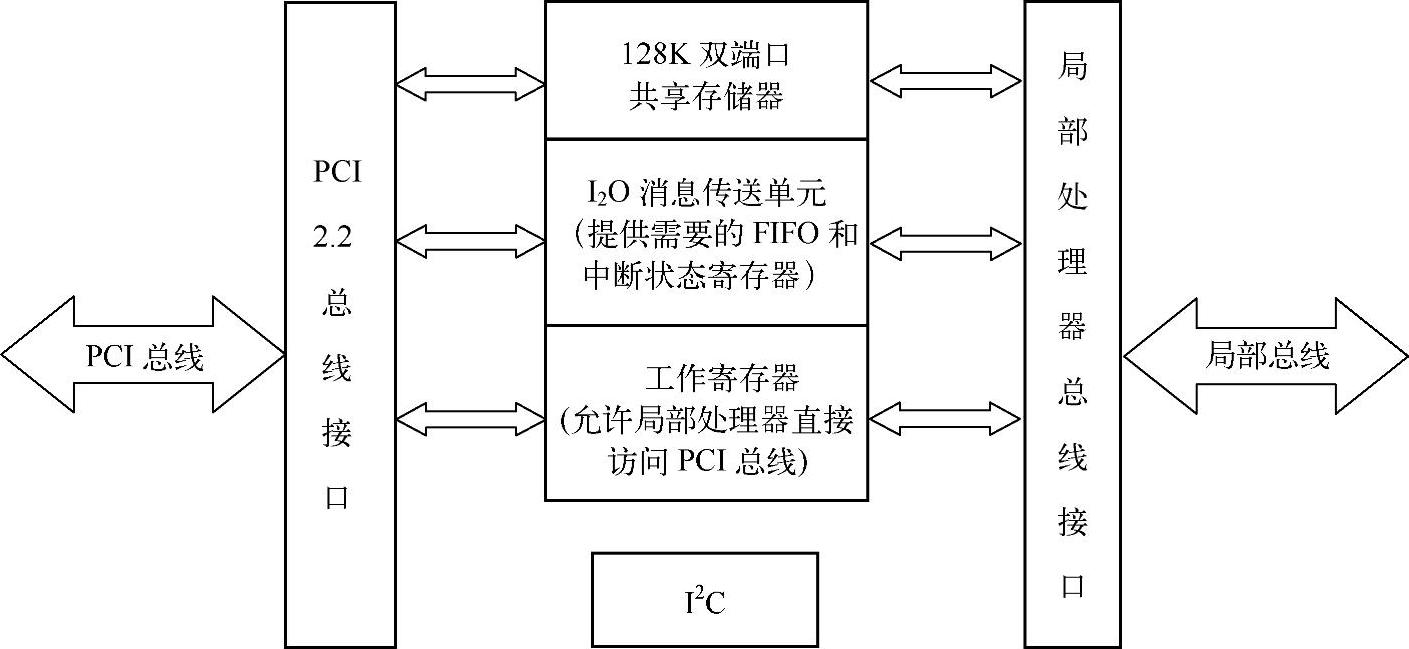

CY7C09449PV包括许多共享资源,它为局部总线和PCI总线之间进行高效的数据传输提供了通道。其结构如图4-39所示。

图4-39 CY7C09449结构示意图

CY7C09449PV内部基本的资源是一个128 Kbit的双端口存储器。这个存储器既可以连接到PCI总线上,又可以连接到局部微处理器总线上。这个共享存储器可同时被两个总线访问,用于过程间通信。

无论是局部总线还是PCI总线,CY7C09449PV都可以变成PCI总线的主设备作为直接存储器存取(DMA)将数据移入内部共享存储器或者将数据从内部共享存储器中移出。CY7C09449PV可以直接存取PCI总线的任意数量的32位双字(DWORD)数据,最多可达16KB。它使用PCI总线的最大突发能力以达到最大传输效率,并且可以在整个32位PCI寻址空间上传输数据。

CY7C09449PV作为PCI总线的主设备时,在每次交易中可以选择优化的PCI命令来实现相应的PCI请求。这种方式使系统平台的效率最大化。PCI的桥功能(PCI-PCI和HOST-PCI桥)使用提高了预存储和存储一致性的命令。CY7C09449PV可以作为任意主设备请求和访问PCI总线。但是,它自身并不包括PCI总线仲裁功能。标准PC的PCI总线包括这一功能,嵌入式系统可能需要实现这一功能。

CY7C09449PV提供了从局部总线直接访问PCI总线的机制。使用这一功能,局部处理器可以直接驱动CY7C09449PV来运行对任意地址空间的任何类型的PCI主设备周期。这就意味着CY7C09449PV能够运行PCI配置周期,可以用作主桥。

4个先入先出(FIFO)存储单元向用户提供了另一种资源。这些资源既可以从PCI总线也可以从局部总线进行访问。当使用CY7C09449PV的I2O消息单元功能时,4个FIFO就作为CY7C09449PV的I2O消息单元的一部分。I2O消息单元包括4个FIFO和I2O系统中断寄存器。CY7C09449PV的共享存储器可用来存储I2O消息帧缓冲,而其他的共享存储器仍可用于通常的操作。当局部处理器使用CY7C09449PV的直接访问机制时可以实现有效的I2O消息机制。它可用来接收和发送指向其他的I2O服务器的消息指针。

CY7C09449PV提供了可完成总线间通信的两个资源,即邮箱寄存器和仲裁标志。局部处理器可通过写邮箱寄存器引起主机中断的方法来传送数据,反之亦然。这一功能可通过CY7C09449PV操作寄存器的中断屏蔽来使能,仲裁标志是用来处理软件和系统过程之间的资源分配和共享的4对标志位。

CY7C09449PV包括一个中断控制器。它具有用于PCI总线和局部总线的中断屏蔽和命令/状态寄存器。中断源包括DMA完成、邮箱、FIFO不空、FIFO溢出、PCI主设备异常和PCI从设备异常,并且具有一个外部中断输入引脚。中断控制器用来表明到PCI总线和局部总线的中断。CY7C09449PV中断控制器没有实现PCI总线系统的中断控制器功能。标准PC的PCI总线包含了这些功能,嵌入式系统可能需要实现这些功能。

通过I2C串行接口可使用非易失性的串行E2PROM来存储CY7C09449PV的初始化参数。这些参数是PCI配置和局部总线设置参数。在响应PCI总线或局部总线交易前,CY7C09449PV在复位和装入初始化参数后可访问E2PROM。当通过这一接口方式连接时,主机和局部处理器可访问各种各样的I2C串行设备。

CY7C09449PV的局部总线具有柔性的、可配置的接口,可与多种工业标准微处理器接口。大多数情况下,不需要外部接口逻辑(即“无缝连接”)。

3.信号终结

PCI总线信号应按PCI2.2规范终结。通常终结是由PCI系统提供。如果CY7C09449PV被用于插卡或者其他设备作为PCI总线的一部分时,就不能使用终结。对于嵌入式系统来说,终结是系统设计的一部分,而不是CY7C09449PV的一部分。任何的PCI系统在所使用的每一个PCI总线控制信号都必须加上一个上拉。这些信号是/FRAME、/IRDY、/TRDY、/DEVSEL、/STOP、/SERR、/PERR、/LOCK、/INTA、/INTB、/INTC、/INTD、/REQ64和/ACK64。具体的要求参考PCI2.2规范的4.3部分———系统(主板)规范。

所有的局部系统和局部总线接口的输入信号必须始终被驱动。没有使用的输入引脚必须被驱动为高或者低(上拉为VDD,或下拉为Ground)。SCL和SDA必须用2.2~10kΩ的上拉电阻接到VDD上。无论这些信号是否使用都要连接上拉电阻。

4.存储器映射

CY7C09449PV的内部资源见表4-21。

表4-21 存储器映射示意图(www.chuimin.cn)

PCI总线从基址寄存器0(BAR0)指定的偏移处开始访问CY7C09449PV资源,除非有其他的说明。当SELECT#引脚有效时,也可从局部总线访问这些资源。PCI I/O也可通过基址寄存器1(BAR1)指定的PCI I/O指针来访问这些存储器映射。存储器映射占有连续的32KB地址空间。

5.PCI总线的配置空间

CY7C09449PV的PCI总线工作在PCI规范2.2版。本节主要介绍PCI配置空间中的几个将在本系统中使用到的寄存器。

CY7C09449PV的PCI配置空间大小为256B,其各个寄存器的名称和偏移量如图4-40所示。

售方(Vendor)ID和设备(Device)ID寄存器中均为只读寄存器,存储的值为主机系统识别设备的标号,其中Vendor ID的默认值为0x12BE,Device ID的默认值为0x3042。

另外两个重要的寄存器是内存空间基地址寄存器BAR0(Base Address Register 0(Mem-ory Type Access))和I/O空间基地址寄存器BAR1(Base Address Register 1(I/O Type Ac-cess))寄存器,它们均为标准的PCI基地址寄存器,分别存储了由主机(Windows)系统自动分配的内存空间和I/O空间的基地址。BAR0和BAR1的内容默认为0x00000000和0x00000001。

由于CY7C09449PV可以向主机发送中断,所以Windows还会分配一个中断号,存储在中断引脚(Interrupt Pin)寄存器中。

6.局部总线

CY7C09449PV提供了可以与几个处理器类型直接连接的可配置的局部处理器总线接口。这个接口通过CLKIN信号同步。CLKIN信号可以连接到一个局部处理器、PCI时钟的一个缓冲输出或者一个独立的时钟源。为了在PCI时钟频率下运行局部接口,可以将PCLKOUT[2:0]引脚的任意一个连接到CLKIN上。

图4-40 PCI配置空间示意图

基本的局部处理器总线交易包括一个地址周期,紧接着是一个或多个数据周期。接口信号通常分为与地址周期相匹配的信号(ALE、/STROBE、/SELECT、/READ、/WRITE与ADR[14:2])以及与数据周期相匹配的信号(/RDY IN、RDY IN、/BLAST、/BE[3:0]与DQ[31:0])。CY7C09449PV驱动/RDY OUT来表明局部处理器总线需要一个等待周期,同时也暗示在读访问CY7C09449PV时DQ[31:0]上的数据有效。请注意:某些CY7C09449PV局部总线信号的极性可以配置。它们是ALE、/BLAST、/RDY OUT和/STROBE。同时/READ和/WRITE信号也具有特殊的信号组合方式。

基本局部总线时钟周期是从地址周期开始的。地址周期是在CLKIN的上升沿/STROBE和/SELECT信号都有效时定义的。同时,对/READ和/WRITE信号进行采样以确定这次访问是读操作还是写操作。如果这次访问是读操作,那么在CLKIN的下一个上升沿,CY7C09449PV开始驱动DQ总线。

有两种方法可以获取输入到CY7C09449PV的地址。第一种方法是当ALE信号始终有效时,地址在地址周期被锁存。即当/STROBE和/SELECT信号有效时,在CLKIN的上升沿锁存在ADR[14:2]引脚上的地址。第二种方法是用ALE信号的下降沿来锁存地址。CY7C09449PV在处理地址之前仍需要一个有效的地址周期(在CLKIN的上升沿/STROBE和/SELECT信号都有效)。当/STROBE和/SELECT信号都有效时,在CLKIN的上升沿和ALE信号的下降沿之前地址信号必须是有效和稳定的。

地址周期后是等待周期和数据周期。在等待周期和数据周期,/STROBE可能是有效的,也可能是无效的。在CLKIN的上升沿,当输入信号RDY IN和/RDY IN及输出信号RDY OUT都有效时,就产生数据周期。如果任一个准备好信号是无效的,那么下一个时钟周期就是等待周期。在写周期的数据周期将采样/BE[3:0]的引脚以确定要写入哪些数据字节,同时锁存DQ引脚上的数据。

在数据周期将会采样/BLAST信号判断是否是最后一个数据周期。一种模式下,在地址周期该信号是无效的,表明在传输过程中有更多的数据周期,并且在地址周期捕获的地址必须要不断地更新;在数据周期该信号是有效的,表明这是传输过程的最后一个数据周期。另一种模式下,/BLAST信号在每个周期都是有效的,在最后一个数据周期变为无效状态。在这两种情况下,如果存取操作是读操作,CY7C09449PV都会在数据周期的/CLKIN的上升沿同步停止驱动DQ总线,为数据周期做准备。

8位接口是通过置局部总线配置寄存器的BW[1:0]=“00”来选择的。只用了数据总线的DQ[7:0]。数据总线中未被使用的引脚DQ[31:8]必须被置为低电平或高电平而不能悬空。局部地址总线的最低两位应接到字节使能引脚/BE[3:2]上。连接方式如下:/BE[3]=A1,/BE[2]=A0,/BE[1]接逻辑高电平,/BE[0]接/RDY IN信号。

注意:只使用了数据线DQ[7:0],未使用的DQ[31:8]必须被置为低电平或高电平而不能悬空。局部地址总线的最低两位A1和A0必须分别连接到字节使能引脚/BE[3]和/BE[2]上。在地址周期它们必须有效。

在突发操作中,BE#[3:2]用局部总线的A0和A1作为输入。8位接口的突发方式不需要从一个DWORD的边界开始。在一个/BE[3:2]等于11(A[1:0]=“11”)的数据周期之后,内部DWORD地址将会自动增加。

有关现场总线及其应用技术的文章

PCI总线是由Intel公司提出的。PCI总线不是由ANSI通过的标准,但由于它是由厂家自发制定执行的标准,具有众多的优点,拥护者,执行者众多,成了事实上的标准。PCI总线共有100个引脚,如果只作为目标设备,至少需要47条,如作为主设备则需要49条。本设计使用位命令字,其定义如下:3.PCI总线基本协议PCI上的基本总线传输机制是突发成组传输。......

2023-11-22

基金会现场总线,是在过程自动化领域得到广泛支持和具有良好发展前景的技术。屈于用户的压力,这两大集团于1994年9月合并,成立了现场总线基金会,致力于开发出国际上统一的现场总线协议。基金会现场总线分低速H1和高速H2两种通信速率。H1的传输速率为31.25 kbit/s,通信距离可达1900 m,可支持总线供电,支持本质安全防爆环境。H2总线标准也已形成。......

2023-11-22

INTERBUS定义了该模型的第1、2、7层。INTERBUS具有强大的可靠性、可诊断性和易维护性。INTERBUS采用了集总帧型的数据环通信。强大的诊断功能是INTERBUS区别于其他总线所独有的。INTERBUS CLUB负责向设备生产厂家提供INTERBUS的接口方案和接口芯片,向其成员提供信息,帮助解决技术问题及为特定的应用找寻合适的INTERBUS产品。INTERBUS的技术发起人为德国菲尼克斯公司。另外,在美国和中国也设有INTERBUS技术中心。......

2023-11-22

WorldFIP技术硬件体系由两个互补的部分组成:通信控制器和通信介质器件。5)用于WorldFIP连接的费用要求。WorldFIP现场总线第一个通信控制器是在1987年开发成功的。图8-9 WorldFIP现场总线通信站的连接......

2023-11-22

西门子为PLC之间简单高速的数字通信提供用户ASICs。参照PROFIBUS DIN 19245第一部分和第三部分设计的这些ASICs,支持并可以完全处理PLC站之间的数据通信。下列的ASICs与微处理器结合可提供智能从站的解决方案:SPC的设计基于OSI参考模型的第一层,需要附加一个微处理器用于实现第二层和第七层的功能。另一种称作LSPM2/SPM2的ASICs是适应这些设备的低成本改造。主站在七层模型的第二层寻址这些ASICs,两个ASICs收到正确的报文后,自动生成所要求的响应报文。......

2023-11-22

因此FF的通信控制器,一定要具备发送帧前引导序列,发送和识别帧前、帧后界定符的能力。通信控制器通过相应的状态位将接收数据是否正确通知CPU,由CPU决定本帧数据的取舍。以上所列几项的要求是FF通信控制器必需的。......

2023-11-22

现场总线报文规范层FMS是基金会现场总线通信模型中应用层的另一个子层。FMS提供了一组服务和标准的报文格式。与OD描述联系在一起,FMS为现场设备应用程序规定了功能性界面。现场总线报文规范层由以下几部分组成:虚拟现场设备、对象字典管理、联系关系管理、域管理、程序调用管理、动态参数管理和时间管理。由用户层监测导致事件发生的条件,当条件发生时,该应用程序激活事件通知服务,并由使用者确认。......

2023-11-22

IDA是一种完全建立在以太网基础上的工业以太网规范,它将一种实时的基于Web的分布自动化环境与集中的安全体系结构加以结合,目标是创立一个基于TCP/IP的分散自动化的解决方案。作为一个单纯的工业以太网协议,IDA涵盖自动化结构中所有层次,包括设备层。因为ModBus TCP/IP是完全透明的,所以很好地符合IDA。IDA协议建立在组件的基础上,该组件包括了IEC 61449的第一部分体系结构功能块标准,但用IDA的体系结构替代了IEC 61499的模型。IDA的协议栈如图1-18所示。......

2023-11-22

相关推荐