BasicCAN地址分配见表4-3。表4-3 BasicCAN地址分配表(续)2.控制段控制寄存器控制寄存器的内容是用于改变CAN控制器的状态。然而,数据长度码必须正确设置以避免两个CAN控制器用同样的识别机制启动远程帧传送而发生总线错误。如果选择的值超过8,则按照DLC规定认为是8。当复位请求位出现了1到0的变化时,CAN控制器将返回操作模式。......

2023-11-22

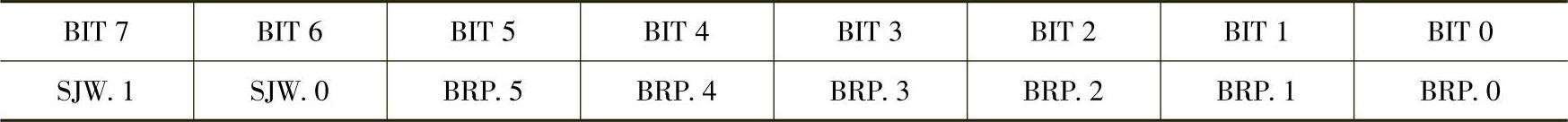

1.总线时序寄存器0

总线时序寄存器0(BTR0)见表4-12,定义了波特率预置器(Baud Rate Prescaler,BRP)和同步跳转宽度(SJW)的值。复位模式有效时,这个寄存器是可以被访问(读/写)的。

表4-12 总线时序寄存器0(地址6)

如果选择的是PeliCAN模式,此寄存器在操作模式中是只读的。在BasicCAN模式中总是“FFH”。

(1)波特率预置器位域

位域BRP使得CAN系统时钟的周期tSCL是可编程的,而tSCL决定了各自的位定时。CAN系统时钟由如下公式计算:

式中,tCLK=XTAL的振荡周期=1/fXTAL。

(2)同步跳转宽度位域

为了补偿在不同总线控制器的时钟振荡器之间的相位漂移,任何总线控制器必须在当前传送的任一相关信号边沿重新同步。同步跳转宽度tSJW定义了一个位周期可以被一次重新同步缩短或延长的时钟周期的最大数目,它与位域SJW的关系是

tSJW=tSCL×(2×SJW.1+SJW.0+1)

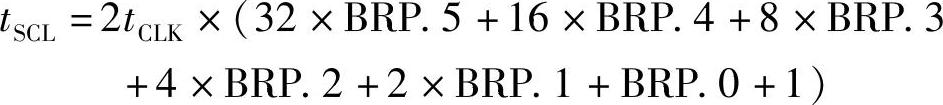

2.总线时序寄存器1

总线时序寄存器1(BTR1)见表4-13,定义了一个位周期的长度、采样点的位置和在每个采样点的采样数目。在复位模式中,这个寄存器可以被读/写访问。在PeliCAN模式的操作模式中,这个寄存器是只读的。在BasicCAN模式中总是“FFH”。

表4-13 总线时序寄存器1(地址7)

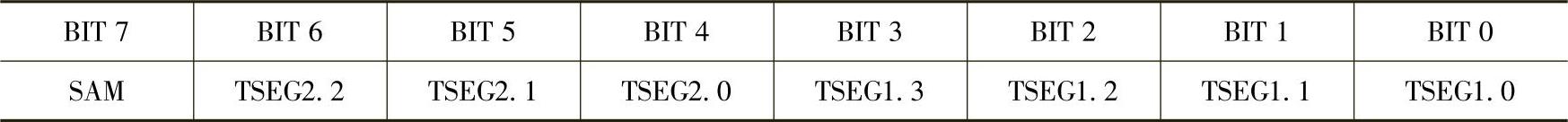

(1)采样位

采样位(SAM)的功能说明见表4-14。

表4-14 采样位的功能说明

(2)时间段1和时间段2位域

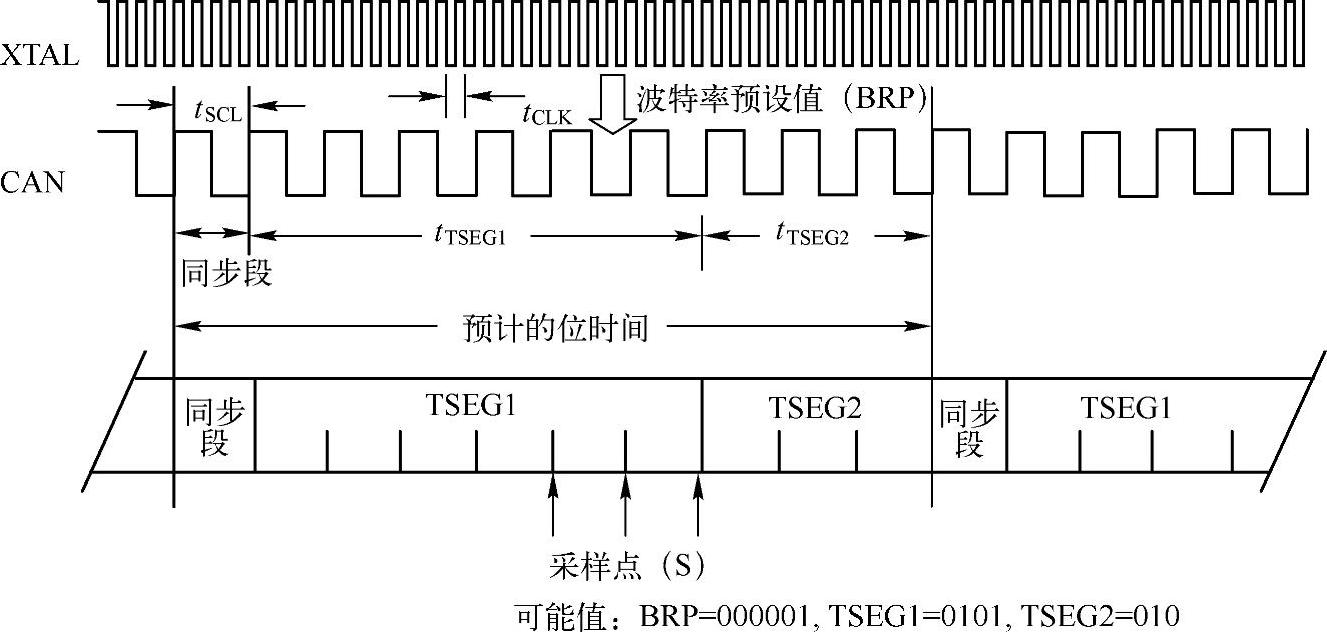

时间段1(TSEG1)和时间段2(TSEG2)决定了每一位的时钟周期数目和采样点的位置,如图4-18所示,这里:

tSYNCSEG=1×tSCL

tTSEG1=tSCL×(8×TSEG1.3+4×TSEG1.2+2×TSEG1.0+1)

tTSEG2=tSCL×(4×TSEG2.2+2×TSEG2.1+TSEG2.1+1)

图4-18 位周期的总体结构

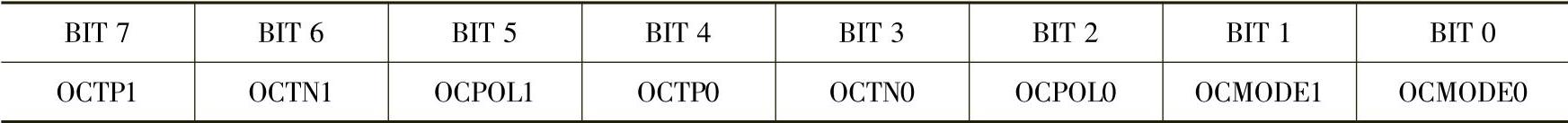

3.输出控制寄存器

输出控制寄存器(OCR)见表4-15,允许由软件控制建立不同输出驱动的配置。在复位模式中此寄存器可被读/写访问。在PeliCAN模式的操作模式中,这个寄存器是只读的。在BasicCAN模式中总是“FFH”。

表4-15 输出控制寄存器(地址8)

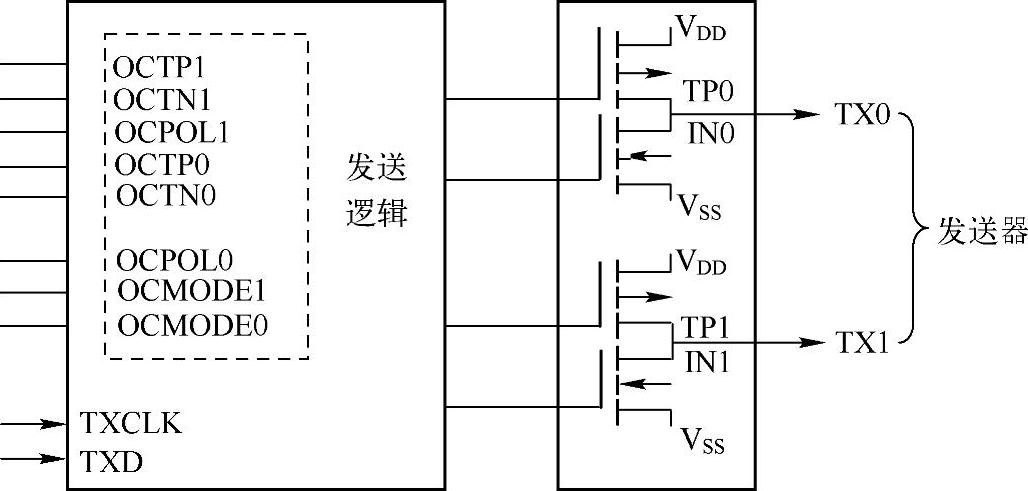

收发器的输入/输出控制逻辑如图4-19所示。

图4-19 收发器的输入/输出控制逻辑

当SJA1000在睡眠模式中时,TX0和TX1引脚根据输出控制寄存器的内容输出隐性的电平。在复位状态(复位请求=1)或外部复位引脚  被拉低时,输出TX0和TX1悬空。

被拉低时,输出TX0和TX1悬空。

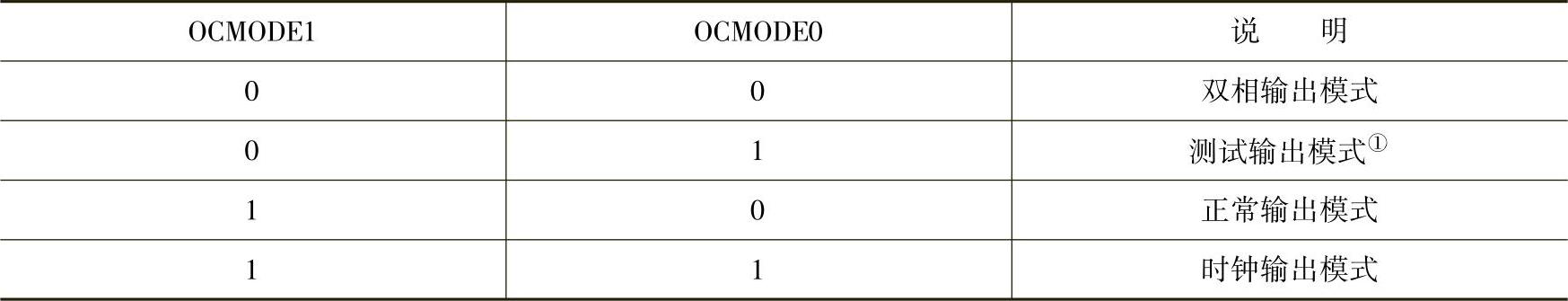

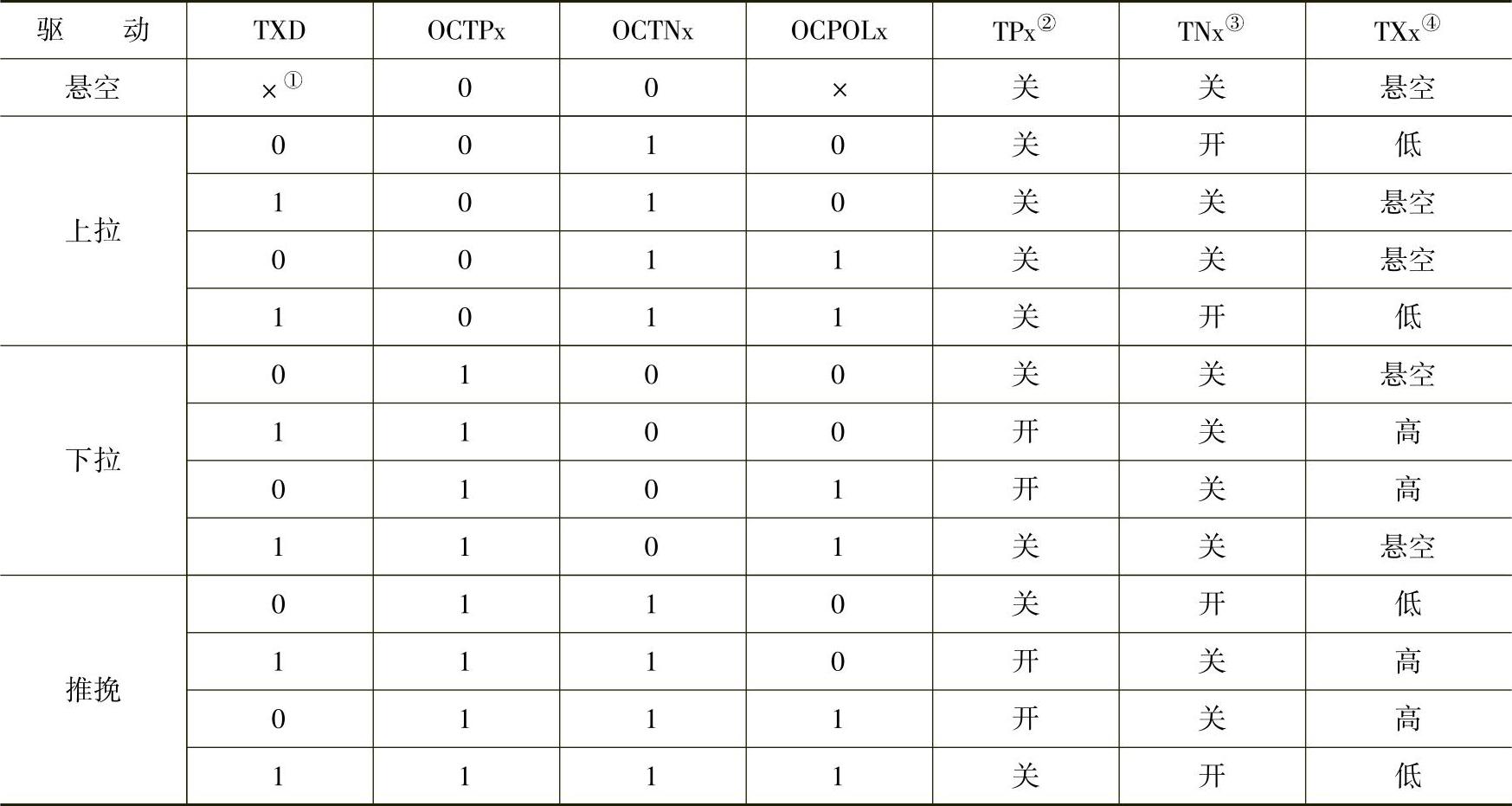

发送的输出阶段可以有不同的模式。输出控制寄存器OCMODE位的设置见表4-16。

表4-16 OCMODE位的说明

(www.chuimin.cn)

(www.chuimin.cn)

①测试输出模式中,TXx会在系统时钟的下一次上升沿反映出在RX引脚检测到的位。TN1、TN0、TP1和TP0配置同OCR相对应。

(1)正常输出模式

正常模式中位序列(TXD)通过TX0和TX1送出。输出驱动引脚TX0和TX1的电平取决于被OCTPx、OCTNx(悬空、上拉、下拉、推挽)编程的驱动器的特性和被OCPOLx编程的输出端极性。

(2)时钟输出模式

TX0引脚在这个模式中和正常模式中是相同的。然而,TX1上的数据流被发送时钟(TXCLK)取代。发送时钟(非翻转)的上升沿标志着一个位周期的开始。时钟脉冲宽度是1×tSCL。

(3)双相输出模式

与正常输出模式相反,这里位的表现形式是时间的变量而且会反复。如果总线控制器被发送器从总线上电流退耦,则位流不允许含有直流成分。这一点由下面的方案实现:在隐性位期间所有输出呈现“无效”(悬空),而显性位交替在TX0和TX1上发送,即第一个显性位在TX0上发送,第二个在TX1上发送,第三个在TX0上发送等,以此类推。

(4)测试输出模式

在测试输出模式中,在下一次系统时钟的上升沿RX上的电平反映到TXx上,系统时钟(fOSC/2)与输出控制寄存器中编程定义的极性相对应。输出控制寄存器的位和输出引脚TX0和TX1的关系见表4-17。

表4-17 输出引脚配置

①×=不影响。

②TPx是片内输出发送器X,连接VDD。

③TNx是片内输出发送器X,连接VSS。

④TXx是在引脚TX0或TX1上的串行输出电平。要求当TXD=0时,CAN总线上的输出电平是显性,而当TXD=1时,这个输出电平是隐性。

位序列(TXD)通过TX0和TX1发送。输出驱动器引脚上的电平取决于被OCTPx、OCTNx(悬空、上拉、下拉、推挽)编程的驱动器的特性和被OCPOLx编程的输出端极性。

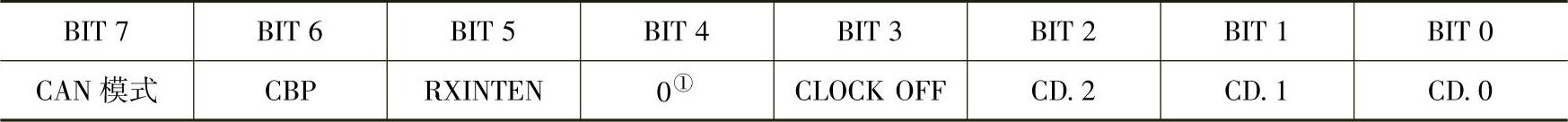

4.时钟分频寄存器

时钟分频寄存器(CDR)控制输出给微控制器的CLKOUT频率,它可以使CLKOUT引脚失效。另外,它还控制着TX1上的专用接收中断脉冲、接收比较器旁路和BasicCAN模式与PeliCAN模式的选择。硬件复位后寄存器的默认状态是Motorola模式(00000101,12分频)和Intel模式(00000000,2分频)。

软件复位(复位请求/复位模式)或总线关闭时,此寄存器不受影响。

保留位(CDR.4)总是0。应用软件应向此位写0,目的是与将来可能使用此位的特性兼容。

时钟分频寄存器(CDR)各位的说明见表4-18。

表4-18 时钟分频寄存器(地址31)

①此位不能写。读值总为0。

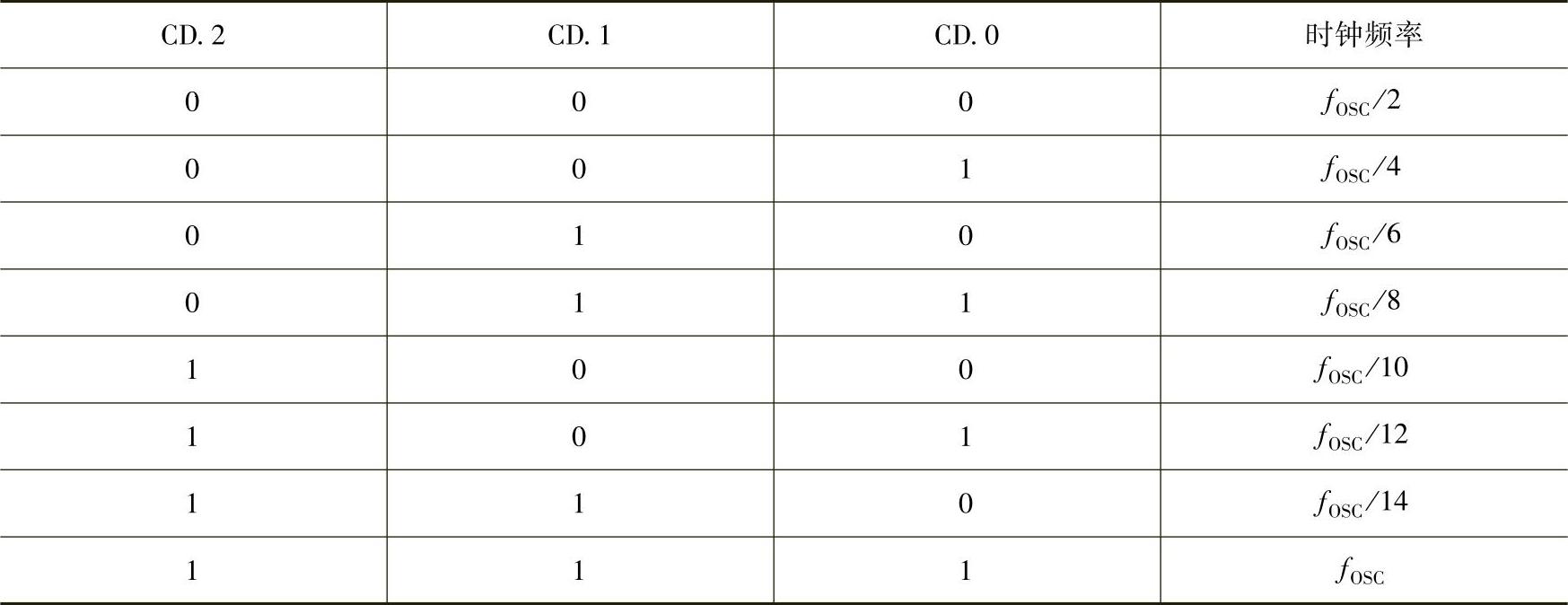

(1)位域CD.2~CD.0的定义

无论在复位模式还是在操作模式中,CD.2~CD.0都是可以随意访问。这些位是用来定义外部CLKOUT引脚上的频率的。可选频率见表4-19。

表4-19 CLKOUT频率选择

表4-19中,fOSC是外部振荡器(XTAL)频率。

(2)时钟关闭位

时钟关闭位(CLOCK OFF)置1使SJA1000的外部CLKOUT引脚失效。只有在复位模式中才可以写访问(在BasicCAN模式中复位请求位设置为1)。如果此位置1,则CLKOUT引脚在睡眠模式中是低而其他情况下是高。

(3)位RXINTEN

此位允许TX1输出用来做专用接收中断输出。当一条已接收的报文成功地通过验收滤波器时,一个位时间长度的接收中断脉冲就会在TX1引脚输出(在帧的最后一位期间)。极性和输出驱动可以通过输出控制寄存器编程。在复位模式中只能写(在BasicCAN模式中复位请求位设置为1)。

(4)位CBP

置位CDR.6(CBP)可以旁路CAN输入比较器,但这只能在复位模式中设置。这主要用于SJA1000外接发送接收电路时。此时内部延时被减少,这将使总线长度最大可能地增加。如果CBP被置位,只有RX0起作用。没有被使用的RX1输入应被连接到一个确定的电平,如Vss。

(5)位CAN模式

位CDR.7定义CAN模式。如果CDR.7是0,CAN控制器工作于BasicCAN模式;否则,CAN控制器工作于PeliCAN模式。只有在复位模式中可以写此位。

有关现场总线及其应用技术的文章

BasicCAN地址分配见表4-3。表4-3 BasicCAN地址分配表(续)2.控制段控制寄存器控制寄存器的内容是用于改变CAN控制器的状态。然而,数据长度码必须正确设置以避免两个CAN控制器用同样的识别机制启动远程帧传送而发生总线错误。如果选择的值超过8,则按照DLC规定认为是8。当复位请求位出现了1到0的变化时,CAN控制器将返回操作模式。......

2023-11-22

当激活错误状态的条件正常化后,错误状态被清除,功能块回到正常运行状态。警报状态可能通过设定相应的等级被个别禁止。标签是报警状态被检出但还未被报告的瞬间。直到警报确认收到前,它是一个常数。列举被报告警报的原因列表。报警状态一直维持到数值小于极限值减去报警回差。......

2023-11-22

基金会现场总线,是在过程自动化领域得到广泛支持和具有良好发展前景的技术。屈于用户的压力,这两大集团于1994年9月合并,成立了现场总线基金会,致力于开发出国际上统一的现场总线协议。基金会现场总线分低速H1和高速H2两种通信速率。H1的传输速率为31.25 kbit/s,通信距离可达1900 m,可支持总线供电,支持本质安全防爆环境。H2总线标准也已形成。......

2023-11-22

PCI总线是由Intel公司提出的。PCI总线不是由ANSI通过的标准,但由于它是由厂家自发制定执行的标准,具有众多的优点,拥护者,执行者众多,成了事实上的标准。PCI总线共有100个引脚,如果只作为目标设备,至少需要47条,如作为主设备则需要49条。本设计使用位命令字,其定义如下:3.PCI总线基本协议PCI上的基本总线传输机制是突发成组传输。......

2023-11-22

对于报文发送器和接收器,报文的实际有效时刻是不同的。标志数据帧和远程帧的起始,它仅由一个显性位构成。每个数据帧和远程帧均由7个隐性位组成的标志序列界定。......

2023-11-22

INTERBUS定义了该模型的第1、2、7层。INTERBUS具有强大的可靠性、可诊断性和易维护性。INTERBUS采用了集总帧型的数据环通信。强大的诊断功能是INTERBUS区别于其他总线所独有的。INTERBUS CLUB负责向设备生产厂家提供INTERBUS的接口方案和接口芯片,向其成员提供信息,帮助解决技术问题及为特定的应用找寻合适的INTERBUS产品。INTERBUS的技术发起人为德国菲尼克斯公司。另外,在美国和中国也设有INTERBUS技术中心。......

2023-11-22

存储和访问设备配置数据的方法包括输出数据文档的打印、电子数据文档、参数对象以及参数对象存根、EDS和参数对象存根的结合。图7-47所示的设备配置采用了支持EDS的配置工具。设备中的应用对象表示配置数据的目的地址,这些地址在EDS中编码。电子数据文档EDS除了包括该规范定义的、必需的设备参数信息外,还可以包括供应商特定的信息。目前,EDS中的文本信息必须是ASCII表示的字符。......

2023-11-20

WorldFIP技术硬件体系由两个互补的部分组成:通信控制器和通信介质器件。5)用于WorldFIP连接的费用要求。WorldFIP现场总线第一个通信控制器是在1987年开发成功的。图8-9 WorldFIP现场总线通信站的连接......

2023-11-22

相关推荐