【摘要】:DM9000A的16位模式和8位模式分别如图8-22和图8-23所示,图8-22 DM9000A的16位模式DM9000A引脚功能说明如下:1.电源引脚VDD:23、30、42引脚,数字电源,3.3V电源输入。图8-23 DM9000A的8位模式3.8位模式引脚WAKE:22引脚,唤醒事件发生时发出一个唤醒信号。LED3:24引脚,全双工LED。GP1~GP3:28、29、31引脚,通用I/O引脚。在E2PROM的16位模式设置中,该引脚还作为ISA总线的IO16。EECS:21引脚,数据总线宽度。

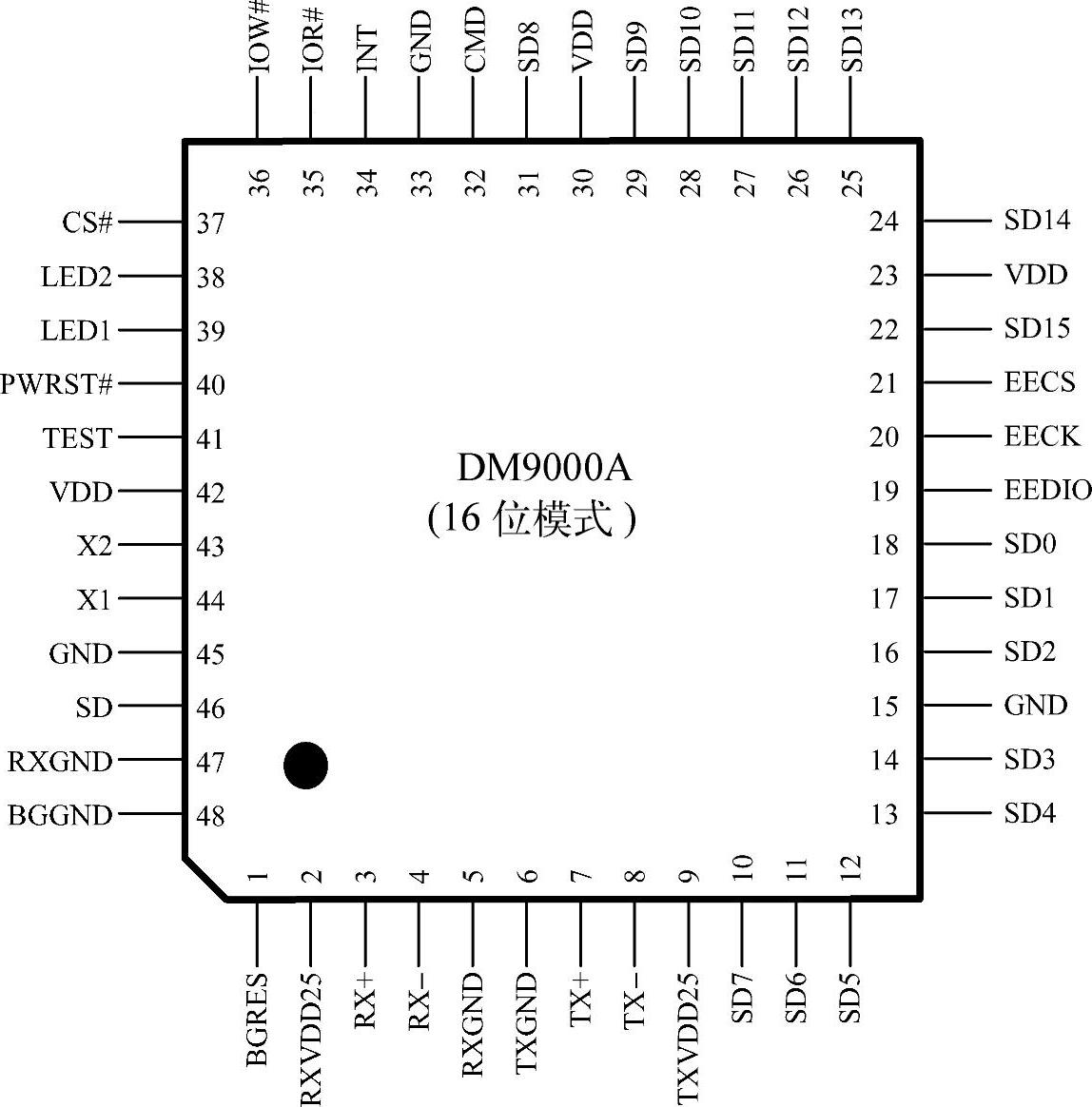

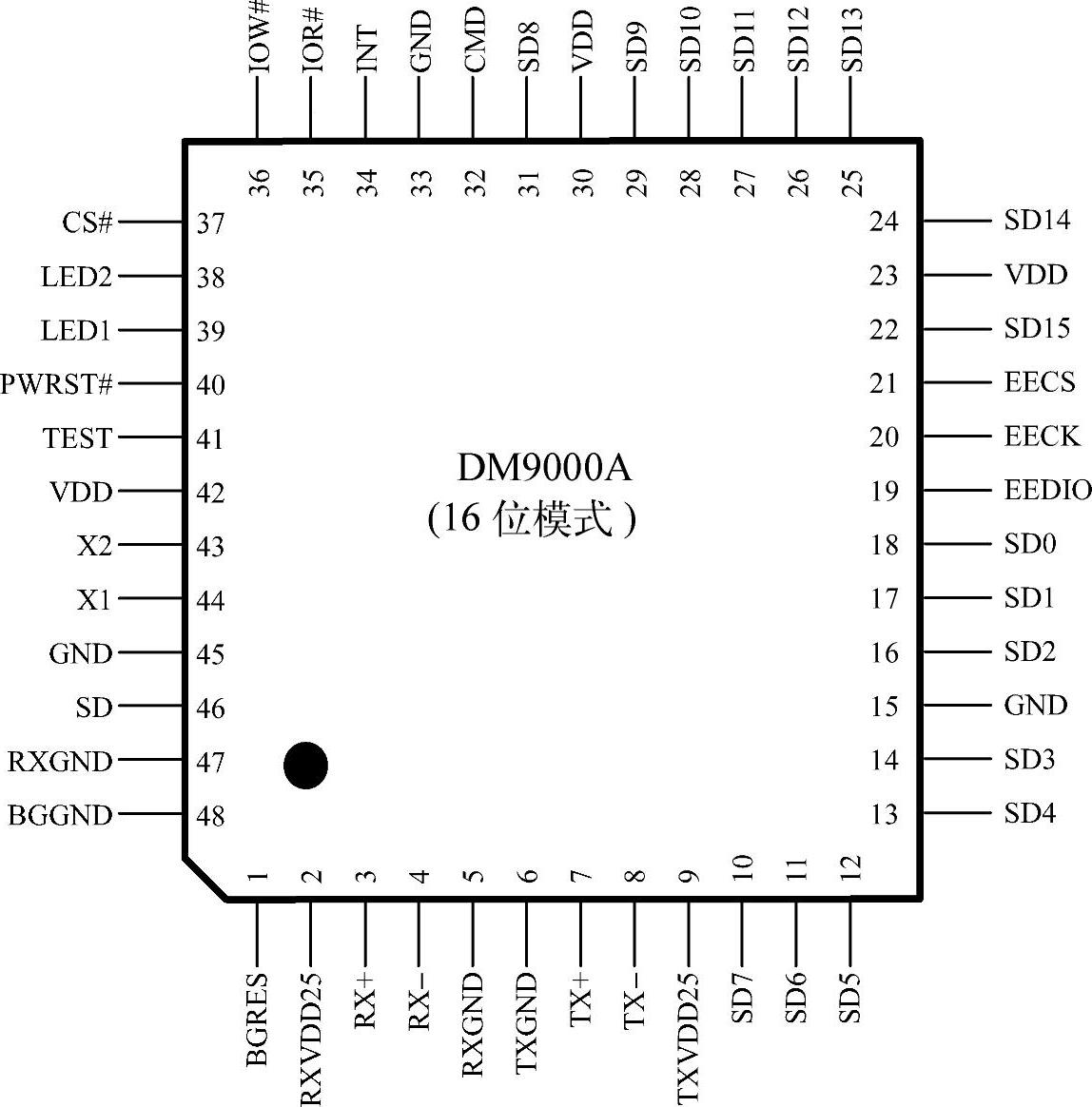

DM9000A的16位模式和8位模式分别如图8-22和图8-23所示,

图8-22 DM9000A的16位模式

DM9000A引脚功能说明如下:

1.电源引脚

VDD:23、30、42引脚,数字电源,3.3V电源输入。

GND:15、33、45引脚,数字地。

2.处理器接口

IOR#:35引脚,处理器读指令,低电平有效,极性可通过E2PROM设定改变。

IOW#:36引脚,处理器写指令,低电平有效,极性可通过E2PROM设定改变。

CS#:37引脚,片选信号,低电平有效,极性可通过E2PROM设定改变。

CMD:32引脚,访问类型,高电平时访问数据端口;低电平时访问地址端口。

INT:34引脚,中断请求信号,高电平有效,极性可通过E2PROM或引脚EECK设定改变。

SD0~SD7:10~14、16~18引脚,处理器数据总线0~7。

SD8~SD15:22、24~29、31引脚,处理器数据总线8~15。16位模式下,这些引脚为处理器数据总线8~15;当EECS引脚被上拉时,这些引脚为其他定义。

图8-23 DM9000A的8位模式

3.8位模式引脚

WAKE:22引脚,唤醒事件发生时发出一个唤醒信号。

LED3:24引脚,全双工LED。LED模式1,低电平输出表示内部PHY工作在全双工模式,悬空表示内部PHY工作在半双工模式;LED模式0,低电平输出表示内部PHY工作在10M模式,悬空表示内部PHY工作在100M模式。LED模式由E2PROM设置。

GP4~GP6:25~27引脚,通用输出引脚。该系列引脚通过通用寄存器(1FH)设置为通用输出引脚。GP6引脚也作为INT输出类型的捆绑引脚:当GP6被上拉置高,INT为开漏输出类型;否则被强制为输出型。

GP1~GP3:28、29、31引脚,通用I/O引脚。该系列引脚可由通用控制寄存器和通用寄存器编程设置。默认为输入引脚。

4.E2PROM接口引脚

EEDIO:19引脚,E2PROM数据输入/输出引脚。

EECK:20引脚,E2PROM时钟信号。该引脚也被用于设置中断引脚极性。当此引脚上拉时,中断引脚低有效,否则高有效。

EECS:21引脚,E2PROM片选信号。此引脚也被用于设置内部存储器数据总线的宽度。当此引脚上拉高电平时,总线宽度为8位,否则为16位。

5.时钟接口引脚(www.chuimin.cn)

X2:43引脚,25MHz晶振输出。

X1:44引脚,25MHz晶振输入。

6.LED输出引脚

LED1:39引脚,高速LED。低电平输出表示内部PHY工作在100M/s的模式,悬空表示内部PHY工作在10M/s的模式。在E2PROM的16位模式设置中,该引脚还作为ISA总线的IO16。

LED2:38引脚,链接/运行LED。LED模式1,它作为PHY链路通断和载波侦测的公用灯;LED模式0,它作为PHY载波侦测的专用灯。在E2PROM的16位模式设置中,该引脚还作为ISA总线的IOWAIT或WAKE。

7.10/100M PHY/Fiber

SD:46引脚,光纤信号检测,PECL电平信号,表明光纤接收是否有效。

BGGND:48引脚,带隙地信号。

BGRES:1引脚,带隙引脚。

RXVDD25:2引脚,2.5V接收端口电源。

TXVDD25:9引脚,2.5V发送端口电源。

RX+:3引脚,物理层接收端的正极。

RX-:4引脚,物理层接收端的负极

RXGND:5、47引脚,接收端口地。

TXGND:6引脚,物理层接收端的负极。

TX+:7引脚,物理层发送端口正极。

TX-:8引脚,物理层发送端口负极。

8.其他引脚

TEST:41引脚,工作模式。正常模式时强制接地。

PWRST#I:40引脚,上电复位。低电平有效信号复位DM9000A,DM9000A需要5μs完成初始化。

9.捆绑引脚表

EECK:20引脚,中断极性。为0时中断引脚低有效;为1时中断引脚高有效。

EECS:21引脚,数据总线宽度。为1时8位;为0时16位。

WAKE:22引脚,8位模式下的CS#的极性。为1时CS#引脚高电平有效;为0时CS#引脚低电平有效。

GP6:25引脚,8位模式下INT输出类型。为1时开漏输出;为0时强制输出。

相关推荐