【摘要】:图4.5是S5PV210的顶层时钟图。图4.5S5PV210顶层时钟图1.外部时钟引脚S5PV210的外部时钟源的时钟输入引脚有XRTCXTI、XXTI、XUSBXTI和XHDMIXTI,也可以不使用外部时钟引脚。当USB PHY没有做有效设置时,CMU和PLL使用这个时钟生成其他的时钟模块所需要的时钟。它的输入频率范围为12~50MHz。推荐使用24MHz晶振,因为IROM是基于24MHz输入时钟的。XHDMIXTI:将一个27MHz晶振提供的时钟连接到XHDMIXTI和XHDMIXTO引脚。VPLL或HDMIPHY生成54MHz时钟提供给TV编码器。可以产生高达2GHz的时钟和40∶60的占空比。EPLL主要用于生成音频时钟。

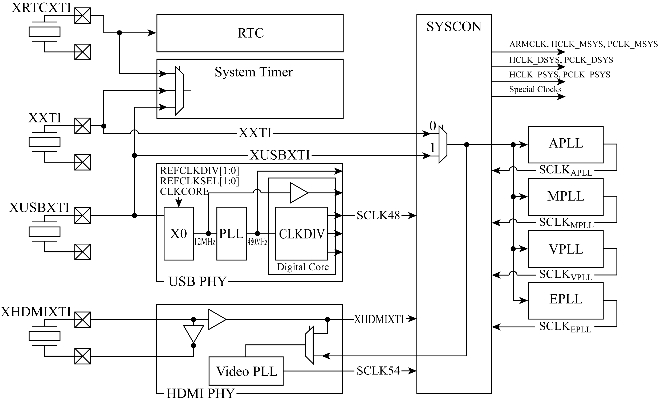

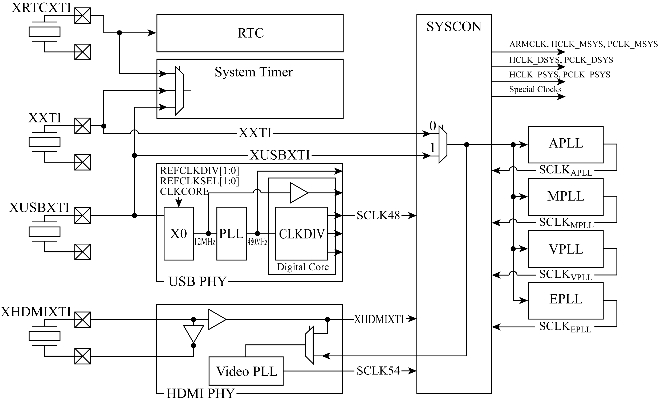

图4.5是S5PV210的顶层时钟图。

图4.5 S5PV210顶层时钟图

1.外部时钟引脚

S5PV210的外部时钟源的时钟输入引脚有XRTCXTI、XXTI、XUSBXTI和XHDMIXTI,也可以不使用外部时钟引脚。

XRTCXTI:将一个32.768KHz晶振提供的时钟连接到XRTCXTI和XRTCXTO引脚。RTC使用这个时钟源作为实时时钟。

XXTI:将一个晶振提供的时钟连接到XXTI和XXTO引脚。当USB PHY没有做有效设置时,CMU和PLL使用这个时钟生成其他的时钟模块(APLL、MPLL、VPLL和EPLL)所需要的时钟。它的输入频率范围为12~50MHz。推荐使用24MHz晶振,因为IROM是基于24MHz输入时钟的。

XUSBXTI:将一个晶振提供的时钟连接到XUSBXTI和XUSBXTO引脚,这个时钟提供给其他时钟模块(APLL、MPLL、VPLL、EPLL和USB PHY)。推荐使用24MHz晶振,因为IROM是基于24MHz输入时钟的。

XHDMIXTI:将一个27MHz晶振提供的时钟连接到XHDMIXTI和XHDMIXTO引脚。VPLL或HDMIPHY生成54MHz时钟提供给TV编码器。

2.时钟管理单元(CMU)

CMU使用时钟引脚(XRTCXTI、XXTI、XUSBXTI和XHDMIXTI)生成内部时钟频率、四个锁相环PLL(APLL、MPLL、EPLL和VPLL)、USB PHY和HDMIPHY。这些时钟可以选择、预分频、提供给其他扩展模块。

3.时钟关系

3大类时钟域中,可以使用不同的分频,使其给不同部件输出所需要的时钟,各类时钟的关系如下:

(1)MSYS时钟域

-freq(ARMCLK)=freq(MOUT_MSYS)/n,where n=1~8

-freq(HCLK_MSYS)=freq(ARMCLK)/n,where n=1~8

-freq(PCLK_MSYS)=freq(HCLK_MSYS)/n,where n=1~8

-freq(HCLK_IMEM)=freq(HCLK_MSYS)/2

(2)DSYS时钟域

-freq(HCLK_DSYS)=freq(MOUT_DSYS)/n,where n=1~16

-freq(PCLK_DSYS)=freq(HCLK_DSYS)/n,where n=1~8(www.chuimin.cn)

(3)PSYS时钟域

-freq(HCLK_PSYS)=freq(MOUT_PSYS)/n,where n=1~16

-freq(PCLK_PSYS)=freq(HCLK_PSYS)/n,where n=1~8

-freq(SCLK_ONENAND)=freq(HCLK_PSYS)/n,where n=1~8

(4)推荐的高性能操作频率值

-freq(ARMCLK)=1000 MHz

-freq(HCLK_MSYS)=200 MHz

-freq(HCLK_IMEM)=100 MHz

-freq(PCLK_MSYS)=100 MHz

-freq(HCLK_DSYS)=166 MHz

-freq(PCLK_DSYS)=83 MHz

-freq(HCLK_PSYS)=133 MHz

-freq(PCLK_PSYS)=66 MHz

-freq(SCLK_ONENAND)=133 MHz、166 MHz

(5)锁相环(PLL)

APLL可以驱动MSYS域和DSYS域。可以产生1GHz的时钟和49∶51的占空比。

MPLL可以驱动MSYS域和DSYS域。可以产生高达2GHz的时钟和40∶60的占空比。

EPLL主要用于生成音频时钟。

VPLL主要用于生成视频系统操作时钟,54 MHz。

通常,APLL驱动MSYS域、MPLL驱动DSYS域。

相关推荐