嵌入式系统的发展大致经历了嵌入式微控制器、嵌入式微处理器和嵌入式数字信号处理器、嵌入式片上系统和以Internet为标志的嵌入式系统等阶段。嵌入式系统的出现最初是基于单片机的,这一阶段的嵌入式系统硬件是单片机,软件停留在无操作系统阶段,采用汇编语言实现系统的功能。第四阶段是以Internet为标志的嵌入式系统。......

2025-09-30

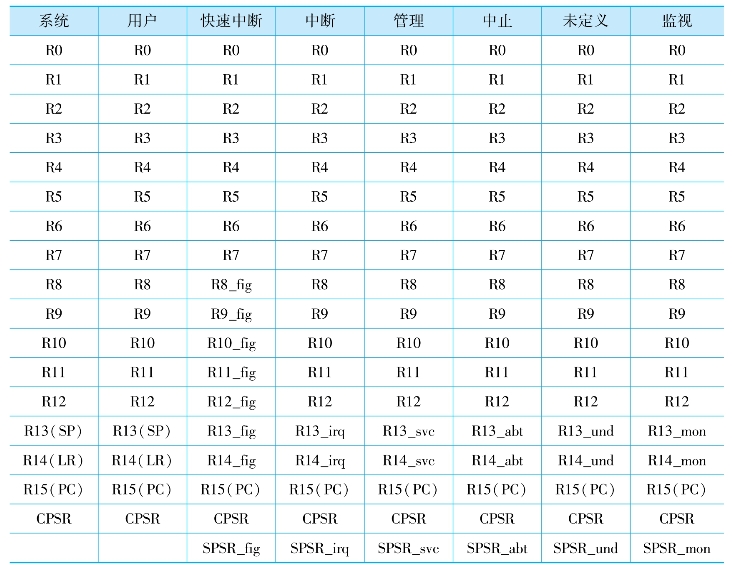

Cortex-A8处理器有40个32位寄存器,分为33个通用寄存器和7个程序状态寄存器。7个程序状态寄存器包括1个当前程序状态寄存器(CPSR)和6个备份程序状态寄存器(SPSR)。ARM正常状态下有16个数据寄存器和1~2个状态寄存器可随时被访问,可被访问的寄存器依赖于处理器当前的工作模式。每种工作模式下处理器可访问的寄存器名称见表2.4。

1.通用寄存器组

表2.4中,R0~R15是通用寄存器。其中R0~R7是不分组的通用寄存器,R8~R15是分组的通用寄存器。这些寄存器用来保存数据或表示地址。

(1)不分组的通用寄存器R0~R7。在所有处理器模式下对于每一个不分组寄存器来说,指的都是同一个物理寄存器。

(2)分组的通用寄存器R8~R15。

①R8~R12:对应两个不同的物理寄存器,由表2.4可知,它们分别为快速中断模式下的相应寄存器及除快速模式外的其他7中模式下的相应寄存器。快速中断下的R8_fig~R12_fig,当FIQ中断到达时,不用保存这些通用寄存器,即程序可以不执行保存和恢复现场的指令,从而可以使中断处理过程非常迅速。

表2.4 ARM状态下Cortex-A8寄存器组

②R13是堆栈指针寄存器(Stack Pointer,SP),用于指向堆栈区的栈顶。每种工作模式具有各自私有的堆栈区和堆栈指针寄存器。

③R14是链接寄存器(Link Register,LR),用于存储子程序返回主程序的链接地址。当处理器执行一条调用指令(BL或BLX)时,R14用于存储主程序的断点地址,供子程序返回主程序;其他时间,R14可以作为一个通用寄存器使用。每种工作模式具有各自私有的链接寄存器。

④R15(PC)5是程序计数器,用于存放下一条指令所在存储单元的地址。由于ARM指令集中的一条指令代码为4字节,因此在取指时指令代码的存储地址应满足字对齐。

2.状态寄存器组

由表2.4可知,Cortex-A8处理器的程序状态寄存器包含1个当前程序状态寄存器CPSR和6个备份程序状态寄存器SPSR。

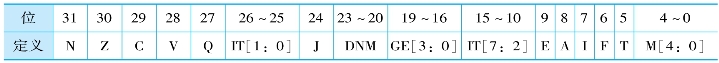

程序状态寄存器(CPSR和SPSR)的主要用途:保存所执行的最后一条逻辑或算术运算指令运行结果的相关信息,控制开启/禁用中断,设置处理器工作模式。程序状态寄存器位格式见表2.5。

表2.5 程序状态寄存器位格式

(1)条件代码标志位

N、Z、C和V位都是条件代码标志。通过算术操作、逻辑操作、MSR或者LDM指令可以对这些位进行设置。各标志位的含义如表2.6所示。

表2.6 各标志位的含义

(https://www.chuimin.cn)

(https://www.chuimin.cn)

(2)状态控制位

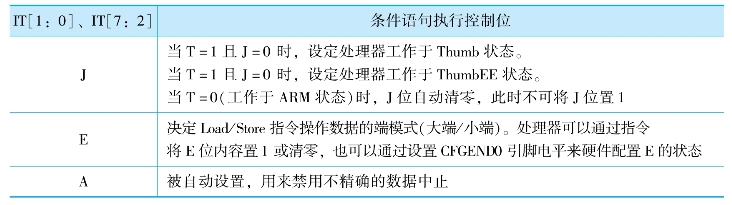

IT[1:0]、IT[7:2]、J、E、A被称为状态控制位,各位具体含义如表2.7所示。

表2.7 状态控制位含义

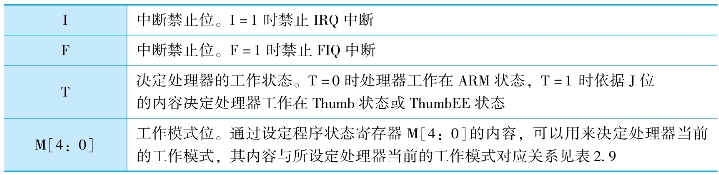

(3)控制位

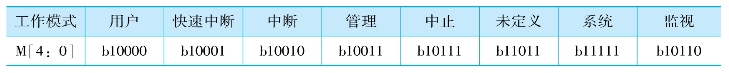

I、F、T、M[4:0]是控制位,其含义如表2.8所示。

表2.8 控制位含义

表2.9 工作模式与M[4:0]的内容对应关系

(4)使用MSR指令修改CPSR寄存器

在ARMv6以前架构版本中,MSR指令可在所有模式下修改标志位字节,即CPSR[31~24]。但CPSR中其他三个字节内容只有在特权模式下可以修改。

ARMv6的改进之处有以下几个方面。

①CPSR寄存器中指定标志位在任何模式下可自由修改,通过MSR指令或借助其他指令执行结果,来改写或直接修改整个CPSR寄存器内容或其中指定标志位内容。这些位包含N、Z、C、V、Q、GE[3:0]、E。

②J和T位的内容不可以使用MSR指令,仅能依据其他指令执行结果来修改。如果使用MSR指令并尝试修改这些位内容,结果不可预知。

③I、F和M[4:0]等位的内容在用户模式下受到保护,仅可在特权模式下改写。用户模式下可以通过执行指令进入处理器的异常模式,在异常模式下来改写这些位的内容。

④只有在安全特权模式下,才可以通过直接写CPSR模式标志位来进入监视模式。如果内核目前处于安全用户模式、非安全用户模式或非安全特权模式,此时设置进入监视模式的修改将被忽略。内核不可以将SPSR寄存器中在非安全模式下发生变化的模式标志位内容复制到CPSR。

⑤DNM(CPSR[23~20])为保留位。当改变CPSR标志或控制位时,确保不改变这些保留标志位的内容以便和未来高版本处理器兼容。

相关文章

嵌入式系统的发展大致经历了嵌入式微控制器、嵌入式微处理器和嵌入式数字信号处理器、嵌入式片上系统和以Internet为标志的嵌入式系统等阶段。嵌入式系统的出现最初是基于单片机的,这一阶段的嵌入式系统硬件是单片机,软件停留在无操作系统阶段,采用汇编语言实现系统的功能。第四阶段是以Internet为标志的嵌入式系统。......

2025-09-30

嵌入式系统设计与开发工作中,软件工作量约占全部工作量的80%,其中测试和验证部分的工作量占软件工作量的70%。图1.6嵌入式系统设计与开发流程1.需求分析分析用户的需求:产品的功能、性能、价格、体积、功耗等。嵌入式系统(实现)编程:选择硬件、操作系统、编程语言以及开发工具,编写程序。......

2025-09-30

在PDA类的设备中,系统在全速运行的时候远比空闲的时候少,所以可以通过设置,使CPU尽可能工作在空闲状态,然后通过相应的中断唤醒CPU,恢复到正常工作模式,处理响应的事件,然后再进入空闲模式。CPU空闲时,降低时钟频率;处于工作状态时,提高时钟频率以全速运行处理事务。......

2025-09-30

嵌入式系统目前已在军事装备、工业制造与过程控制、通信、机器人、仪器与仪表、汽车、船舶、交通管理、信息家电及家庭智能管理、消费类产品各领域普及应用,具有广阔的发展前景。在这些设备中,嵌入式系统将大有用武之地。在服务领域,如远程点菜器等已经体现了嵌入式系统的优势。在很多环境恶劣,地况复杂的地区,嵌入式系统将实现无人监测。......

2025-09-30

ARM是Advanced RISCMachines的缩写,它是一家微处理器行业的知名企业,该企业设计了大量高性能、廉价、耗能低的精简指令集处理器。我们可以从三个层次理解ARM:一个公司的名字;一类微处理器的通称;一种技术的名字。ARM具有以下技术特点:ARM是一种通用的32位RISC处理器。ARM是一种功耗很低的高性能处理器。ARM是一种可扩展,可移植、可集成的处理器。......

2025-09-30

2.开发模式嵌入式系统本身不具备自举开发能力,即使设计完成以后用户通常也是不能对其中的程序功能进行修改的,必须有一套开发工具和环境才能进行开发,这些工具和环境一般是基于通用计算机上的软硬件设备以及各种逻辑分析仪、混合信号示波器等。表1.2常用嵌入式开发工具......

2025-09-30

现在高端嵌入式系统软件都在操作系统的支持下运行。嵌入式操作系统是指用于嵌入式系统的操作系统。嵌入式操作系统负责嵌入式系统的全部软、硬件资源的分配、任务调度,控制、协调并发活动。从20个世纪70年代单片机的出现到今天,嵌入式操作系统经历了发展的四个阶段。这一阶段嵌入式系统的主要特点是:操作系统的实时性得到了很大改善,已经能够运行在各种不同类型的微处理器上,具有高度的模块化特点和扩展性。......

2025-09-30

具体来说,嵌入式系统是以应用为中心、计算机技术为基础,软硬件可裁剪,适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。可以这样认为,嵌入式系统是一种专用的计算机系统,作为装置或设备的一部分。通常,嵌入式系统是一个控制程序存储在ROM中的嵌入式处理器控制板。表1.1对比了通用计算机系统与嵌入式系统。......

2025-09-30

相关推荐