由于单片机的显示和存储功能有限,因而与PC通信是非常必要的。对一些复杂的控制系统,需要以局部单片机组成一套控制网。通信波特率8051串行接口组成的通信系统是一种异步通信系统,即通信双方在发送与接收时,只靠通信双方的软件控制同步。RI接收结束标志。一般对单片机的数据通信要求不很高,用串行接口即可达到,一般为2400~9600bit/s。......

2023-11-07

简单地说,中断就是CPU暂时停止正在做的工作,转而去做其他更重要的事情,当该事情处理完毕后,再返回原来的位置继续做被中止的工作。我们在介绍独立键盘和矩阵键盘时,使用了中断法来监控按键,只有当按键被按下时才会触发中断,CPU停止当前运行的程序,开始检测是哪一个按键被按下,这样可以大大地减轻CPU的查询负担。

7.1.1 中断源

中断是需要被某些因素触发的,中断的触发(请求)源称为中断源,它是引起CPU中断当前任务进程的根源。8051系列单片机的中断源可以分为外部中断源和内部中断源两大类。

(1)外部中断源:这一类中断源的触发条件来自单片机的外部,因而称其为外部中断源。

外部中断0(INT0):来自P3.2引脚,当其采集到低电平或者下降沿时,即可产生中断请求。

外部中断1(INT1):来自P3.3引脚,当其采集到低电平或者下降沿时,同样可以产生中断请求。

(2)内部中断源:这一类触发源来自单片机片内,称其为内部中断源。

定时/计数器0(T0):当定时/计数器0发生计数溢出时,即可产生中断请求。

定时/计数器1(T1):当定时/计数器1发生计数溢出时,即可产生中断请求。

串行口(UART):当单片机的串行口成功地完成接收或发送一组数据时,即可产生中断请求。

7.1.2 中断的处理过程

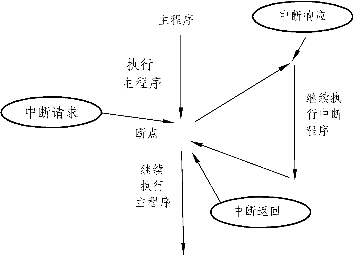

8051系列单片机对中断的处理可以概括为中断请求、中断响应和中断返回三个过程。当中断发生时,中断源向CPU提出处理请求,这一过程称为中断请求或中断申请;CPU接收到中断源的中断请求后,开始对事件进行处理,处理事件的过程称为中断响应;当CPU处理完事件后,会返回到主程序停止处,继续开始执行源程序,这一过程称为中断返回。8051系列单片机对中断的处理流程如图7-2所示。

图7-2 单片机中断过程

8051系列单片机对中断的控制是通过一系列的标志位和控制位来实现的。当一个有效的中断产生时,相应的中断标志位被单片机硬件置位(标志位由“0”变为“1”),并向CPU申请中断响应。CPU检测到中断标志位被置位后,如果该中断得到允许(中断总控制位和分控制位均为“1”),随即转向执行与该中断类型相对应的中断服务程序。中断的标志位在CPU执行了中断服务程序后,硬件会将标志位清零,但对于串行口接收和发送两个中断来说,标志位RI和TI只能由软件清零。当CPU执行完中断服务程序后,会自动回到程序原来的位置,继续执行主程序。

7.1.3 中断的优先级

8051系列单片机有五个中断源,它们都可以向CPU申请中断,那么CPU是如何分辨这五种不同类型的中断的呢?8051系列单片机给这五种中断源都分别指定了相应的中断向量号,并为每个中断向量规定了专用的中断入口地址,就像给每一个人分配好专用的座位号一样。一旦某一个中断发生,它会自动地转向某一个固定的位置,CPU根据位置不同,即可分辨出产生了哪一个类型的中断,并且应该执行哪一个中断服务程序,中断源与中断向量号的对应关系见表7-1。

表7-1 8051单片机的中断向量

1.中断的查询顺序

在明确了向量号之后,一个极端的情况是:当这五个中断源同时发生事件,同时向CPU申请中断时,CPU该怎样处理呢?8051系列单片机规定:如果同级的多个中断同时出现,则按CPU的查询顺序确定哪个中断请求被响应。CPU对中断源的查询次序为:

外部中断0→定时/计数器0→外部中断1→定时/计数器1→串行口

这个查询顺序是由单片机的硬件结构决定的,是CPU对中断的查询顺序,与后面提到的优先级无关,一旦这五个中断在默认设置(不指定优先级)的情况下同时发生,CPU只响应查询顺序在前的中断,而其他中断将被忽略。

2.中断的优先级

单纯依靠查询的办法处理中断有时会将排在其次位置的中断忽略掉,这在一些关键的应用中显得不十分可靠,为此8051系列单片机还引入了中断优先级的概念,可以分别为这五个中断源指定两个不同的优先级,当多个中断同时发生时,优先级高的中断会被优先响应。

8051系列单片机有高和低两个中断优先级,单片机在复位后的默认情况下,五个中断源共同处于低优先级当中。用户可以根据需要,软件指定某一个中断源为高优先级。比如:我们可以将“外部中断1”指定为高优先级,这时当“外部中断0”与“外部中断1”同时发生时,CPU将不按原来的查询顺序处理“外部中断0”了,而是按优先级顺序优先处理“外部中断1”。

3.中断嵌套

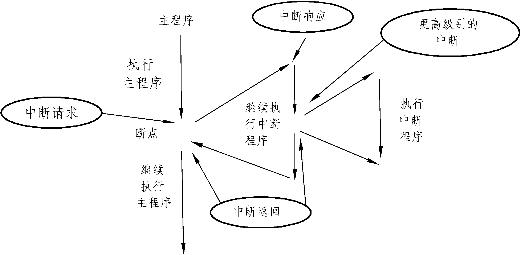

通过优先级控制,还可以实现中断嵌套,即高优先级的中断可以中断低优先级的中断。当CPU在响应某一低优先级中断源的中断请求时,又有一个高优先级的中断产生,CPU则将正在处理的低优先级事件暂停下来,转而处理优先级更高的中断请求,之后再继续执行原来的中断服务程序,这一过程就是中断嵌套,其过程如图7-3所示。

在图7-3中,一个正在执行的低优先级中断程序能被高优先级的中断源中断,但是它不能被另一个低优先级的中断源所中断。当CPU正在执行高优先级的中断时,则不能被任何其他中断源所中断,直到执行结束为止。

图7-3 中断嵌套的原理

优先级的控制原则:

(1)低优先级中断不能中断高优先级的中断,但高优先级的中断可以中断低优先级中断。

(2)如果一个中断请求已被响应,则同级的其他中断服务将被禁止,即同级别中断不能嵌套。

(3)如果同级的多个中断同时出现,CPU只响应查询顺序靠前的那一个。

7.1.4 中断的相关寄存器

8051系列单片机对中断的控制使用了四个寄存器,分别是中断允许寄存器、定时器控制寄存器、串行口控制寄存器和中断优先级控制寄存器。

1.中断允许寄存器IE(Interrupt Enable Register)

8051单片机对中断的使能或屏蔽是通过中断允许寄存器IE来控制的,可位寻址。

(1)bit7(EA):中断允许总控制位。

① 0:禁止所有中断。

② 1:总中断允许。总中断允许后各中断源由各自的中断允许位控制。

(2)bit6,bit5(保留)。

(3)bit4(ES):串行口中断允许位。

① 0:禁止串行中断。

② 1:允许串行中断。

(4)bit3(ET1):定时/计数器T1的溢出中断允许位。

① 0:禁止定时/计数器T1溢出中断。

② 1:允许定时/计数器T1溢出中断。

(5)bit2(EX1):外部中断1允许位。

① 0:禁止外部中断1中断。

② 1:允许外部中断1中断。

(6)bit1(ET0):定时/计数器T0溢出中断允许位。

① 0:禁止定时/计数器T0溢出中断。

② 1:允许定时/计数器T0溢出中断。

(7)bit0(EX0):外部中断0允许位。

① 0:禁止外部中断0中断。

② 1:允许外部中断0中断。

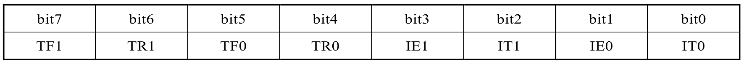

2.定时器控制寄存器TCON(Timer Control Register)

TCON寄存器用来控制两个外部中断和两个定时/计数器的计数溢出,可位寻址。

(1)bit7(TF1):定时/计数器1溢出标志位。

① 0:定时/计数器1无计数溢出。

② 1:定时/计数器1产生计数溢出。

当定时/计数器1产生计数溢出时,相应TF1位由硬件自动置位,如果该中断得到允许,CPU开始执行中断服务程序,一旦CPU开始执行中断服务程序,硬件自动将TF1位清零。

(2)bit6(TR1):定时/计数器1运行控制位。

① 0:定时/计数器1停止计数。

② 1:定时/计数器1启动计数。

(3)bit5 TF0:定时/计数器0溢出标志位。

① 0:定时/计数器0无计数溢出。

② 1:定时/计数器0产生计数溢出。

当定时/计数器0产生计数溢出时,相应TF0位由硬件自动置位,如果该中断得到允许,CPU开始执行中断服务程序,一旦CPU开始执行中断服务程序,硬件自动将TF0位清零。

(4)bit4(TR0):定时/计数器0运行控制位。

① 0:定时/计数器0停止计数。(www.chuimin.cn)

② 1:定时/计数器0启动计数。

(5)bit3(IE1):外部中断1中断标志位。

① 0:无外部中断1发生。

② 1:发生外部中断1。

当CPU采样到INT1端出现有效中断请求时,IE1位自动硬件置位。如果该中断得到允许,CPU开始执行中断服务程序。一旦CPU开始执行中断服务程序,硬件自动将IE1位清零。

(6)bit2(IT1):外部中断请求触发方式控制位。

① 0:电平触发方式,低电平有效。

② 1:脉冲触发方式,下降沿有效。

(7)bit1(IE0):外部中断0中断标志位。

① 0:无外部中断0发生。

② 1:发生外部中断0。

当CPU采样到INT0端出现有效中断请求时,IE0位自动硬件置位,如果该中断得到允许,CPU开始执行中断服务程序。一旦CPU开始执行中断服务程序,硬件自动将IE0位清零。

(8)bit0(IT0):外部中断请求触发方式控制位。

① 0:电平触发方式,低电平有效。

② 1:脉冲触发方式,下降沿有效。

3.串行口控制寄存器SCON(Serial Control Register)

SCON寄存器是串行口控制寄存器,可位寻址。

(1)bit7:2(保留)。

(2)bit1(TI):串行口发送中断标志位。

① 0:无串行口发送中断发生。

② 1:发生串行口发送中断。

当串行口发送完一帧数据后,硬件将该位置位。当CPU执行中断服务程序后,系统不能用硬件将该位清零,需要用软件将该位清零。

(3)bit0(RI):串行口接收中断标志位。

① 0:无串行口接收中断发生。

② 1:发生串行口接收中断。

当串行口接收完一帧串行数据后,硬件将该位置位。当CPU执行中断服务程序后,系统不能用硬件将该位清零,需要用软件将该位清零。

注意:串行口中断请求是由TI和RI位的逻辑“或”得到的,无论是发送标志位还是接收标志位置位,都会产生串行中断请求。

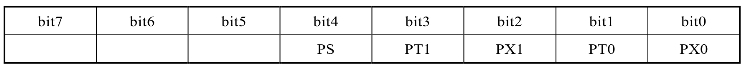

4.中断优先级控制寄存器IP(Interrupt Priority Register)

中断源的优先级由中断优先级寄存器IP进行设定,可位寻址。

(1)bit5~bit7(保留)。

(2)bit4(PS):串行口中断优先级控制位。

① 0:串行口为低优先级中断。

② 1:串行口为高优先级中断。

(3)bit3(PT1):定时器T1中断优先级控制位。

① 0:定时器T1为低优先级中断。

② 1:定时器T1为高优先级中断。

(4)bit2(PX1):外部中断1中断优先级控制位。

① 0:外部中断1为低优先级中断。

② 1:外部中断1为高优先级中断。

(5)bit1(PT0):定时器T0中断优先级控制位。

① 0:定时器T0为低优先级中断。

② 1:定时器T0为高优先级中断。

(6)bit0(PX0):外部中断0中断优先级控制位。

① 0:外部中断0为低优先级中断。

② 1:外部中断0为高优先级中断。

8051单片机对中断的使能是分两级控制的,其中IE寄存器的EA位是中断的总控制位,此外每一个中断源还有自己的中断允许位作为分控位。当总控制位为禁止时,关闭整个中断系统,且不管分控位的状态如何;当总控制位为允许时,中断由各分控位使能或禁止。8051系列单片机复位后,IE寄存器的各位均默认为“0”,因此整个中断系统处于禁止状态。另外,单片机在完成了中断响应后,不会更改已使能的中断控制位。

7.1.5 外部中断的触发方式

外部中断具有两种不同的触发方式,即电平触发和脉冲触发。当IE寄存器的IT0/IT1位清零时,外部中断被设置为电平触发方式,低电平有效;当IT0/IT1位置位时,外部中断被设置为脉冲触发方式,下降沿有效。

1.电平触发方式

在电平触发方式下,CPU每个自动硬件机器周期都会对INT0和INT1引脚进行采样,一旦检测到低电平,相应标志位IE0或IE1置位,并且向CPU申请中断。当CPU执行完中断服务程序后,如果INT0和INT1引脚仍保持为低电平,CPU会再次进入中断状态。

2.脉冲触发方式

在脉冲触发方式下,一旦在INT0和INT1引脚上检测到脉冲的下降沿,相应标志位IE0或IE1自动硬件置位,并且向CPU申请中断。

7.1.6 外部中断的应用

以下我们通过两个实训来加深对外部中断的理解。

【实训7.1】将外部中断0(INT0)设置成低电平触发,用数码管显示发生外部中断的次数,电路图是在任务5.2的电路图的基础上添加一个按键并连接至P3.2引脚,另一端接地。

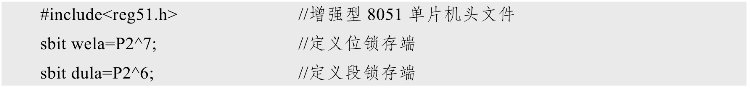

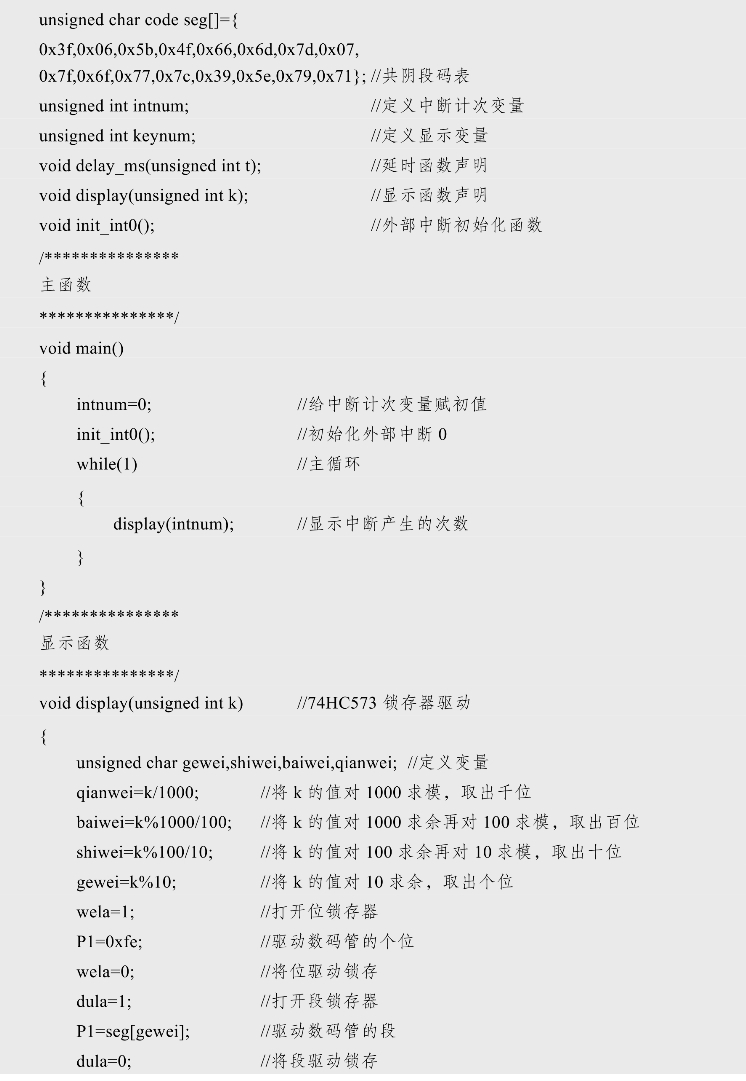

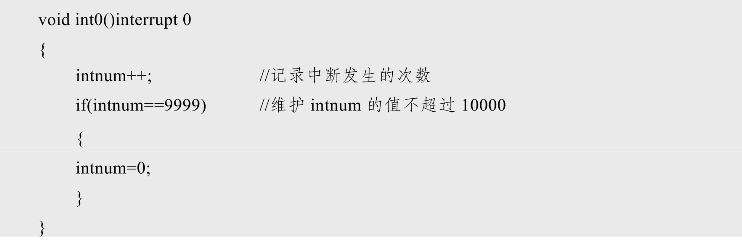

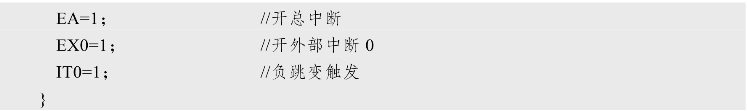

外部中断0的低电平触发程序清单如下:

以上代码经正确编译后在Proteus环境下仿真,程序运行后,数码管显示“0000”,将单击按钮(单片机的P3.2引脚连接至GND端),给该引脚送去一个持续的低电平,这时数码管的数字会持续地累加,直到弹起按钮后,数字累加才会停止,具体状态如图7-4所示。

图7-4 外部中断0的低电平触发

从上面的例子中我们发现:当低电平出现在INT0引脚时,即有中断产生,并且CPU执行了中断服务程序,数码管显示了中断产生的次数。如果INT0引脚为持续的低电平,中断也会持续的发生,这也是8051系列单片机外部中断低电平触发的特点。下面我们将程序稍做改动,将外部中断0设置为下降沿触发,具体改动方法可以参考以下代码:

程序运行后,再次单击按键,数码管显示“1”,每单击一次,数字增加1。在实际使用开发板或实验板时,由于在按键按下的瞬间,P3.2引脚上产生了一个负跳变,从而引发了中断,数码管显示一个较小的数值是因为引线连接时会有触点抖动的现象,产生了多个下降沿,但这个时间很短,产生的下降沿数量有限,所以数码管的显示数值不会增加很多。在Proteus环境中程序运行的状态如图7-5所示。

图7-5 外部中断0的下降沿触发(Proteus下的仿真)

在任务7.1中,使用了单片机的定时中断来完成精确的定时,我们身边的很多设备具有定时功能,如学校的打铃器、电视机的定时关机、空调的定时开关、运动场上的秒表等。与之类似的是,单片机工作时也需要计时或计数,这些功能的实现可以通过集成在芯片内部的定时/计数器来完成。

有关单片机原理与应用 基于C语言的文章

由于单片机的显示和存储功能有限,因而与PC通信是非常必要的。对一些复杂的控制系统,需要以局部单片机组成一套控制网。通信波特率8051串行接口组成的通信系统是一种异步通信系统,即通信双方在发送与接收时,只靠通信双方的软件控制同步。RI接收结束标志。一般对单片机的数据通信要求不很高,用串行接口即可达到,一般为2400~9600bit/s。......

2023-11-07

MCS—51系列单片机中,有的芯片有片内程序存储器,有的芯片内没有程序存储器。MCS—51单片机片内有4 KB ROM,片外还可以扩展64 KB ROM。......

2023-10-21

8051系列单片机内部集成的串行通信接口全称为“通用异步收发器”,它既可作异步传输使用,也可作同步移位寄存器使用,还可用于数据的组网通信。图9-7 8051系列单片机通用异步收发器的内部结构UART工作时,定时器T1用于产生通信需要的时钟,控制寄存器用于对串行口的工作状态进行相应的监控和设置。......

2023-11-17

1.中断响应的条件1)当前机器周期还不是正在执行指令的最后一个机器周期,任何中断请求都得不到响应。2)同优先级或高优先级的中断已在进行中,此中断不会被响应。中断查询的机器周期正好是指令的最后一个机器周期时,查询占1个机器周期,响应中断执行隐指令LCALL需两个机器周期,则共需3个机器周期。......

2023-11-17

8051有5个中断源,即两个外部中断、两个定时/计数器中断和一个串行发送/接收中断。1.外部中断外部中断是由连接到单片机外部引脚信号变化而引起的中断,反映外部某一事件的发生。CPU是在每个机器周期的S5P2检测P 3.2和P 3.3上的信号,如果是有效信号则对定时器控制寄存器TCON中的IE0或IE1置1,建立中断请求标志。表6-1中断源的主要内容及说明......

2023-11-17

CPU对中断处理过程包括中断初始化、中断响应、保护现场、中断服务程序处理、中断撤销和中断返回。所以在进入中断服务子程序后,一般都要保护现场,再执行中断服务程序,返回主程序前再恢复现场,用户在编制中断处理程序时必须要考虑上述问题。......

2023-11-04

1.生产厂商常见的单片机生产厂商有Intel公司、Motorola公司、Philips公司、Atmel公司、Zilog公司、NEC公司、MicroChip公司、ADI公司、Epson公司、NS公司、AMD公司、WinBond公司、Scenix公司、Toshiba公司、Fujitsu公司、Samsung公司等。2.单片机系列常见的单片机系列有Intel公司的MCS-51、MCS-96/98系列,Motorola公司的68HC05、68HC5X、68HC12、68HC16、683XX系列,Philips公司的80C5X系列,Atmel公司的AT89系列,Zilog公司的Z8、Z86系列,ADI公司的MC-6801系列,MicroChip公司的PIC16CX、PIC16FX、PIC17CX、PIC18CX系列,NEC公司的μPD7800系列,Toshiba公司的MB8900、MB90系列等。......

2023-11-17

相关推荐