74HC573锁存器除了具有总线收发器的功能以外,还具有数据的保持功能。通过74HC573不但可以直接驱动数码管,而且还可以减少单片机I/O端口的使用,在实际工程中对外围器件的控制可以减少干扰。......

2023-11-17

在实际应用中,有时我们希望总线上的数据能随单片机I/O口变化而变化,有时又希望单片机I/O口上的数据在总线上有一个固定的保持时间,这些功能的实现可以通过锁存器来完成。

5.3.1 74HC573锁存器的功能

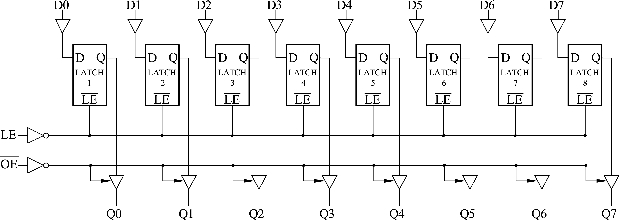

锁存器有多种型号,其中比较有代表性的型号是74HC573,全称为“八进制三态非反转透明锁存器”,其内部逻辑电路结构如图5-20所示。74HC573是一种高性能硅栅CMOS集成电路,拥有八路输出的透明锁存器,输出为三态门,器件的输入与标准CMOS电平兼容。锁存器可以驱动大电容或低阻抗负载,可以直接与总线连接并驱动总线,特别适用于缓冲、I/O通道、双向总线驱动等应用。

图5-20 74HC573内部逻辑电路

74HC573的八个锁存器都是透明的D型锁存器,当锁存端(LE)为高电平时,Q端输出将随数据D端输入的变化而变化。当LE端为低电平时,Q端输出将锁存在已建立的数据电平上。输出控制端(OE)不会影响锁存器的内部工作,当OE为高电平时,输出关闭,但上一个数据仍可以在器件内部保持,新的数据也可以置入。

5.3.2 74HC573的引脚排列

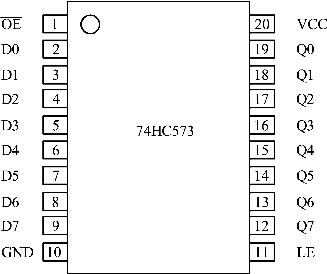

74HC573为20引脚,单电源供电,供电电压为2.0~6.0 V,其外观如图5-21所示,引脚排列如图5-22所示。

图5-21 DIP20封装的74HC573(www.chuimin.cn)

图5-22 74HC573引脚排列

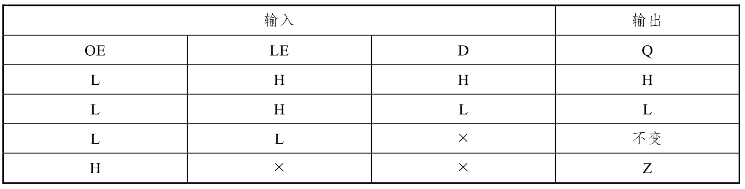

74HC573的1脚是OE端(Output Enable),即输出使能,它是芯片的选通开关。当OE端为低电平时,芯片被选通并可以正常工作;而当OE端为高电平时,芯片进入关闭状态,Q0~Q7八个输出端呈高阻状态。2~9脚是8位数据输入端(D0~D7),12~19脚是8位数据输出端(Q0~Q7),并且Dx与Qx相对应。11脚为数据锁存使能端(LE),当该引脚为高电平时,芯片进入透明状态,输入端D0~D7电平的变化,会引起输出端Q0~Q7电平的相应变化。当LE端为低电平时,芯片进入锁存状态,芯片的输出端Q0~Q7会保持在锁存时刻的电平状态,当输入端电平变化时,输出端数据仍保持不变。74HC573各引脚之间的逻辑关系(真值表)见表5-2。

表5-2 74HC573真值表

注:H=高电平,L=低电平,×=不用关心,Z=高阻态。

通常情况下,锁存器与单片机I/O口相连接,可以实现以下两种功能:

(1)数据锁存:先将数据从单片机的端口输出至Dn,再将LE端从0→1→0,这时单片机输出的数据就锁存在Qn上。这时单片机端口的输出数据的再次变化将不会影响Qn端数据的输出。这时,单片机与锁存器相连端口可以用于与其他器件的通信,并且不会影响到被锁存的数据。

(2)数据缓冲:与总线驱动器74HC245一样,74HC573同样具有较高的驱动能力,其单个输出端的灌电流和拉电流都可以达到35 mA,当锁存器的LE端为高电平时,锁存器为透明状态,其功能相当于总线收发器,可用于提高单片机对总线的驱动能力。

有关单片机原理与应用 基于C语言的文章

74HC573锁存器除了具有总线收发器的功能以外,还具有数据的保持功能。通过74HC573不但可以直接驱动数码管,而且还可以减少单片机I/O端口的使用,在实际工程中对外围器件的控制可以减少干扰。......

2023-11-17

表6-12 SPC3内存分配注:HW禁止超出地址范围,也就是如果用户写入或读取超出存储器末端,用户将得到一新的地址,即原地址减去400H。禁止覆盖处理器参数,在这种情况下,SPC3产生一访问中断。表6-13 内部参数锁存器分配(读)表6-14 内部参数锁存器分配(写)(续)3.组织参数用户把组织参数存储在特定的内部RAM中,用户可读也可写。......

2023-11-22

功能块PULSEGEN和功能块CONT_C一起,可实现具有脉冲输出的控制器,用于控制比例执行器。在参数分配期间,用户可以激活或取消激活PID控制器的子功能,以使控制器适合实际的工艺过程。......

2023-06-18

为了防止这种现象发生,也为了降低油耗,当车速在大于60km/h时,锁止离合器会通过机械摩擦将泵轮与涡轮相连接。锁止离合器的接合和分离由变矩器中的液压油的流向改变来决定。加压油液流至锁止离合器的前端,锁止离合器前端及后端的压力就变得一样,锁止离合器处于脱开状态。这时,变矩器壳体受到锁止活塞挤压,从而使锁止离合器和前盖一起转动,即锁止离合器接合。锁止离合器接合时的动力传输过程如图1-3-8所示。......

2023-08-25

如果要改善多路输出中某一组或某几组的负载调整率,则可采用图1-45所示的方法,就是给5V输出加一个模拟负载,它的阻值应根据负载变化的范围而定。若一个开关电源有5组输出,则不可能每一组都出现负载调整率不稳定,最多也不超过两组,这两组在低压、大电流输出时也许会出现不稳定。......

2023-06-25

多路输出高频变压器的设计与一般变压器虽然有很多相同的方面,但是不完全一样。设计多路输出高频变压器时应注意如下事项。图1-46 多路输出变压器脚位设计2.磁心的选用多路输出受自身输出功率、磁心的热力效应、磁心的损耗、饱和磁感应强度等多种因素的影响,因此,选择磁心时一定要选用最佳磁感应强度的磁心,这是为了避免出现磁心磁饱和,达到磁心的总损耗最小。......

2023-06-25

图3-20所示的传感器输出接口描述了8种不同的连接外部器件的电路结构。主电路中,传感器中的光电二极管发出光束使场效应管打开。晶体管发射极与电源正端相连,所以在PNP器件中,电流从发射极流到集电极,然后从传感器输出到负载。用每个器件的集电极之间的开关来控制输出,当开关处于上面的位置,传感器是PNP输出,电路工作于电流源方式。传感器的电流最大时,饱和压降为NPN直流1.2V,PNP直流2V。......

2023-06-25

变频器的输出因频率变化而有一些特点需要注意:输出电压的测量输出电压指输出端子间的基波方均根电压。为了进一步改善输出电压的测量精度,可以采用阻容滤波器与整流式电压表配合使用。输出电流的测量输出电流是指流过输出端子的总线的方均根电流。输出电流需要测量包括基波和其他谐波在内的总有效值。......

2023-06-19

相关推荐