所谓I/O接口也就是输入/输出接口。根据信号传输方式的不同,I/O接口一般可分为并行接口和串行接口两种方式。通常所说的并行接口一般称为Centronics接口,也称为IEEE1284标准。当传输距离较远、位数又多时,并行接口会导致通信线路复杂且成本提高。图5-13所示为各类并行接口及并行电缆,传输的是数字量和开关量。串行接口按电气标准及协议来分包括RS-232-C、RS-422、RS-485等。......

2023-06-23

为什么要给P0口加上拉电阻呢?要想彻底理解单片机P0口加上拉电阻的问题,必须要从P0端口的结构及工作原理入手。

51系列单片机有4个双向的8位并行I/O端口,分别记作P0、P1、P2、P3,共有32根端口线。其中,P0、P2、P3端口为多功能端口。这是针对最早的MCS-8051系列来说的,现在国内最新的STC公司生产的12系列、15系列的单片机对此有新的定义,读者可自行查阅相关资料进行了解。这里还是以MCS-8051为背景来讲解,重点讲解P0口。

4.1.1 P0端口的结构及工作原理

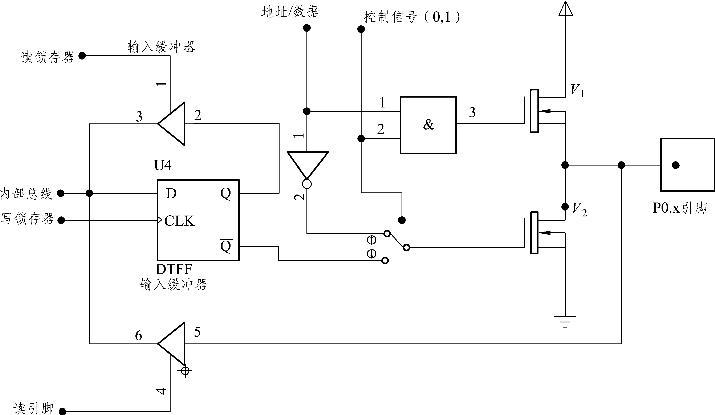

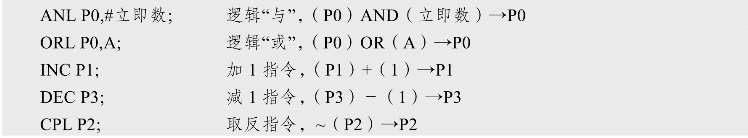

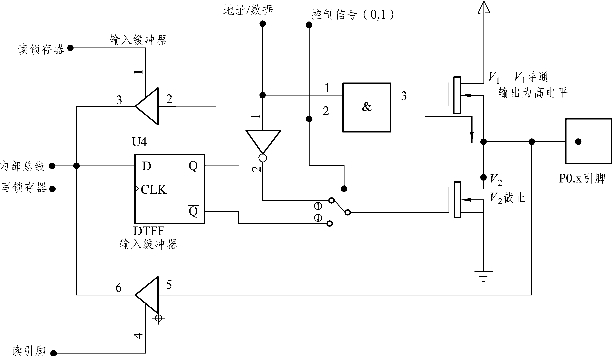

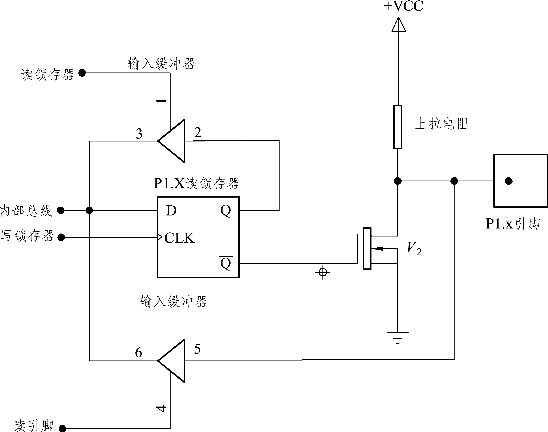

P0端口8位中的1位结构图如图4-3所示。

图4-3 PO口工作原理图

由图4-3可见,P0端口由锁存器、输入缓冲器、切换开关、与非门、与门及场效应管驱动电路构成。再看图的右边标号为P0.x引脚的图标,也就是说P0.x引脚可以是P0.0~P0.7的任何一位,即在P0口由8个与图4-3相同的电路组成。

1.P0口的组成

先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即它的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),观察图4-3,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(图中标号为“读锁存器”端)有效。下面一个是读引脚的缓冲器,要读取P0.x引脚上的数据,也要使标号为“读引脚”的这个三态缓冲器的控制端有效,引脚上的数据才会传输到单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。观察图4-3中的D锁存器,D端是数据输入端,CLK是控制端(也就是时序控制信号输入端),Q是输出端, 是反向输出端。

是反向输出端。

对于D触发器来说,当D输入端有一个输入信号,如果这时控制端CLK没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端 的。如果时序控制端CLK的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及

的。如果时序控制端CLK的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及 端。数据传送过来后,当CLK时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来)。如果下一个时序控制脉冲信号到来,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

端。数据传送过来后,当CLK时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来)。如果下一个时序控制脉冲信号到来,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

多路开关:在51单片机中,当内部的存储器够用(也就是不需要外扩展存储器时,这里的存储器包括数据存储器及程序存储器)时,P0口可以作为通用的输入/输出端口(即I/O)使用,对于8031(内部没有ROM)的单片机或者编写的程序超过单片机内部的存储器容量,需要外扩存储器时,P0口就作为“地址/数据”总线使用。那么,这个多路选择开关就是用于选择是作为普通I/O口使用还是作为“数据/地址”总线使用的选择开关。观察图4-3,当多路开关与下面接通时,P0口是作为普通的I/O口使用的,当多路开关是与上面接通时,P0口是作为“地址/数据”总线使用的。

输出驱动部分:从图4-3中可以看出,P0口的输出是由两个MOS管组成的推拉式结构,也就是说,这两个MOS管一次只能导通一个,当V1导通时,V2就截止;当V2导通时,V1截止。

与门、与非门:这两个单元电路的逻辑原理前面已经介绍,这里不再赘述。

前面我们已将P0口的各单元部件进行了一个详细的讲解,下面我们就来研究一下P0口作为I/O口及地址/数据总线使用时的具体工作过程。

2.作为I/O端口使用时的工作原理

P0口作为I/O端口使用时,多路开关的控制信号为0(低电平)。在图4-中的控制信号线部分,多路开关的控制信号同时与与门的一个输入端是相接的,我们知道与门的逻辑特点是“全1出1,有0出0”,那么控制信号如果是0,这时与门输出的也是0(低电平)。与门的输出如果是0,V1管就截止,在多路控制开关的控制信号是0(低电平)时,多路开关是与锁存器的 端相接的(即P0口作为I/O接口线使用)。

端相接的(即P0口作为I/O接口线使用)。

P0口用作I/O端口时,其由数据总线向引脚输出(即输出状态Output)的工作过程:当写锁存器信号CLK有效,数据总线的信号→锁存器的输入端D→锁存器的反向输出 端→多路开关→V2管的栅极→V2的漏极到输出端P0.x。当多路开关的控制信号为低电平0时,与门输出为低电平,V1管是截止的,所以作为输出口时,P0是漏极开路输出,类似于OC门,当驱动上接电流负载时,需要外接上拉电阻。

端→多路开关→V2管的栅极→V2的漏极到输出端P0.x。当多路开关的控制信号为低电平0时,与门输出为低电平,V1管是截止的,所以作为输出口时,P0是漏极开路输出,类似于OC门,当驱动上接电流负载时,需要外接上拉电阻。

图4-4所示为由内部数据总线向P0口输出数据的流程图。

图4-4 P0口由内部总线向引脚输出数据的流程图

P0口用作I/O端口时,其由引脚向内部数据总线输入(即输入状态Input)的工作过程:

数据输入时(读P0口)有两种情况。

1)读引脚

读芯片引脚上的数据,读引脚数时,读引脚缓冲器打开(即三态缓冲器的控制端要有效),通过内部数据总线输入,如图4-5所示。

图4-5 P0口读引脚时的流程图

2)读锁存器

通过打开读锁存器三态缓冲器读取锁存器输出端Q的状态,如图4-6所示。

图4-6 P0口读锁存器时的流程图

在输入状态下,从锁存器和从引脚上读来的信号一般是一致的,但也有例外。例如,当从内部总线输出低电平后,锁存器Q=0, =1,场效应管V2开通,端口线呈低电平状态。此时无论端口线上外接的信号是低电平还是高电平,从引脚读入单片机的信号都是低电平,因而不能正确地读入端口引脚上的信号。又如,当从内部总线输出高电平后,锁存器Q=1,

=1,场效应管V2开通,端口线呈低电平状态。此时无论端口线上外接的信号是低电平还是高电平,从引脚读入单片机的信号都是低电平,因而不能正确地读入端口引脚上的信号。又如,当从内部总线输出高电平后,锁存器Q=1, =0,场效应管V2截止。如外接引脚信号为低电平,从引脚上读入的信号就与从锁存器读入的信号不同。

=0,场效应管V2截止。如外接引脚信号为低电平,从引脚上读入的信号就与从锁存器读入的信号不同。

为此,8031单片机在对端口P0~P3的输入操作上,有如下约定:凡属于读-修改-写方式的指令,从锁存器读入信号,其他指令则从端口引脚线上读入信号。

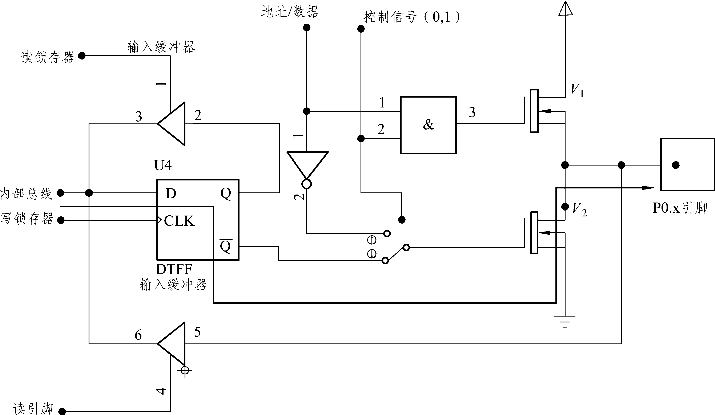

读-修改-写指令的特点是,从端口输入(读)信号,在单片机内加以运算(修改)后,再输出(写)到该端口上。下面是几条读-修改-写指令(汇编指令,因本书是以C语言为主,汇编部分仅供参考)的例子。

这样安排的原因在于读-修改-写指令需要得到端口原输出的状态,修改后再输出,读锁存器而不是读引脚,可以避免因外部电路的原因而使原端口的状态被读错。

P0端口是8031单片机的总线口,分时出现数据D7~D0、低8位地址A7~A0,以及三态,用来连接存储器、外部电路与外部设备。P0口是使用最广泛的I/O端口。

3.作为地址/数据复用口使用时的工作原理

在访问外部存储器时,P0口作为地址/数据复用口使用。

这时多路开关“控制”信号为“1”,“与门”解锁,“与门”输出信号电平由“地址/数据”线信号决定;多路开关与反相器的输出端相连,地址信号经“地址/数据”线→反相器→V2场效应管栅极→V2漏极输出。

例如:控制信号为“1”,地址信号为“0”时,“与门”输出低电平,V1管截止;反相器输出高电平,V2管导通,输出引脚的地址信号为低电平如图4-7所示。

图4-7 P0口作为地址线,控制信号为1,地址信号为0时的工作流程

反之,控制信号为“1”,地址信号为“1”,“与门”输出为高电平,V1管导通;反相器输出低电平,V2管截止,输出引脚的地址信号为高电平如图4-8所示。

图4-8 P0口作为地址线,控制信号为1,地址信号为1时的工作流程

可见,在输出“地址/数据”信息时,V1、V2管是交替导通的,驱动能力很强,可以直接与外设存储器相连,无须增加总线驱动器。

P0口又作为数据总线使用。在访问外部程序存储器时,P0口输出低8位地址信息后,将变为数据总线,以便读指令码(输入)。

在取指令期间,“控制”信号为“0”,V1管截止,多路开关也跟着转向锁存器反相输出端 ;CPU自动将0FFH(11111111,即向D锁存器写入一个高电平“1”)写入P0口锁存器,使V2管截止,在读引脚信号控制下,通过读引脚三态门电路将指令码读到内部总线,如图4-9所示。

;CPU自动将0FFH(11111111,即向D锁存器写入一个高电平“1”)写入P0口锁存器,使V2管截止,在读引脚信号控制下,通过读引脚三态门电路将指令码读到内部总线,如图4-9所示。

图4-9 P0口作为数据总线,取指期间工作流程

如果该指令是输出数据,如MOVX @DPTR,A(将累加器的内容通过P0口数据总线传送到外部RAM中),则多路开关“控制”信号为“1”,“与门”解锁,与输出地址信号的工作流程类似,数据由“地址/数据”线→反相器→V2场效应管栅极→V2漏极输出。

如果该指令是输入数据(读外部数据存储器或程序存储器),如MOVX A,@DPTR(将外部RAM某一存储单元内容通过P0口数据总线输入到累加器A中),则输入的数据仍通过读引脚三态缓冲器到内部总线,其过程类似于图4-9中的读取指令码流程图。

通过以上的分析可以看出,当P0作为地址/数据总线使用时,在读指令码或输入数据前,CPU自动向P0口锁存器写入0FFH,破坏了P0口原来的状态。因此,不能再作为通用的I/O端口。在系统设计时务必注意,即程序中不能再含有以P0口作为操作数(包含源操作数和目的操作数)的指令,由其在使用C语言编程时注意此类问题,如果把握不准,可以进行混合编程,在类似的地方用汇编语言。(www.chuimin.cn)

P0口作为通用I/O端口使用时,一定要外接上拉电阻。上拉电阻的作用简单来说就是将不确定的电平拉成高电平,让CPU能正确读取端口信息。这也是任务4.1中在P0口外接上拉电阻与不外接上拉电阻的区别。为什么P2口不外接上拉电阻就能驱动外围电路工作呢?下面我们来学习P1、P2、P3端口的结构和工作原理。

4.1.2 P1端口的结构及工作原理

P1口的结构最简单,用途也单一,仅作为数据输入/输出端口使用。输出的信息有锁存,输入有读引脚和读锁存器之分。P1端口的一位结构如图4-10所示。

由图4-10可见,P1端口与P0端口的主要差别在于,P1端口用内部上拉电阻R代替了P0端口的场效应管V1,并且输出的信息仅来自内部总线。由内部总线输出的数据经锁存器反相和场效应管反相后,锁存在端口线上,因此,P1端口是具有输出锁存的静态口。

由图4-10可见,要正确地从引脚上读入外部信息,必须先使场效应管关断,以便由外部输入的信息确定引脚的状态。为此,在作引脚读入前,必须先对该端口写入“1”。具有这种操作特点的输入/输出端口,称为准双向I/O口。8051单片机的P1、P2、P3都是准双向口。P0端口由于输出有三态功能,输入前,端口线已处于高阻态,无须先写入“1”后再做读操作。

图4-10 P1口的工作原理

单片机复位后,各个端口已自动地被写入了“1”,此时,可直接作输入操作。如果在应用端口的过程中,已向P1~P3端口线输出过“0”,则再要输入时,必须先写“1”后再读引脚,才能得到正确的信息。此外,随输入指令的不同,P1端口也有读锁存器与读引脚之分。

4.1.3 P2端口的结构及工作原理

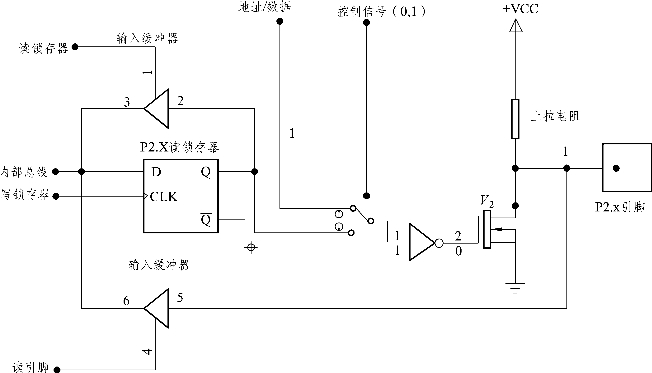

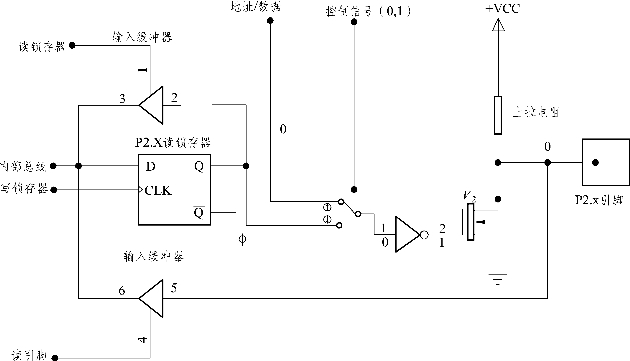

P2端口的一位结构如图4-11所示。

由图4-11可见,P2端口在片内既有上拉电阻,又有切换开关MUX,所以P2端口在功能上兼有P0端口和P1端口的特点。这主要表现在输出功能上,当切换开关向下接通时,从内部总线输出的一位数据经反相器和场效应管反相后,输出在端口引脚线上;当多路开关向上时,输出的一位地址信号也经反相器和场效应管反相后,输出在端口引脚线上。

图4-11 P2口的工作原理

对于8031单片机必须外接程序存储器才能构成应用电路(或者应用电路扩展了外部存储器),而P2端口就是用来周期性地输出从外存中取指令的地址(高8位地址),因此,P2端口的多路开关总是在进行切换,分时地输出从内部总线来的数据和从地址信号线上来的地址。因此,P2端口是动态的I/O端口。输出数据虽被锁存,但不是稳定地出现在端口线上。其实,这里输出的数据往往也是一种地址,只不过是外部RAM的高8位地址。

在输入功能方面,P2端口与P0和P1端口相同,有读引脚和读锁存器之分,并且P2端口也是准双向口。

可见,P2端口的主要特点包括:

(1)不能输出静态的数据。

(2)自身输出外部程序存储器的高8位地址。

(3)执行MOVX指令时,还输出外部RAM的高位地址,故称P2端口为动态地址端口。

即P2口既可以作为I/O口使用,也可以作为地址总线使用。

1.作为I/O端口使用时的工作过程

当没有外部程序存储器或虽然有外部数据存储器,但需求容量不大于256 B,即不需要高8位地址时(在这种情况下,不能通过数据地址寄存器DPTR读写外部数据存储器),P2口可以作为I/O口使用。这时,“控制”信号为“0”,多路开关转向锁存器同相输出端Q,输出信号经内部总线→锁存器同相输出端Q→反相器→V2管栅极→V2管漏极输出。

当D为“1”时,经反相后为“0”,V2截止,经上拉电阻作用后,输出引脚为高电平“1”,如图4-12所示。

图4-12 控制为“0”,D为“1”时,V2截止,P2.X为“1”

当D为“0”时,经反相后为“1”,V2导通,整个输出线为低电平,输出引脚为低电平“0”,如图4-13所示。

图4-13 控制为“0”,D为“0”时,V2导通,P2.X为“0”

由于V2漏极带有上拉电阻,可以提供一定的上拉电流,负载能力约为8个TTL与非门;作为输出口前,同样需要向锁存器写入“1”,使反相器输出低电平,V2管截止,即引脚悬空时为高电平,防止引脚被钳位在低电平。读引脚有效后,输入信息经读引脚三态门电路到内部数据总线。

2.作为地址总线使用时的工作过程

P2口作为地址总线时,“控制”信号为‘1’,多路开关车向地址线(即向上接通),地址信息经反相器→V2管栅极→漏极输出。由于P2口输出高8位地址,与P0口不同,无须分时使用,因此P2口上的地址信息(程序存储器上的A15~A8)与数据地址寄存器高8位DPH保存时间长,无须锁存。

当地址/数据为“1”时,经反相后为“0”,V2截止,因上拉电阻作用,P2.X为高电平“1”,如图4-14所示。

图4-14 当控制为“1”,地址/数据为“1”时,V2截止,P2.X为“1”

当地址/数据为“0”时,经反相后为“1”,V2导通,整个输出线为低电平,输出引脚为低电平“0”,如图4-15所示。

图4-15 控制为“1”,地址/数据为“0”时,V2导通,P2.X为“0”

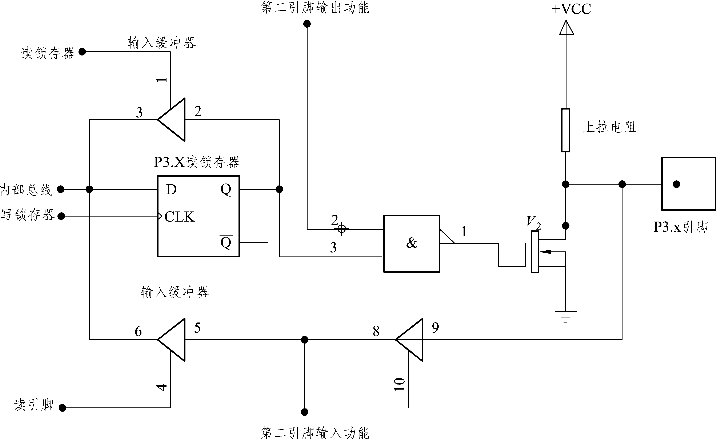

4.1.4 P3端口的结构及工作原理

P3口是一个多功能口,它除了可以作为I/O口外,还具有第二功能。P3端口的一位结构如图4-16所示。

图4-16 P3端口的结构

由图4-16可见,P3端口和Pl端口的结构相似,区别仅在于P3端口的各端口线有两种功能选择。当处于第一功能时,第二输出功能线为“1”,此时,内部总线信号经锁存器Q端和与非门后和场效应管相连,其作用与P1端口作用相同,也是静态准双向I/O端口。当处于第二功能时,锁存器输出“1”,和通过第二输出功能线输出特定的内含信号(WR、RD、TxD)相与后再反相,通过V2后输出。在输入方面,既可以通过缓冲器读入引脚信号,还可以通过替代输入功能读入片内的特定第二功能信号(RxD,T0,T1,INT0,INT1),此时第二输出功能线自动为“1”,信号经右边缓冲器(在图4-16中为右边)直接进入内总线。由于输出信号锁存并且有双重功能,P3端口为静态双功能端口。

P3口的特殊功能(即第二功能)见表4-1。

表4-1 P3口的特殊功能

续表

使P3端品各线处于第二功能的条件是:

(1)串行I/O处于运行状态(RXD,TXD)。

(2)打开了处部中断(INT0,INT1)。

(3)定时器/计数器处于外部计数状态(T0,T1)。

(4)执行读写外部RAM的指令(RD,WR)。

在应用中,如不设定P3端口各位的第二功能(WR,RD信号的产生不用设置),则P3端口线自动处于第一功能状态,也就是静态I/O端口的工作状态。在更多的场合是根据应用的需要,把几条端口线设置为第二功能,而另外几条端口线处于第一功能运行状态。在这种情况下,不宜对P3端口作字节操作,需采用位操作的形式。

有关单片机原理与应用 基于C语言的文章

所谓I/O接口也就是输入/输出接口。根据信号传输方式的不同,I/O接口一般可分为并行接口和串行接口两种方式。通常所说的并行接口一般称为Centronics接口,也称为IEEE1284标准。当传输距离较远、位数又多时,并行接口会导致通信线路复杂且成本提高。图5-13所示为各类并行接口及并行电缆,传输的是数字量和开关量。串行接口按电气标准及协议来分包括RS-232-C、RS-422、RS-485等。......

2023-06-23

图4-41I/O引脚等效原理图本节所有的寄存器和位以通用格式表示:小写的“x”表示端口的序号,而小写的“n”代表位的序号,但是在程序里要写完整。通用数字I/O的端口为具有可选上拉电阻的双向I/O端口。图4-42通用数字I/O说明:WRx、WPx、WDx、RRx、RPx和RDx对于同一端口的所有引脚都是一样的。注意SBI指令能够用来改变端口的单个位。表4-15端口引脚配置......

2023-06-26

把扩展芯片接入单片机系统,数据线和控制信号的连接比较简单,而地址线的连接则比较复杂,因为地址线的连接涉及I/O编址和芯片选取问题。程序存储器系统和数据存储器系统的外扩展地址空间大小相同,但外扩展程序存储器ROM的起始地址与单片机芯片是否有片内程序存储器有关。口线信号为低电平状态时芯片被选中。译码法寻址所谓译码法,就是使用译码器对高位地址进行译码,以其译码输出作为扩展芯片的片选信号。......

2023-11-17

MCS—51系列单片机中,有的芯片有片内程序存储器,有的芯片内没有程序存储器。MCS—51单片机片内有4 KB ROM,片外还可以扩展64 KB ROM。......

2023-10-21

早期的51系列单片机的带负载能力是很小的,P1~P3口,每个引脚可以带动3个TTL输入端,只有P0口的能力强,可以带动8个。但分析一下TTL的输入特性就可以发现,51单片机基本上没有驱动能力,它的引脚甚至不能带动LED进行正常发光。而当这些引脚“输出高电平”时,单片机的“拉电流”能力竟然不到1mA。但是单片机此时几乎没有输出能力,必须采用外接“上拉电阻”的方法来提供D2所需的电流。......

2023-10-28

程序点评:数据传送指令MOV将一组数据分别传送到P1口,做了输出口的操作。将8位立即数传送给累加器A,再由累加器A将数据传送到I/O接口的P1口,使P1.0灯亮。在I/O接口输出操作时不能将间接寄存器中的地址输出到P1口。......

2023-11-07

图1-7磁盘I/O瓶颈现象调查最理想的I/O应用就是所有控制器相应的设备都得以均衡使用。图1-10所示为调查Oracle数据库内文件的I/O的SQL。图1-10调查Oracle数据库内文件通过上述分析结果,可采取的措施包括:将 /oracle上数据文件的一部分移至有其他控制器的挂载点,通过移动 RBS、TEMP、USERS中一两个数据文件使 I/O平衡并分散。该操作非一次性操作,分配一次后要重新进行监测,确定 I/O是否分散均衡。......

2023-11-01

相关推荐