MCS-51单片机的算术运算类指令包括加、减、乘、除、加1、减1等指令。这类指令有ADD、ADDC、INC、SUBB、DEC、DA、MUL、DIV共8种。表3-3算术运算类指令注:√表示该指令影响某一标志位。运算结果对PSW的影响同上述4条ADD指令。6.十进制调整指令十进制调整指令只有以下1条:该指令用于BCD码加法运算时,对BCD码的加法运算结果自动进行调整,但对BCD码的减法运算不能用此指令来调整。在运算过程中,单片机按二进制规则进行运算。......

2023-11-17

如果有人问起在当今微控制器领域中,哪一款芯片对业界的影响力最大?那答案肯定是Intel(英特尔)公司的8051系列单片机。从20世纪80年代开始,8051系列单片机以惊人的速度迅速成长,并成为一种行业标准。

MCS-51系列单片机产品有8051、8031、8751、80C51、80C31等型号(前三种为CMOS芯片,后两种为CHMOS芯片)。它们的结构基本相同,其主要差别反映在存储器的配置上。8051内部设有4 KB的掩模ROM程序存储器,8031片内没有程序存储器,而8751是将8051片内的ROM换成EPROM。由Atmel公司生产的89C51将EPROM改成了4 KB的闪速存储器,它们的结构大同小异。

1.1.1 MCS-51单片机的基本组成

单片微型计算机简称单片机,是典型的嵌入式微控制器(Microcontroller Unit),常用缩写MCU表示,由运算器、控制器、存储器、输入/输出设备构成,相当于一个微型的计算机(最小系统)。与计算机相比,单片机缺少了外围设备等。概括地讲:一块芯片就成了一台计算机,它的体积小、质量小、价格便宜,从而为学习、应用和开发提供了便利条件。

51单片机通常指的是兼容Intel MCS-51体系架构的一系列单片机,而51是它的一个通俗的简称。全球有众多的半导体厂商推出了无数款这一系列的单片机,如Atmel(爱特梅尔)公司的AT89C52,NXP(恩智浦半导体)公司的P89V51,宏晶科技的STC89C52等。具体型号千差万别,但它们的基本原理和操作都是一样的,程序开发环境也是一样的。

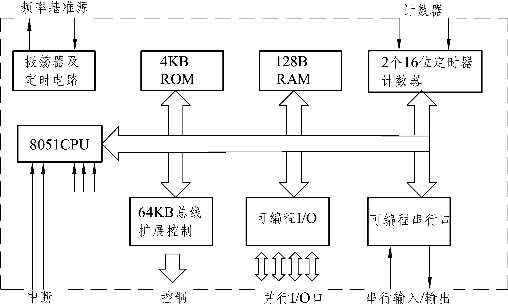

MCS-51单片机是在一块芯片中集成了CPU、RAM、ROM、定时器/计数器和多种功能的I/O端口等计算机所需要的基本功能部件。MCS-51单片机包含下列几个部件:

(1)1个8位CPU。

(2)1个片内振荡器及时钟电路。

(3)4 KB ROM程序存储器。

(4)128 B RAM数据存储器。

(5)2个16位定时器/计数器。

(6)可寻址64 KB外部数据存储器和64 KB外部程序存储器空间的控制电路。

(7)32个可编程的I/O端口(4个8位并行I/O端口)。

(8)1个可编程全双工串行口。

8051单片机框图如图1-2所示。各功能部件由内部总线连接在一起。

图1-2 8051单片机框图

图1-2中4 KB(4096)的ROM存储器部分用EPROM替换就成为8751的结构图;图1-2中去掉ROM部分就成为8031的结构图。

1.CPU

CPU是单片机的核心部件,它由运算器和控制器等部件组成。

1)运算器

运算器的功能是进行算术运算和逻辑运算,可以对半字节(4位)、单字节(8位)等数据进行操作。例如,能完成加、减、乘、除、加1、减1、BCD码十进制调整、比较等算术运算和与、或、异或、求补、循环等逻辑操作,操作结果的状态信息送至状态寄存器。

8051运算器还包含一个布尔处理器,用来处理位操作。它是以进位标志位C为累加器的,可执行置位、复位、取反、等于1转移、等于0转移、等于1转移且清0,以及进位标志位与其他可寻址的位之间进行数据传送等位操作,也能使进位标志位与其他可位寻址的位之间进行逻辑与、或操作。

2)程序计数器PC

程序计数器PC用来存放即将要执行的指令地址,共16位,可对64 KB程序存储器直接寻址。执行指令时,PC内容的低8位经P0口输出,高8位经P2口输出。

3)指令寄存器

指令寄存器中存放指令代码。CPU执行指令时,由程序存储器中读取的指令代码送入指令寄存器,经译码后由定时与控制电路发出相应的控制信号,完成指令功能。

4)定时与控制部件

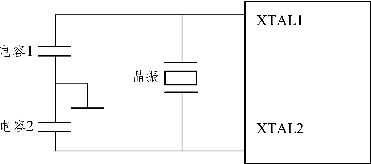

(1)时钟电路。

8051片内设有一个由反向放大器所构成的振荡电路,XTAL1和XTAL2分别为振荡电路的输入和输出端,时钟可以由内部方式产生或外部方式产生。内部方式时钟电路如图1-3所示。在XTAL1和XTAL2引脚上外接定时元件,内部振荡电路就产生自激振荡。定时元件通常采用石英晶体和电容组成的并联谐振回路。晶振可以在1.2~12 MHz范围内选择,电容值在5~30 pF范围内选择,电容的大小可起频率微调作用。

图1-3 内部方式时钟电路

外部方式的时钟很少用,若要用时,只需要将XTAL1接地,XTAL2接外部振荡器就行。对外部振荡信号无特殊要求,只要保证脉冲宽度,一般采用频率低于12 MHz的方波信号即可。

时钟发生器把振荡频率两分频,产生一个两相时钟信号P1和P2供单片机使用。P1在每一个状态S的前半部分有效,P2在每个状态的后半部分有效。

(2)时序。

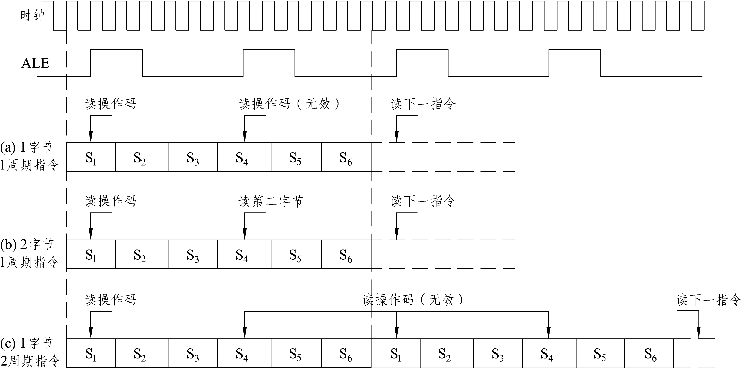

MCS-51典型的指令周期(执行一条指令的时间称为指令周期)为一个机器周期,一个机器周期由六个状态(十二振荡周期)组成。每个状态又被分成两个时相P1和P2。所以,一个机器周期可以依次表示为S1P1,S1P2,…,S6P1,S6P2。通常算术逻辑操作在P1时相进行,而内部寄存器传送在P2时相进行。

图1-4给出了8051单片机的取指和执行指令的定时关系。这些内部时钟信号不能从外部观察到,所用XTAL2振荡信号仅供参考。在图1-4中可以看到,低8位地址的锁存信号ALE在每个机器周期中两次有效:一次在S1P2与S2P1期间,另一次在S4P2与S5P1期间。

对于单周期指令,当操作码被送入指令寄存器时,便从S1P2开始执行指令。如果是双字节单机器周期指令,则在同一机器周期的S4期间读入第二个字节,若是单字节单机器周期指令,则在S4期间仍进行读操作,但所读的这个字节操作码被忽略,程序计数器也不加1,在S6P2结束时完成指令操作。图1-4的(a)和(b)给出了单字节单机器周期和双字节单机器周期指令的时序。8051指令大部分在一个机器周期完成。乘(MUL)和除(DIV)指令是仅有的需要两个以上机器周期的指令,占用4个机器周期。对于双字节单机器周期指令,通常是在一个机器周期内从程序存储器中读入两个字节,唯有MOVX指令例外。MOVX是访问外部数据存储器的单字节双机器周期指令。在执行MOVX指令期间,外部数据存储器被访问且被选通时跳过两次取指操作。图1-4(c)给出了一般单字节双机器周期指令的时序。

图1-4 8051时序

2.存储器

MCS-51单片机的程序存储器和数据存储器空间是互相独立的,物理结构也不同。程序存储器为只读存储器(ROM)。数据存储器为随机存取存储器(RAM)。单片机的存储器编址方式采用与工作寄存器、I/O口锁存器统一编址的方式。有关存储器的内容将在后面详述。

3.I/O端口

I/O端口又称为I/O接口,也叫作I/O通道或I/O通路。I/O端口是MCS-51单片机对外部实现控制和信息交换的必经之路,I/O端口有串行和并行之分,串行I/O端口一次只能传送一位二进制信息,并行I/O端口一次能传送一组二进制信息。(www.chuimin.cn)

1)并行I/O端口

MCS-51单片机设有4个8位双向I/O端口(P0、P1、P2、P3),每一条I/O线都能独立地用作输入或输出。P0口为三态双向口,能带8个LSTTL电路。P1、P2、P3口为准双向口(在用作输入线时,口锁存器必须先写入“1”,故称为准双向口),负载能力为4个LSTTL电路。

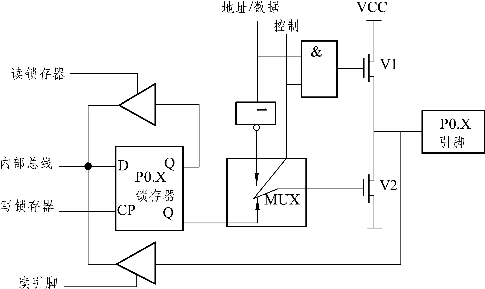

(1)P0端口功能(P0.0~P0.7,即32~39脚)。

图1-5是P0口位结构,包括1个输出锁存器、2个三态缓冲器、1个输出驱动电路和1个输出控制端。输出驱动电路由1对场效应管组成,其工作状态受输出端的控制,输出控制端由1个与门、1个反相器和1个转换开关MUX组成。对于8051/8751来说,P0口既可作为输入/输出口,又可作为地址/数据总线使用。

① P0口作通用I/O端口使用。

对于有内部ROM的单片机,P0口可以作为通用I/O,此时控制端为低电平,转换开关把输出端与锁存器的Q端接通,同时因与门输出为低电平,输出端V1管处于截止状态,输出端为漏极开路电路,在驱动NMOS(N型金属氧化物半导体)电路时应外接上拉电阻。PO口作输入口用时,应先将锁存器写“1”,这时输出端两个场效应管均截止,可作高阻抗输入,通过三态输入缓冲器读取引脚信号,从而完成输入操作。

② P0口作地址/数据复用总线使用。

若从P0口输出地址或数据信息,此时控制端应为高电平,转换开关MUX将反相器输出端与输出级场效应管V2接通,同时与门开锁,内部总线上的地址或数据信号通过与门去驱动V1管,又通过反相器去驱动V2管,这时内部总线上的地址或数据信号就传送到P0口的引脚上。工作时低8位地址与数据线分时使用P0口。低8位地址由ALE信号的负跳变使它锁存到外部地址锁存器中,而高8位地址由P2口输出。

③ PO口线上的“读-修改-写”功能。

图1-5上面的一个三态缓冲器是为了读取锁存器Q端的数据。Q端与引脚的数据是一致的。结构上这样安排是为了满足“读-修改-写”指令的需要,这类指令的特点是:先读口锁存器,随之可能对读入的数据进行修改再写入到端口上。

图1-5 P0口位结构

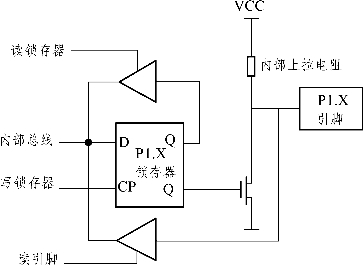

(2)P1口(P1.0~P1.7,即1~8脚)。

① P1口作通用I/O端口使用。

P1口是一个有内部上拉电阻的准双向口,位结构如图1-6所示。P1口的每一位口线能独立用作输入线或输出线。P1口作输出时,如将“0”写入锁存器,场效应管导通,输出线为低电平,即输出为“0”。因此,P1口作输入时,必须先将“1”写入口锁存器,使场效应管截止。该口线由内部上拉电阻提拉成高电平,同时也能被外部输入源拉成低电平,即当外部输入“1”时,该口线为高电平;而输入“0”时,该口线为低电平。P1口作输入时,可被任何TTL电路和MOS电路驱动,由于具有内部上拉电阻,也可以直接被集电极开路和漏极开路电路驱动,不必外加上拉电阻。P1口可驱动4个LSTTL门电路。

图1-6 P1口位结构

② P1口其他功能。

P1口在EPROM编程和验证程序时,它输入低8位地址。在8032/8052系列中P1.0和P1.1是多功能的,P1.0可作定时器/计数器2的外部计数触发输入端T2,P1.1可作定时器/计数器2的外部控制输入端T2EX。

(3)P2口(P2.0~P2.7,即21~28脚)。

P2口的位结构如图1-7所示,引脚上拉电阻同P1口。在结构上,P2口比P1口多一个输出控制部分。

图1-7 P2口位结构

① P2口作通用I/O端口使用。

当P2口作通用I/O端口使用时,是一个准双向口,此时转换开关MUX倒向左边,输出端与锁存器接通,引脚可接I/O设备,其输入/输出操作与P1口完全相同。

② P2口作地址总线口使用。

当系统中接有外部存储器时,P2口用于输出高8位地址A15~A8。这时在CPU的控制下,转换开关MUX倒向右边,接通内部地址总线。P2口的口线状态取决于片内输出的地址信息,这些地址信息来源于PCH、DPH等。在外接程序存储器的系统中,由于访问外部存储器的操作连续不断,P2口不断送出地址高8位。例如,在8031构成的系统中,P2口一般只作地址总线口使用,不再作I/O端口直接连接外部设备。

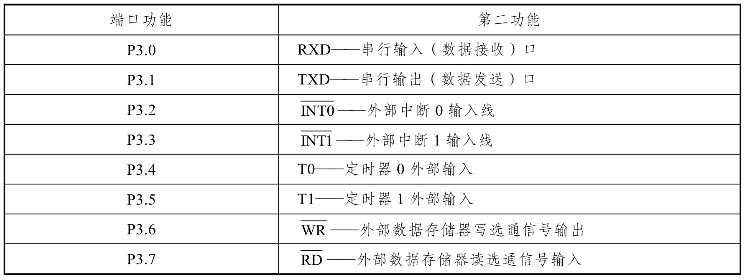

(4)P3口(P3.0~P3.7,即10~17脚)。

P3口是一个多用途的端口,也是一个准双向口,作为第一功能使用时,其功能同P1口。P3口的位结构如图1-8所示。

图1-8 P3口位结构

当P3口作第二功能使用时,每一位功能定义如表1-2所示。P3口的第二功能实际上就是系统具有控制功能的控制线。此时相应的口线锁存器必须为“1”状态,与非门的输出由第二功能输出线的状态确定,从而P3口线的状态取决于第二功能输出线的电平。在P3口的引脚信号输入通道中有两个三态缓冲器,第二功能的输入信号取自第一个缓冲器的输出端,第二个缓冲器仍是第一功能的读引脚信号缓冲器。P3口可驱动4个LSTTL门电路。

表1-2 P3口的第二功能

每个I/O端口内部都有一个八位数据输出锁存器和一个八位数据输入缓冲器,四个数据输出锁存器与端口号P0、P1、P2和P3同名,皆为特殊功能寄存器。因此,CPU数据从并行I/O端口输出时可以得到锁存,数据输入时可以得到缓冲。

四个并行I/O端口作为通用I/O口使用时,共有写端口、读端口和读引脚三种操作方式。写端口实际上就是输出数据,是将累加器A或其他寄存器中的数据传送到端口锁存器中,然后由端口自动从端口引脚线上输出。读端口不是真正地从外部输入数据,而是将端口锁存器中输出数据读到CPU的累加器。读引脚才是真正的输入外部数据的操作,是从端口引脚线上读入外部的输入数据。端口的上述三种操作实际上是通过指令或程序来实现的,这些将在后面详细介绍。

2)串行I/O端口

8051有一个全双工的可编程串行I/O端口。这个串行I/O端口既可以在程序控制下将CPU的八位并行数据变成串行数据一位一位地从发送数据线TXD发送出去,也可以把串行接收到的数据变成八位并行数据送给CPU。这种串行发送和串行接收可以单独进行,也可以同时进行。

8051串行发送和串行接收利用了P3口的第二功能,即利用P3.1引脚作为串行数据的发送线TXD和P3.0引脚作为串行数据的接收线RXD,如表1-1所示。串行I/O端口的电路结构还包括串行口控制器SCON、电源、波特率选择寄存器PCON和串行数据缓冲器SBUF等,它们都属于特殊功能寄存器SFR。其中PCON和SCON用于设置串行口工作方式和确定数据的发送和接收波特率,SBUF实际上由两个八位寄存器组成,一个用于存放欲发送的数据,另一个用于存放接收到的数据,起着数据的缓冲作用。

4.总 线

MCS-51单片机属于总线型结构,通过地址/数据总线可以与存储器(RAM、EPROM)、并行I/O接口芯片相连接。

在访问外部存储器时,P2口输出高8位地址,P0口输出低8位地址,由ALE(地址锁存允许)信号将P0口(地址/数据总线)上的低8位锁存到外部地址锁存器中,从而为P0口接收数据做准备。

在访问外部程序存储器指令时,PSEN(外部程序存储器选通)信号有效,在访问外部数据存储器指令时,由P3口自动产生读/写信号,通过P0口对外部数据存储器单元进行读/写操作。

MCS-51单片机所产生的地址、数据和控制信号与外部存储器、并行I/O接口芯片连接简单、方便。

有关单片机原理与应用 基于C语言的文章

MCS-51单片机的算术运算类指令包括加、减、乘、除、加1、减1等指令。这类指令有ADD、ADDC、INC、SUBB、DEC、DA、MUL、DIV共8种。表3-3算术运算类指令注:√表示该指令影响某一标志位。运算结果对PSW的影响同上述4条ADD指令。6.十进制调整指令十进制调整指令只有以下1条:该指令用于BCD码加法运算时,对BCD码的加法运算结果自动进行调整,但对BCD码的减法运算不能用此指令来调整。在运算过程中,单片机按二进制规则进行运算。......

2023-11-17

8051有5个中断源,即两个外部中断、两个定时/计数器中断和一个串行发送/接收中断。1.外部中断外部中断是由连接到单片机外部引脚信号变化而引起的中断,反映外部某一事件的发生。CPU是在每个机器周期的S5P2检测P 3.2和P 3.3上的信号,如果是有效信号则对定时器控制寄存器TCON中的IE0或IE1置1,建立中断请求标志。表6-1中断源的主要内容及说明......

2023-11-17

目前在单片机市场上,8位单片机和32位的ARM嵌入式微处理器占据的市场份额达70%以上。在单片机市场中,代表性的产品有MCS-51系列产品,其中ATMEL公司的AT89C51/C52两个系列8位单片机在焊接领域应用较为广泛。1994年ATMEL公司以其E2PROM和Intel公司的80C31单片机核心技术进行交换,从而取得80C31核的使用权。......

2023-06-26

1.基本组成微型计算机的基本组成如图1-2所示。图1-2微型计算机的组成框图中央处理器CPUCPU是计算机的核心部件,它由运算器和控制器组成,完成计算机的运算和控制功能。电池式NVRAM是由CMOS的SRAM、备用电池和切换电路组成,在电源断开或低于某值时切换电路把备用电池接入,对RAM进行写保护,防止意外数据写入和信息丢失。......

2023-11-17

程序存储器以程序计数器PC作为地址指针,通过16位地址总线,可寻址的地址空间为64KB,片内/外统一编址。根据单片机的类型及引脚的电平,CPU可从内部也可从外部程序存储器开始执行。而当EA=0时,内部程序存储器被忽略,程序直接从外部程序存储器的0000H开始执行。64KB程序存储器中有一些特殊的单元,在使用时应加以注意。0023H——串行口的中断服务子程序入口地址。......

2023-11-17

1.生产厂商常见的单片机生产厂商有Intel公司、Motorola公司、Philips公司、Atmel公司、Zilog公司、NEC公司、MicroChip公司、ADI公司、Epson公司、NS公司、AMD公司、WinBond公司、Scenix公司、Toshiba公司、Fujitsu公司、Samsung公司等。2.单片机系列常见的单片机系列有Intel公司的MCS-51、MCS-96/98系列,Motorola公司的68HC05、68HC5X、68HC12、68HC16、683XX系列,Philips公司的80C5X系列,Atmel公司的AT89系列,Zilog公司的Z8、Z86系列,ADI公司的MC-6801系列,MicroChip公司的PIC16CX、PIC16FX、PIC17CX、PIC18CX系列,NEC公司的μPD7800系列,Toshiba公司的MB8900、MB90系列等。......

2023-11-17

如果将单片机的一个I/O口连接于K点,通过检测K点电压的高低,就可以确认是否有按键按下,这就是键盘检测的基本原理。基于中断方式工作的独立键盘的电路原理如图6-8所示。矩阵键盘能有效地节省I/O口,简化电路,非常适用于按键数量较多的应用。......

2023-11-17

在单片机应用系统设计时,应按以下6条原则进行:1)明确设计目标。在整个设计过程中要不断地对照设计目标并满足目标要求。2)自上而下设计。3)软、硬件优化设计。大部分子任务可以以硬件为主实现也可以以软件为主实现,必须进行协调优化设计,从而提高性能质量,降低成本。6)组合及开放式设计。......

2023-11-17

相关推荐