嵌入式微处理器是由通用计算机中的CPU演变而来的。嵌入式微处理器及其存储器、总线、外设等安装在一块电路板上,称为单板计算机。据不完全统计,全世界的嵌入式微处理器已经超过1000多种,体系结构也有很多种类。但与全球PC市场不同的是,没有一种嵌入式微处理器可以主导市场,仅以32位的产品而言,就有100种以上的嵌入式微处理器。嵌入式微处理器的选择是根据具体的应用而决定的。......

2023-11-08

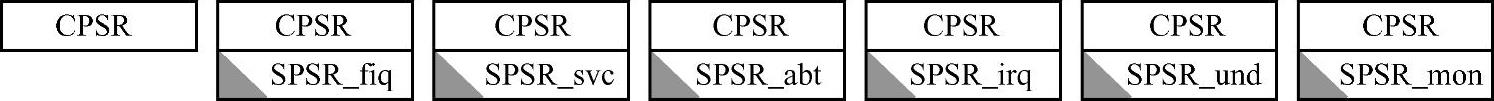

Cortex-A8处理器总共有40个32位长的寄存器,其中包括33个通用寄存器和7个状态寄存器。7个状态寄存器包括1个CPSR(Current Programs Status Register,当前程序状态寄存器)和6个SPSR(Saved Program Status Register,备份程序状态寄存器)。

这些寄存器不能同时访问,处理器状态和操作模式决定了哪些寄存器对编程者是可用的。具体如图3-2和图3-3所示。

1.通用寄存器组

如图3-2所示,R0~R7是不分组的通用寄存器,R8~R15是分组的通用寄存器。在ARM状态,任何时刻,16个数据寄存器R0~R15和1~2个状态寄存器是可访问的。在特权模式下,特定模式下的寄存器阵列才是有效的。

和ARM状态一样,Thumb和ThumbEE状态下也可以访问同样的寄存器集。但是其中16位指令对某些寄存器的访问是有限制的,32位的Thumb指令和ThumbEE指令则没有限制。

图3-2 ARM状态下Cortex-A8通用寄存器组

图3-3 ARM状态下Cortex-A8状态寄存器组

(1)未分组的通用寄存器R0~R7

16个数据寄存器中R0~R7是未分组的通用寄存器,用来保存数据和地址。

(2)分组寄存器

R8~R15是分组寄存器,当前处理器的模式不同决定了访问不同的物理寄存器,具体如下:

●R8~R12寄存器分别对应两个不同的物理寄存器,它们分别对应快速中断模式下的相应寄存器,以及除了快速中断其他模式下的相应寄存器。

●R13、R14是分组寄存器,每个寄存器分别对应7个不同的物理寄存器,除了用户和系统模式共用一个物理寄存器,其他6个分别是usr、svc、abt、und、irp、fiq以及mon模式下的不同物理寄存器。R13常作堆栈指针;R14子程序连接寄存器,当处理器执行BL和BLX指令时,R14可以保存返回地址。其他情况下,可以把它当作一个通用寄存器来使用。类似地,当处理器进入中断或异常时,或在中断和异常子程序中执行BL和BLX指令时,相关的寄存器R14_mon、R14_svc、R14_irq、R14_fiq、R14_abt、R14_und用来保存返回值。

●程序计数器R15(PC),在ARM状态下,PC字对齐;在Thumb状态和ThumbEE状态下,PC半字对齐。

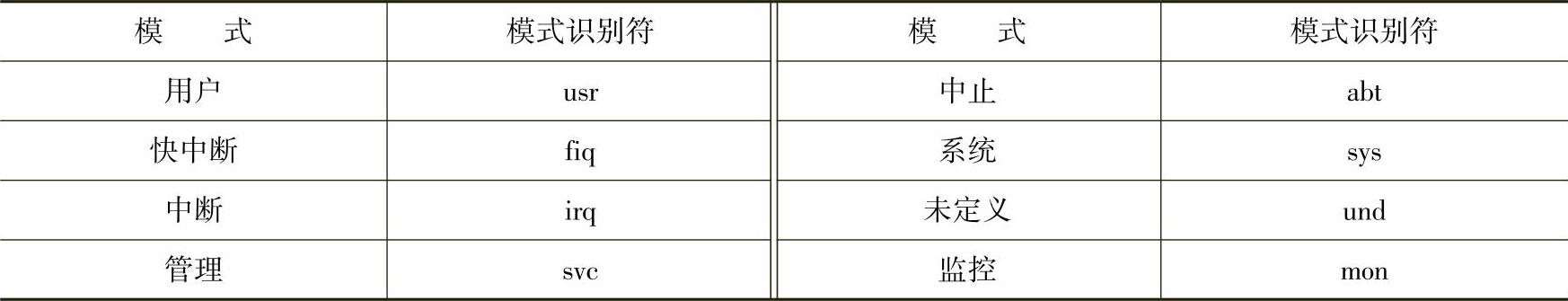

图3-2中的分组寄存器由模式标识符指示当前所处的操作模式,如表3-2所示。在寄存器名中,模式标识符usr通常省略。仅当处理器在另外的处理模式下,访问指定的usr或sys模式寄存器时,标识符usr才出现。

表3-2 寄存器模式标识符

快中断模式有7个分组寄存器映射到R8~R14,即R8_fiq~R14_fiq。因此,许多快速中断处理不需要保存任何寄存器。

监控、管理、中止、中断和未定义模式下,分别有指定寄存器映射到R13~R14,这使得每种模式都有自己的栈指针和链接寄存器。

2.状态寄存器

处理器有两类程序状态寄存器:1个当前程序状态寄存器CPSR和6个保存程序状态寄存器SPSR。这些程序状态寄存器主要功能如下:

●保存最近执行的算术或逻辑运算的信息。

●控制中断的允许或禁止。

●设置处理器操作模式。

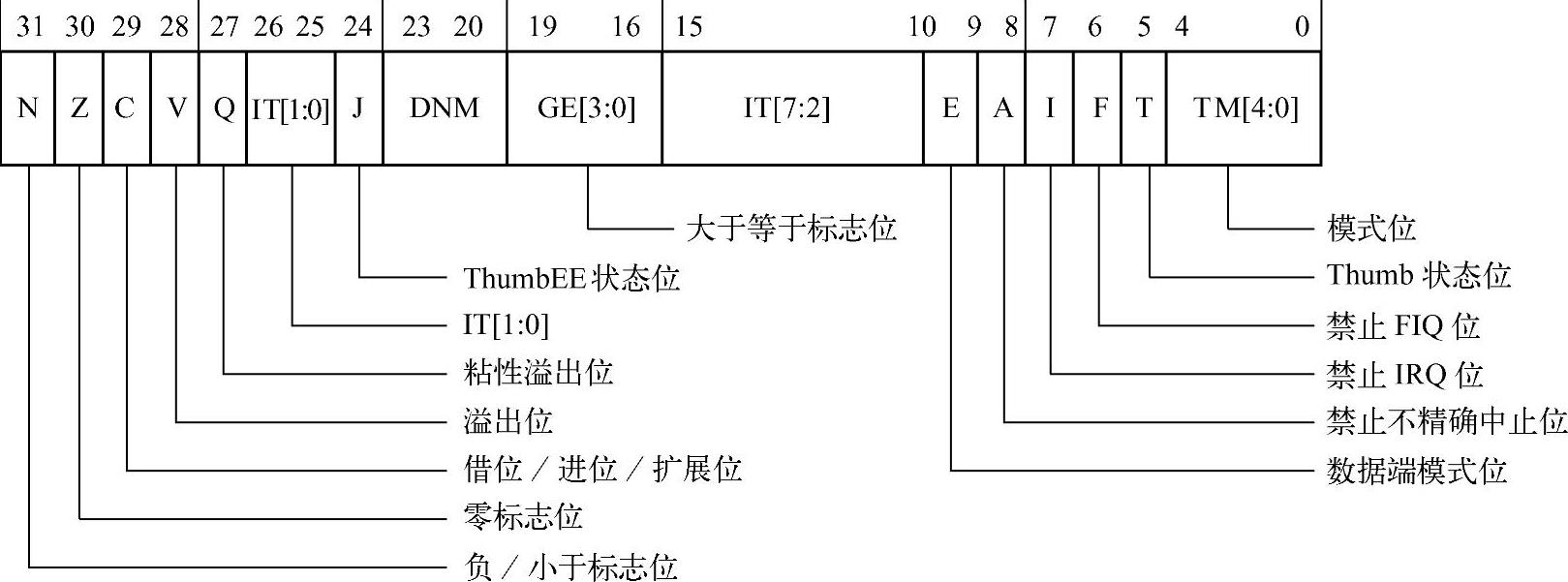

程序状态寄存器的位域如图3-4所示。

图3-4 程序状态寄存器的位域

为了保持与未来ARM处理器的兼容性,强烈建议在修改CPSR寄存器时使用“读-修改-写"的策略。

(1)条件标志位

N、Z、C、V是条件标志位,通过算术和逻辑操作可以设置它们,也可以通过MSR指令来设置。处理器通过测试这些标识位来确定一条指令是否执行。

在ARM状态,可以根据条件标志位的状态有条件地执行大多数指令。在Thumb状态,也可有条件地执行少数指令。但是在Thumb状态可以用IT指令使大多数指令有条件地执行。

(2)Q标志位

在带有DSP指令扩展的ARMv5及更高版本中,Q标志位被指定用于指示增强的DAP指令是否发生了溢出。Q标志位具有粘性,当因某条指令将其置为1时,它将一直保持为1直到通过MSR指令写CPSR寄存器明确地将该位清零,不能根据Q标志位的状态来有条件地执行某条指令。为了确定Q标志位的状态,必须通过读入PSR到一个寄存器,然后从中提取Q标志位。

(3)IT块(www.chuimin.cn)

IT块用于对thumb指令集中if-then-else这一类语句块的控制。如果有IT块,则IT[7:5]为当前IT块的基本条件码。在没有IT块处于活动状态时,这3位为000。IT[4:0]表示条件执行指令的数量,不论指令的条件是基本条件码还是基本条件的逆条件码。在没有IT块处于活动状态时,这5位是00000。当处理器执行IT指令时,通过指令的条件和指令中Then、Else(T和E)参数来设置这些位。

(4)J位

CPSR中的J位用于表示处理器是否处于ThumbEE状态。当T=1时,

●J=0,表示处理器处于Thumb状态。

●J=1,表示处理器处于ThumbEE状态。

注意,当T=0时,不能够设置J=1;当T=0时,J=0。不能通过MSR指令来改变CPSR的J位。

(5)GE[3:0]位

该位用于表示在SIMD指令集中的大于、等于标志。在任何模式下可读可写。

(6)E位

E位控制存取操作的字节顺序。0表示小端操作,1表示大端操作。ARM和Thumb指令集都提供指令用于设置和清除E位。当使用CFGEND0信号复位时,E位将被初始化。

(7)A位

A表示异步异常禁止。

(8)控制位

状态控制寄存器的低8位是控制位,有中断禁止位、T位和模式位。当异常发生时,控制位发生改变。当处理器处于特权模式时,软件可以操纵这些位。

1)中断屏蔽位。I位和F位是中断禁止位。

当I位置为1时,IRQ中断被禁止。

当F位置为1时,FIQ中断被禁止。

2)T位。T位反映了操作状态。

当T位被置为1时,J位决定处理器是在Thumb还是在ThumbEE状态下执行。

当T位被清0时,说明处理器正在ARM状态下执行。

注意,不要用MSR指令来强行修改CPSR的T位状态。如果强行用MSR指令修改该位,其结果不可预知。

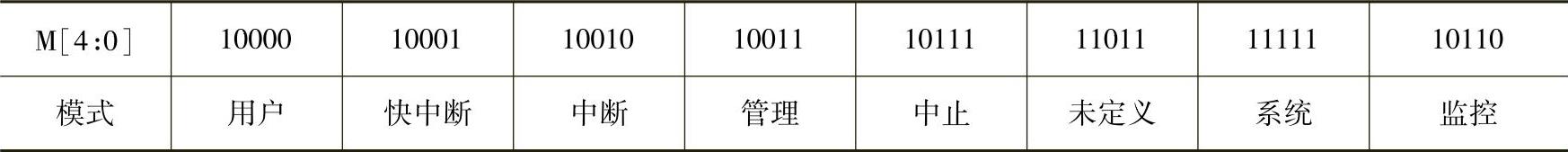

●模式位

TM[4:0]是模式位,这些位决定处理器操作模式,如表3-3所示。

表3-3 模式位的设置

(9)通过MSR指令改变PSR位

在以前的体系结构版本中,MSR指令可以在任何模式下改变CPSR的标志字节,即[31:24]位,但是其他3个字节只能在特权模式下改变。

从ARMv6之后,对CPSR中各位的修改采取以下策略中的一种:

●对于可以被MSR指令修改的位,可以在任何模式下改变位,不论是直接通过MSR指令还是通过其他具有写指令位或改变整个CPSR功能的指令来修改。这一类位包含:N、Z、C、V、Q、GE[3:0]和E位。

●对于不能被MSR指令改变的位,则只能因其他指令的副作用而修改。如果一条MSR指令非要试着修改这个位的话,结果是不可预知的。这一类包含J和T位。

●对于只能在特权模式下才能修改的位,处理器在用户模式下不能通过指令修改它。当处理器处于用户模式时,唯一能够改变这些位的方法就是进入一个处理器异常。这一类位包含A、I、F、M[4:0]。

●只有安全的特权模式下才能通过直接写CPSR的模式位进入Monitor模式。如果内核处于安全的User模式、非安全的User模式或不安全的特权模式,则它将忽略为了进入监控模式而对CPSR进行的改变。

(10)保留位

在状态寄存器中剩下的位是不使用和保留的。当希望改变一个PSR的标志位或控制位时,最好确保没有改变保留位,这将确保程序不依赖这些保留位,因为未来的处理器或许会用到一些或全部的保留位。

嵌入式微处理器是由通用计算机中的CPU演变而来的。嵌入式微处理器及其存储器、总线、外设等安装在一块电路板上,称为单板计算机。据不完全统计,全世界的嵌入式微处理器已经超过1000多种,体系结构也有很多种类。但与全球PC市场不同的是,没有一种嵌入式微处理器可以主导市场,仅以32位的产品而言,就有100种以上的嵌入式微处理器。嵌入式微处理器的选择是根据具体的应用而决定的。......

2023-11-08

Cortex-A8处理器有40个32位寄存器,分为33个通用寄存器和7个程序状态寄存器。表2.4ARM状态下Cortex-A8寄存器组②R13是堆栈指针寄存器,用于指向堆栈区的栈顶。表2.5程序状态寄存器位格式条件代码标志位N、Z、C和V位都是条件代码标志。......

2023-11-19

每组GPIO端口都有两类控制寄存器,分别工作在正常模式和掉电模式。S5PV210处理器工作在正常模式下时,正常寄存器工作;进入掉电模式时,所有配置和上拉/下拉控制由掉电寄存器控制。用于控制GPIO的引脚功能,向该寄存器写入数据来设置相应引脚是输入/输出,还是其他功能。GPIO数据寄存器GPxnDAT。GPIO上拉/下拉寄存器GPxnPUD,用于控制每个端口上拉/下拉电阻的使能/禁止。......

2023-11-19

由于Linux系统本身具备的特点,使得开源嵌入式操作系统很容易推广并且得到不断的完善。随着嵌入式系统的发展,嵌入式系统的人机交互功能越来越强大,多媒体人机界面逐渐成为嵌入式系统的主要人机交互方式。......

2023-11-08

ARM微处理器目前包括下面几个系列。其中,ARM7TMDI是目前使用最广泛的32位嵌入式RISC处理器,属低端ARM处理器核。ARM10E系列微处理器主要应用于下一代无线设备、数字消费品、成像设备、工业控制、通信和信息系统等领域。......

2023-11-08

例如,在Windows操作系统下搭建基于YAGARTO开发工具链的Eclipse for ARM开发平台的步骤如下:1)安装YAGARTO GCC编译工具。指定一个工程存放目录Eclipse for ARM是一个标准的窗口应用程序,可以单击程序按钮开始运行。......

2023-11-08

DSP处理器是专门用于信号处理方面的处理器。DSP处理器对系统结构和指令进行了特殊设计,使其适合于执行DSP算法。DSP的理论算法在20世纪70年代就已经出现,但是由于专门的DSP处理器还未出现,所以这种理论算法只能通过MPU等元件实现。嵌入式DSP处理器比较有代表性的产品是Texas Instruments公司的TMS320系列和Mo-torola公司的DSP56000系列。DSP56000目前已经发展成为DSP56000、DSP56100、DSP56200和DSP56300等几个不同系列的处理器。......

2023-11-08

Cortex-A8处理器是一款适用于复杂操作系统及用户应用的应用处理器,已在工业控制、医疗电子、节能环保、智能交通、能源节能、电力系统、通信系统等环境恶劣场合广泛应用。Cortex-A8处理器包含以下4种外部接口。......

2023-11-19

相关推荐