( )7.基本RS触发器和同步RS触发器的共同缺点是存在不定状态和空翻现象。( )9.三极管的输出特性是指三极管的VBE一定时,输出电流ic与输出电压VCE之间的关系。( )11.场效应管的输出特性曲线有可调电阻区、放大区、饱和区。第2题图五、综合题某超市举行一次促销活动,只要顾客拿着购物发票,就可以参加这项活动。......

2023-10-21

1.基本RS触发器。(B)

2.同步RS触发器。(B)

3.触发器的常用触发方式(同步式触发、上升沿触发、下降沿触发、主从触发)。(B)

4.JK触发器的电路组成和图形符号。(B)

5.JK触发器的逻辑功能。(C)

6.集成JK触发器。(A)

7.D触发器的电路组成和图形符号。(B)

8.D触发器的逻辑功能分析。(C)

9.集成D触发器及其应用。(B)

10.T触发器的电路组成。(A)

11.T触发器的逻辑功能。(B)

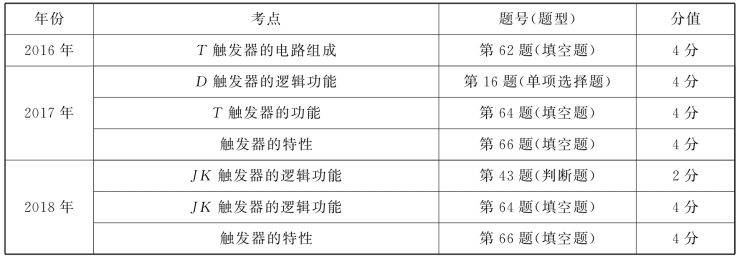

近三年四川省对口升学本章考点内容及考题分析

触发器是组成时序逻辑电路的基本单元,掌握触发器的电路组成,逻辑功能和状态方程的应用是学好后续时序逻辑电路的关键。本章在高考中多以客观题出现,也会以大题时序逻辑电路的分析出现,在复习过程中掌握单个触发器的逻辑功能和灵活应用状态方程是解题关键。

一、触发器的工作特性

1.触发器是组成时序逻辑电路的必不可少的基本单元。

2.具有记忆功能。

3.具有两个稳态“0”和“1”。

4.一个触发器能够存储一位二进制,则有N个触发器存储N位二进制。(一个触发器输出Q:0和1,一位二进制:0和1,即一个触发器能存储一位二进制)。

5.触发器的输出不仅与该时刻的输入有关,还与电路之前的状态有关。如:![]()

![]() 。

。

6.触发器的输出端Q的状态为触发器的状态。

二、基本RS触发器

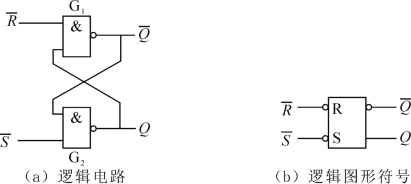

1.逻辑电路和逻辑图形符号(如图2-12-1所示)

图2-12-1 基本RS触发器

(1)输入端:![]() (低电平有效)

(低电平有效)

输出端:![]()

(2)触发器的状态:![]() ),处于0态;

),处于0态;![]() ,处于1态。

,处于1态。

2.逻辑功能分析与总结

(1)![]() :置0端,有效就置

:置0端,有效就置![]() :置1端,有效就置1(Q=1)。

:置1端,有效就置1(Q=1)。

(2)![]() :低电平有效0,R、S:高电平有效_。

:低电平有效0,R、S:高电平有效_。

(3)逻辑功能总结;![]() 有效,则Q置0;

有效,则Q置0;![]() 有效,则Q置1;输入端都无效,则Q保持;输入端都有效,则Q不确定,见表2-12-1、表2-12-2。

有效,则Q置1;输入端都无效,则Q保持;输入端都有效,则Q不确定,见表2-12-1、表2-12-2。

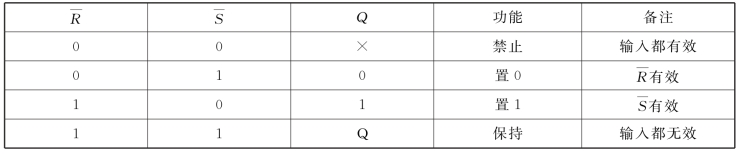

表2-12-2 或非门构成的基本RS触发器的逻辑功能真值表

3.约束条件

(1)与非门构成的基本RS触发器:![]() 。

。

(2)或非门构成的基本RS触发器:R×S=0。

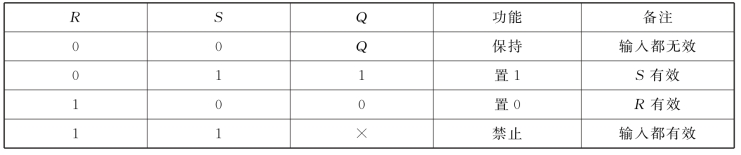

三、同步RS触发器

1.受CP控制的RS触发器,又称钟控RS触发器。

2.电路结构

在基本RS触发器的基础上增加两个与非门,两个与非门都受CP控制。

3.逻辑电路和逻辑图形符号(如图2-12-2所示)

图2-12-2 同步RS触发器

4![]() :异步置0端,低电平有效,不受输入和CP控制,即

:异步置0端,低电平有效,不受输入和CP控制,即![]() 。

。

![]() :异步置1端,低电平有效,不受输入和CP控制,即

:异步置1端,低电平有效,不受输入和CP控制,即![]() 。

。

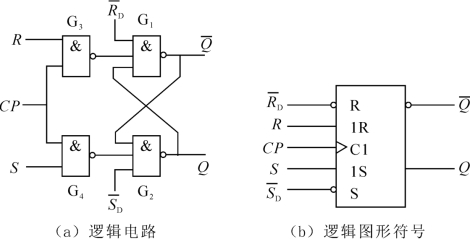

5.工作原理(见表2-12-3)

(1)CP=0,Q n+1=Q n保持。

(2)CP=1,根据输入S,R的状态决定Q n+1的状态。

表2-12-3 同步RS触发器真值表

四、触发器的触发方式

1.同步式触发

(1)特点:采用电平触发,一般为高电平触发,即CP=1期间,输入信号起作用。

(2)存在空翻现象:CP=1期间,输出随输入不断变化,而可能发生变化。

2.上升沿触发:CP上升沿时刻根据输入信号变化,一个CP周期内触发器只动作一次,可以避免空翻现象。

3.下降沿触发:CP下降沿时刻根据输入信号变化,一个CP周期内触发器只动作一次,可以避免空翻现象。

4.主从触发:具有CP=1期间接收输入信号,CP下降沿时刻根据输入信号变化的特点,可以避免空翻现象。

五、JK触发器

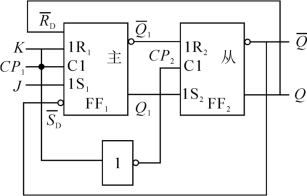

1.电路组成:如图2-12-3所示,由两个钟控RS触发器和非门组成。

图2-12-3 JK触发器电路图

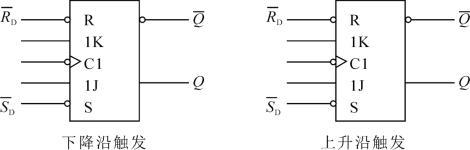

2.逻辑符号(如图2-12-4所示)

图2-12-4 JK触发器逻辑图形符号

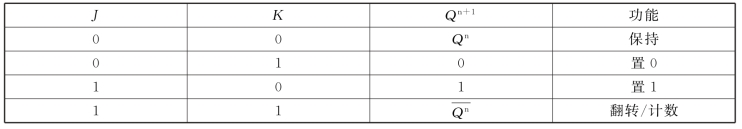

3.真值表(见表2-12-4)

表2-12-4 JK触发器真值表

4.状态方程(特性方程):![]() 。

。

5.集成JK触发器

实际应用中,JK触发器大多采用集成电路,集成双JK触发器74LS76,其他型号的JK触发器有74LS70,74H72,74LS73,74111,74H71,实际使用中注意引脚顺序。

六、D触发器

1.电路组成_:JK触发器的K端串接一个非门后与J端相连,作为输入端D,即K= ,J=D,也有K=

,J=D,也有K= 。

。

2.逻辑图形符号(如图2-12-5所示)

图2-12-5 D触发器逻辑图形符号

3.逻辑功能分析

(1)CP未到,触发器保持。

(2)CP到来,Q n+1=D,D=0,触发器置0;D=1,触发器置1。(www.chuimin.cn)

4.状态方程:Q n+1=D。

5.集成D触发器

D触发器有TTL和CMOS型两类。TTL型双D触发器74LS74,常用的有四D触发器74LS175,八D触发器74LS273,实际应用中注意引脚顺序。

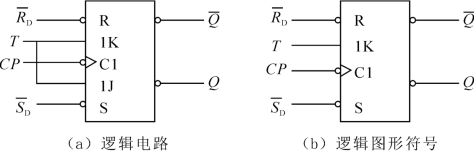

七、T触发器

1.电路组成

将JK触发器的输入端J、K连接在一起,作为输出端T,即J=K=T。

2.逻辑电路和逻辑图形符号(如图2-12-6所示)

图2-12-6 T触发器

3.逻辑功能分析

(1)T=0,则Q n+1=Q n,触发器保持原态不变。

(2)T=1,则![]() ,触发器状态翻转,为计数状态。

,触发器状态翻转,为计数状态。

4.状态方程:![]() 。

。

【例1】 (2017年高考真题)只具有保持和翻转功能的触发器是________触发器。

【答案】 T

【解析】 根据题目中只具有保持和翻转功能的触发器的要求,应该为T触发器。T=0,保持;T=1,翻转。

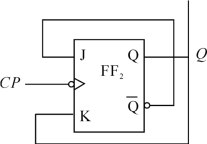

【例2】 如图所示,试分析触发器的逻辑功能。

【答案】 解:第一步:写出触发器的驱动方程

![]()

第二步:将驱动方程代入标准的状态方程,得到触发器的状态方程

![]()

根据状态方程可知逻辑功能:翻转,即CP到来,触发器Q翻转一次。

【解析】 本题考查知识点是JK触发器的逻辑功能。触发器的功能可以通过状态方程来判断。

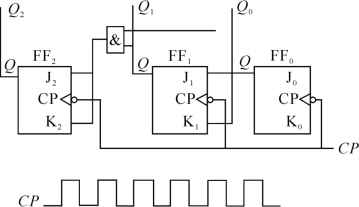

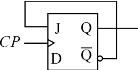

【例3】 在如图所示的电路中,设触发器的初始状态均为“0”,试画出输出Q0、Q1、Q2的波形。

【答案】 第一步:写出触发器的驱动方程

FF0中:J0=K0=1

FF1中:J1=K1=Q0

FF2中:J2=K2=Q0Q1。

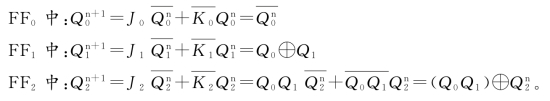

第二步:将驱动方程代入标准的状态方程,得到触发器的状态方程

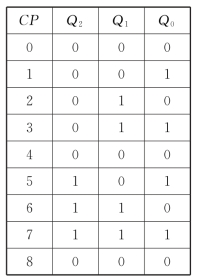

第三步:根据状态方程列出状态转换表(真值表)。

第四步:根据状态转换表画出输出波形。

一、单项选择题

1.关于触发器的工作特性,下列说法错误的是( )

A.触发器是组成时序逻辑电路的基本单元

B.具有记忆功能

C.具有两个稳态“0”和“1”

D.触发器的输出仅与该时刻的输入有关

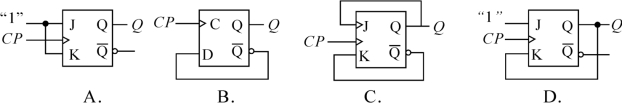

2.下列选项中所有触发器的初始状态皆为0,触发器在时钟信号作用下,输出电压波形恒为0的是( )

3.由与非门构成的基本RS触发器,要使Q n+1=0的输入信号应为( )

A.S=R=0 B.S=R=1

C.S=1,R=0 D.S=0,R=1

第4题图

4.触发器电路如图所示,其状态方程为( )

A.Q n+1=Q n

B.Q n+1=1

C.Q n+1=![]()

D.Q n+1=D

5.将TTL型JK触发器的两输入端均悬空,则触发器的逻辑功能为( )

A.置0 B.置1 C.保持 D.翻转

二、判断题(正确的选“A”,错误的选“B”)

1.要存储4位二进制,需要16个触发器。( )

2.边沿触发器和主从触发器能避免空翻现象。( )

3.对于JK触发器,当J=K=1时,CP未到,触发器输出Q翻转。( )

4.D触发器的输出状态始终与输入状态相同。( )

5.将JK触发器的JK端连接在一起作为输入端,就构成了D触发器。( )

三、填空题

1.触发器是构成________的基本单元,其与组合逻辑最大的区别是具有________,每个触发器能够存储_________位二值信息。

2.基本RS触发器具有_________、_________和_________三种功能。

3.同步RS触发器是在基本RS触发器的基础上,增加了两个_________门。输出不仅受输入信号的影响,还要受_________控制。

4.集成触发器中,异步置0端为________,异步置1端为________,它们不受________控制。

5.JK触发器具有_________、_________、_________和_________四种逻辑功能。

6.基本RS触发器当![]() 作为输入端时的约束条件为_________,当R、S作为输入端时的约束条件为________。

作为输入端时的约束条件为_________,当R、S作为输入端时的约束条件为________。

7.D触发器的逻辑功能_________是和_________。

8.基本RS触发器,当![]() 都接高电平时,该触发器具有________逻辑功能。

都接高电平时,该触发器具有________逻辑功能。

9.D触发器的特性方程为_________;JK触发器的特性方程为_________;T触发器的特性方程为________。

10.由4个触发器构成的4位二进制计数器中,若CP的脉冲频率为64 MHz,则最高位触发器Q端输出信号的频率为________。

四、综合题

1.图中所有触发器的初始状态为0,分析逻辑功能并画出4个CP作用下Q端的输出波形。

第1题图

2.设触发器的初态均为0,画出4个CP作用下Q1,Q2的波形。

第2题

有关对口升学 信息技术二类专业总复习的文章

( )7.基本RS触发器和同步RS触发器的共同缺点是存在不定状态和空翻现象。( )9.三极管的输出特性是指三极管的VBE一定时,输出电流ic与输出电压VCE之间的关系。( )11.场效应管的输出特性曲线有可调电阻区、放大区、饱和区。第2题图五、综合题某超市举行一次促销活动,只要顾客拿着购物发票,就可以参加这项活动。......

2023-10-21

( )三、填空题1.某辆汽车刹车时能产生的最大加速度为10 m/s2,司机发现前方有危险时要经0.5 s才能作出反应马上制动。那么改用5 N的水平力拉物体,物体在原地面上运动的加速度是_________m/s2。......

2023-10-21

触电造成人体伤害的主要原因是电流对人体的伤害。其伤害程度与电流的大小、频率、触电时间、流过人体的路径、人体电阻和触电者本身的健康状况等因素有关。......

2023-10-21

电路在外加触发脉冲信号的作用下,能够产生具有一定宽度和幅度的矩形脉冲信号,但这只是一个暂时的稳定状态,经过一段时间又自动返回到稳态(原态)。图2-14-4 集成单稳态触发器74LS1233.单稳态触发器作用常用于对脉冲信号进行整形处理、延时控制,还用于电路的定时控制等。( )4.施密特触发器主要用于波形的变换、整形和幅度鉴别等。......

2023-10-21

( )3.在检测较大容量的电容器的质量时,当万用表的表棒分别与电容器的两端接触时,发现指针根本不偏转,这说明电容器内部已短路。( )三、填空题1.将容量分别为40μF和20μF,耐压值均为100 V的两只电容器串联使用时,最大安全工作电压为________V。电容器不带电,求接通开关S后流过R4的总电量。......

2023-10-21

相关推荐