【摘要】:因而TA和ATPT很容易成为瓶颈,从而影响虚拟化系统的整体效率。除此之外,在图13-2中,EP1和EP2分别隶属于Domain1和Domain2。在正常情况下,一个Domain并不能访问其他Domain的PCI设备。支持ATS机制的PCIe设备,内部含有ATC,ATC在PCIe设备中的位置如图13-8所示。与其他Cache类似,ATC还可以被Invalidate。当ATPT被更改时,处理器系统将发送Invalidate报文,同步在不同PCIe设备中的ATC。在PCIe总线中,只有与存储器相关的TLP支持AT字段。

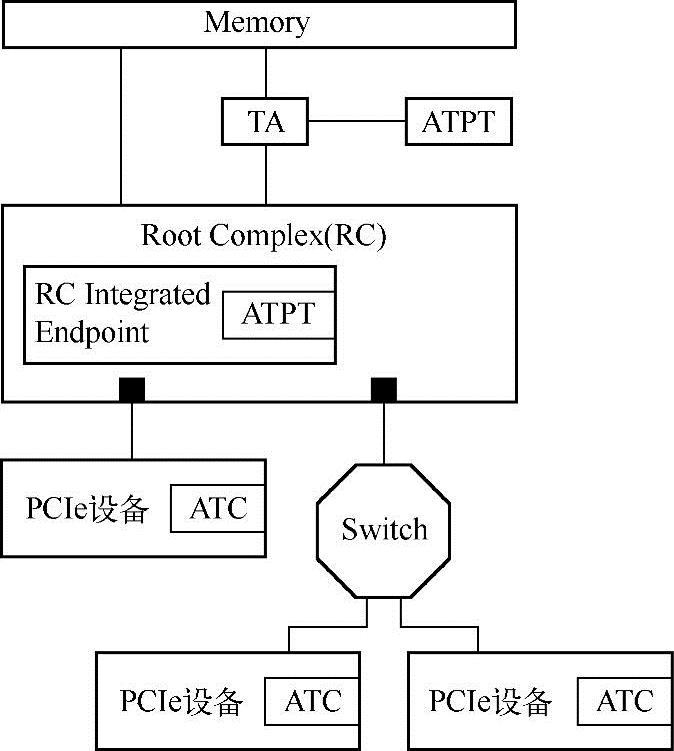

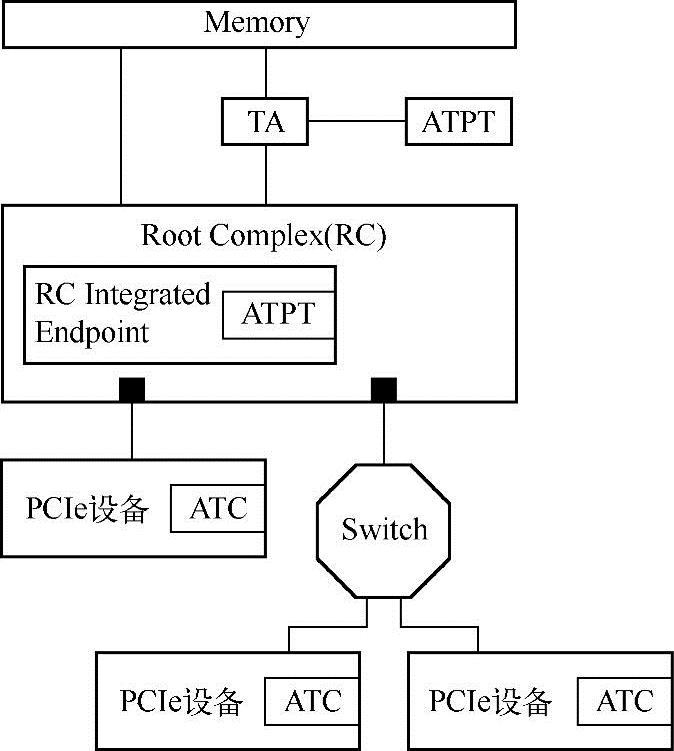

单纯使用IOMMU并不能充分发挥处理器系统的效率,从图13-2中可以发现,所有PCI设备在进行DMA操作时,都需要经过TA和ATPT进行地址翻译,然后才能访问主存储器。因而TA和ATPT很容易成为瓶颈,从而影响虚拟化系统的整体效率。

除此之外,在图13-2中,EP1和EP2分别隶属于Domain1和Domain2。在正常情况下,一个Domain并不能访问其他Domain的PCI设备。但是如果处理器系统中存在一个恶意的虚拟机,而且EP1隶属于该虚拟机(Domain1)。当EP1进行DMA写操作时,该虚拟机填写的DMA写地址可以与EP2的BAR地址空间重合,那么启动DMA写操作时,Domain1可以将数据传递到EP2,从而影响Domain2的正常运行。

解决这种异常的最合理的方法是,隶属于Domain1的PCI设备只能访问GPA1的空间,而仅使用IOMMU并不能解决该问题。解决该问题较为有效的方法是PCI设备进行数据传送的同时也进行地址转换,从而该PCI设备使用的地址是经过转换的HPA地址。此时再进行DMA写时,该数据将传递到与Domain1对应的HPA地址空间中,而不会将数据传送到EP2。从而这个恶意的虚拟机并不会影响其他正常工作的虚拟机。

PCIe总线使用ATS机制实现PCIe设备的地址转换。支持ATS机制的PCIe设备,内部含有ATC(Address Translation Cache),ATC在PCIe设备中的位置如图13-8所示。

在ATC中存放ATPT的部分内容,当PCIe设备使用地址路由方式发送TLP时,其地址首先通过ATC转换为HPA地址。如果PCIe设备使用的地址没有在ATC中命中时,PCIe设备将通过存储器读TLP从ATPT中获得相应的地址转换信息,更新ATC后,再发送TLP。与其他Cache类似,ATC还可以被Invalidate。当ATPT被更改时,处理器系统将发送Invalidate报文,同步在不同PCIe设备中的ATC。(https://www.chuimin.cn)

图13-8 ATC在PCIe设备中的位置

PCIe总线在TLP中设置了AT字段以支持ATS机制。在PCIe总线中,只有与存储器相关的TLP支持AT字段。值得注意的是,只有处理器系统支持IOMMU时,PCIe设备才可以使用ATS机制。

相关推荐