从图5 -18 可看出, 微控制器功能主要包括感应装定功能、转数定距功能、自毁功能。图5-19某型引信专用处理器程序流程图在计转数定距模式, 程序首先配置计转数定距功能需要的片上资源测到预定状态, 然后取出装定数据并以此作为起始圈数对弹丸旋转圈数进行减计数,当装定圈数减到零时给出发火指令。......

2023-06-15

AMD处理器的IOMMU技术与Intel的VT-d技术类似,其完成的主要功能也类似。AMD率先提出了IOMMU的概念,并发布了IOMMU的技术手册,但是Intel首先将这一技术在芯片中实现。由于AMD和Intel使用的x86体系结构略有不同,因此AMD的IOMMU技术在细节上与Intel的VT-d并不完全一致。

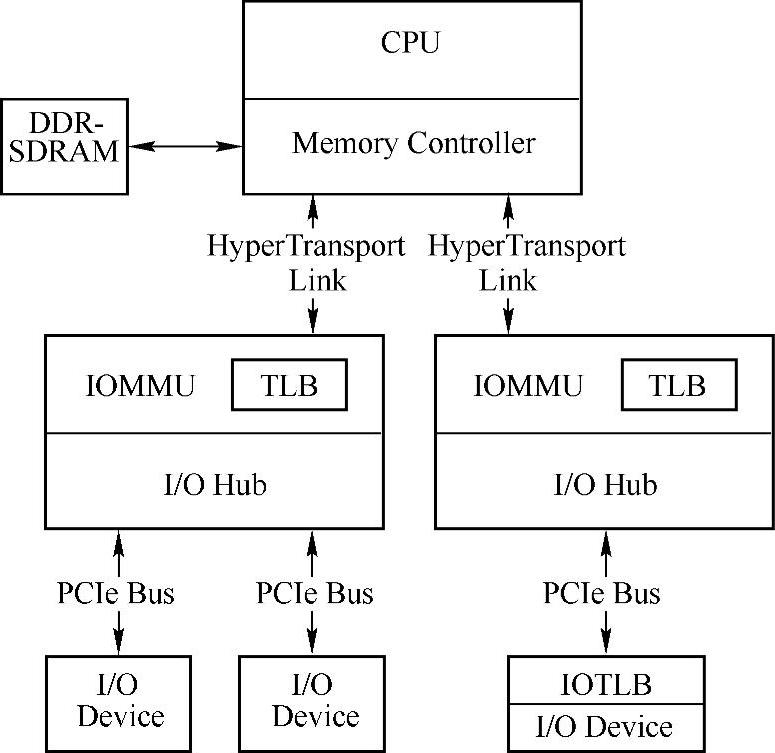

AMD处理器使用HT(Hyper Transport)总线连接I/O Hub,其中每一个I/O Hub都含有一个IOMMU,其结构如图13-5所示。

图13-5 AMD处理器的IOMMU结构

其中每一个IOMMU都使用一个Device Table。AMD处理器使用Device Table存放图13-3中的结构,Device Table最多由216个Entry组成,其中每个Entry的大小为256b,因此Device Table最大将占用2MB内存空间,与Intel使用的Root/Context Entry结构相比,AMD使用的这种方法容易造成内存的浪费。

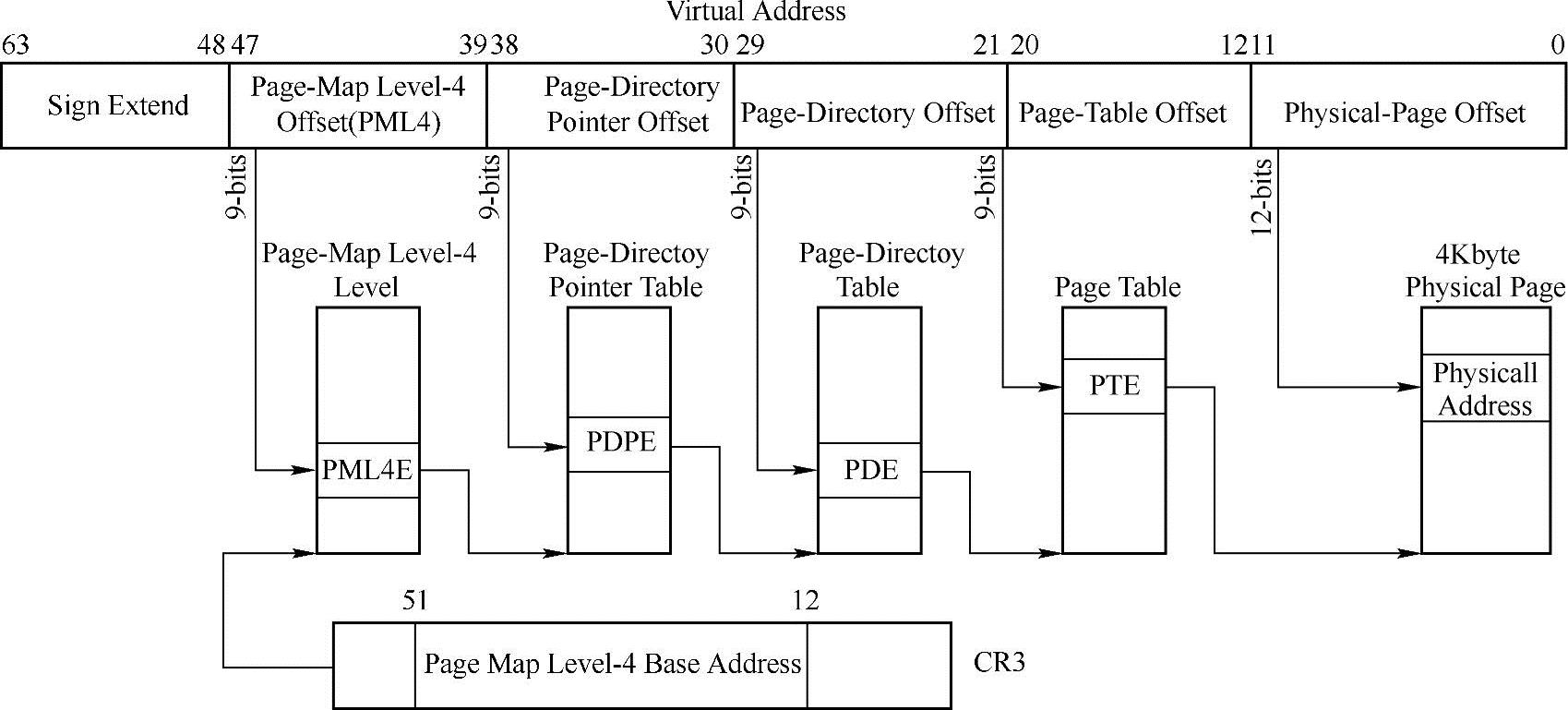

在I/O Hub中的设备[113]使用16位的DeviceID在Device Table查找该设备所对应的Entry,并使用这个Entry,根据I/O Page Table结构最终找到IO PTE表,并完成GPA到HPA的转换。在AMD处理器中,GPA到HPA的转换与图13-4中所示的方法有类似之处,但实现细节不同。IOMMU使用一个新型的页表结构完成GPA到HPA的转换,这个页表结构基于AMD64使用的虚拟地址到物理地址的页表结构,但是做出了一些改动。AMD64进行虚拟地址到物理地址的转换时使用4级页表结构,如图13-6所示。

与Intel处理器的结构类似,一个进程首先从CR3寄存器中获得页表的基地址指针寄存器“Page Map Level-4 Base Address”,之后通过4级索引最终获得4KB大小的物理页面,完成虚拟地址到物理地址的转换。AMD处理器也支持大页面方式,如果使用三级索引,可以获得2MB大小的物理页面;使用二级索引,可以获得1GB大小的页面。

IOMMU使用的I/O页表结构基于以上结构,但是做出了一定的改动。在IOMMU中,4级I/O页表指针可以直接指向2级I/O页表指针,从而越过第3级I/O页表,使用这种方法可以节省Page Table的空间。如图13-7所示。

图13-6 AMD64虚拟地址到物理地址的页表结构(www.chuimin.cn)

图13-7 IOMMU使用的GPA到HPA的转换机制

当设备进行DMA操作时,首先需要从相应的Device Table的Entry中获得“Level 4 Page Table Address”指针,并定位设备使用的I/O页表,最后使用多级页表结构,最终完成PCI总线地址到HPA地址的转换。Page Table的Entry由64位组成,其主要字段如下所示。

●第51~12位为Next Table Address/Page Address字段,该字段存放下一级页表或者物理页面的地址,该地址为系统物理地址,属于HPA空间。

●第11~9位为Next Level字段,表示下一级页表的级数,其中在Device Table中存放的级数一般为4,Level-N级页表中存放的Next Level字段为N-1~1。

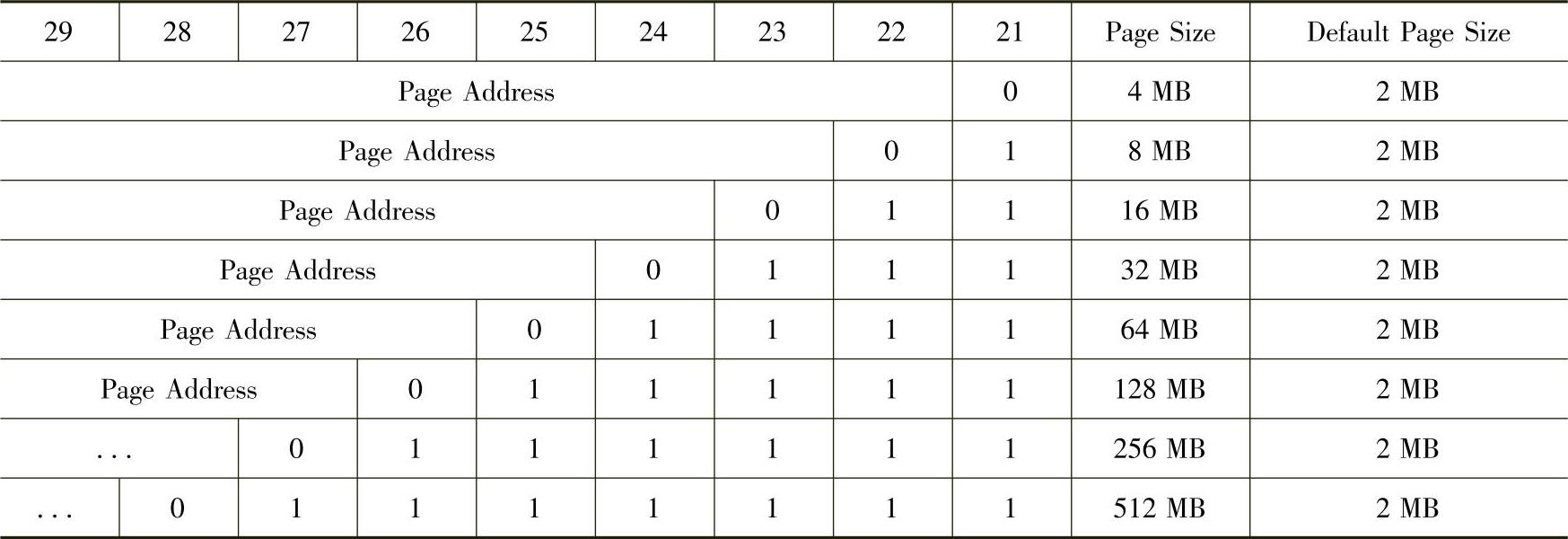

如图13-7所示,在第4级页表的Entry中的Next Level字段为2,表示第4级页表直接指向第2级页表,而忽略第3级页表。当该字段为0b000或者0b111时,表示下一级指针指向物理页面而不是页表。Next Level字段为0b000时,表示所指向的物理页面的大小是固定的,AMD64支持4KB、2MB、1GB、512GB和1TB(SP=4)大小固定页面;如果Next Level字段为0b111时,表示所指向的物理页面大小是浮动的。如果Level 2 Page Table的En-try中的Next Level字段为0b111,表示该Entry指向的物理页面大小浮动,其中物理页面大小和GPA的第29~21位相关,如表13-1所示。

表13-1 Next Level字段为0b111时的页表大小

AMD64处理器使用这种IO页表方式,可以方便地支持4KB、8KB、……、4GB大小的浮动物理页面。除了I/O页表外,IOMMU也设置了IOTLB以加快GPA到HPA地址的转换,这部分内容与IA处理器的实现方式类似,本章不对此继续进行描述。对IOMMU感兴趣的读者可以参考AMD I/O Virtualization Technology Specific ation。

有关PCI Express体系结构导读的文章

从图5 -18 可看出, 微控制器功能主要包括感应装定功能、转数定距功能、自毁功能。图5-19某型引信专用处理器程序流程图在计转数定距模式, 程序首先配置计转数定距功能需要的片上资源测到预定状态, 然后取出装定数据并以此作为起始圈数对弹丸旋转圈数进行减计数,当装定圈数减到零时给出发火指令。......

2023-06-15

DM 816X系列处理器框架如图2-9所示。Linux运行在该处理器上。④HDVICP2:负责视频编解码处理,根据芯片型号会有2、3个HDVICP2,1个HDVICP2有1080P@60fps的视频编码或解码能力。图2-10引自《DM 8148芯片数据手册》第5页框图。图2-10DM 814X系列处理器框图DM 814X有七种核心处理单元:①ARM Cortex-A8:负责系统控制和外围接口驱动。②PCIe 2.0:负责PCI总线连接,可以连接PCI设备也可以作为PCI扩展设备与X86处理器连接。除去以上还具有同DM816X相关部分相同模块。......

2023-11-22

数控机床的以太网可以实现远程数据传输、远程故障诊断及远程在线加工,目前主要功能是实现远程在线加工;且为了确保远程在线加工传输的高可靠性、高速度和高精度,采取建立在快速以太网板基础上的数据服务器功能进行数据传输。下面介绍数控机床基于Data Server功能的CNC与计算机的连接以及两种FTP传输软件的网络传输设定过程。......

2023-06-23

BIOS 是主板上的重要部件,具体作用有以下几点:1.处理器BIOS 中断服务BIOS 中断服务程序实质上就是计算机系统中硬件与软件之间的一个可编程接口,主要用于程序软件功能与微机硬件之间转接。......

2023-11-18

连接功能的实现主要涉及硬件技术,包括拓扑结构、控制方式、阻塞特性和故障防卫等方面的内容,下面分别进行简要说明。对T 接线器、S接线器、TST 网络及BANYAN 网络的详细介绍,可参阅第5.1.2节和第5.2.3节。这种系统不考虑阻塞率,但有时也可将等待时延超过门限值的呼叫视为被阻塞的呼叫。首先,在虚连接建立阶段遇到的阻塞与电路交......

2023-06-26

逆变器是电力电子技术的一个重要应用方面。而逆变器与整流器恰好相反,它的功能是将直流电转换为交流电。逆变器还具备有自动调压或手动调压功能,可改善光伏发电系统的供电质量。逆变器不仅具有直交流变换功能,还具有最大限度地发挥太阳能电池性能的功能和系统故障保护功能。太阳能发电系统用的逆变器的最大特点就是包括了最大功率点跟踪这一功能。......

2023-07-02

2.电流控制的工作原理MAX5069A采用其内部双通道消隐检测的电流信号进行电流控制,为防止电流信号进入PWM比较器,限流比较器全程监控CS脚的检测电流,并执行逐周期限流。......

2023-06-25

相关推荐