存储器读写请求TLP的格式如图6-8所示。在存储器读写和I/O读写请求的第3和第4个双字中,存放TLP的32或者64位地址。存储器、I/O和原子操作读写请求使用的TLP头较为类似。此时与这个存储器读请求TLP对应的读完成TLP中不包含有效数据。......

2023-10-20

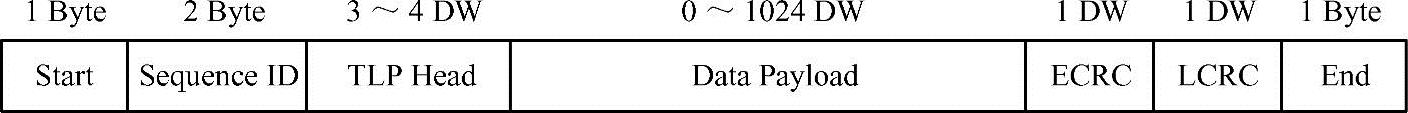

在PCIe总线中,TLP产生于事务层,并在通过PCIe总线的链路层与物理层时,加入若干前缀和后缀后,才能经由PCIe端口发送。PCIe总线定义了多种TLP,本章重点关心与存储器读写相关的TLP,包括存储器写TLP、存储器读请求TLP和存储器读完成TLP。这些TLP报文的通用格式如图12-10所示。

图12-10 PCIe总线TLP格式

由上图所示,一个PCIe设备发送TLP报文时,在经过数据链路层和物理层时,需要加上若干前缀和后缀。

(1)Sta rt和End前后缀由物理层添加,表示一个TLP的开始与结束,各由一个字节组成,用于物理层同步TLP发送与接收。

(2)Sequence ID和LCRC前后缀由数据链路层添加,存放TLP的识别号和数据链路层的CRC校验,分别由2B和1DW组成。

(3)TLP Head前缀描述TLP的属性,由3~4个DW组成。

(4)ECRC后缀存放TLP在事务层的CRC校验,该字段可选。

(5)而Data Payload是真正的有效负载,其长度在0~1024DW之间。由上文所述,TLP的有效负载长度由PCIe设备的Max_Payload_Size参数确定,该字段通过上下游链路进行协商后获得。目前在多数处理器系统中,PCIe设备使用的Max_Payload_Size参数为128B或者256B。

我们假设TLP使用3DW的报文头,而且不需要ECRC校验,根据图12-10,在一个TLP中,Data Payload所占的比例如公式12-11所示。

Payload_Ratio=Payload/(Payload+20) (12-11)

假设PCIe设备的Max_Payload_Size参数为256B时,根据以上公式可以得出该PCIe设备最大的Payload_Ratio=256/(256+20)≈92.8%。但是TLP在PCIe链路中进行传送时,远不能获得Payload_Ratio大小的链路带宽。TLP在传送过程中,需要通过PCIe总线的事务层、数据链路层和物理层,因此必须考虑这些协议所带来的开销。

1.事务层的开销

事务层的开销需要分存储器写和存储器读两种情况讨论。在PCIe总线中,存储器写请求TLP使用Posted总线事务,而存储器读请求TLP使用Split总线事务。在这两种情况之下,事务层的开销不同。

PCIe设备进行DMA写的过程较为简单,当PCIe设备将一个4KB大小的数据传送到存储器时,首先将4KB数据封装到多个存储器写请求TLP中,然后发向RC,其中每个TLP最大的Payload为Max_Payload_Size。

PCIe设备的Max_Payload_Size参数由PCIe链路协商确定,目前x86处理器系统RC的Max_Payload_Size为128B或者256B,所以与RC直接相连的PCIe设备,其Max_Payload_Size参数只能为128B或者256B。由公式12-11,可以计算出与Max_Payload_Size参数对应的Payload_Ratio,并由此推算存储器写TLP在事务层上的开销。

PCIe设备进行DMA读的过程略微复杂。首先PCIe设备向RC发送存储器读请求TLP,当RC收到这个存储器读请求TLP后,将从存储器中获得数据,然后组成一个或者多个存储器读完成TLP,并将其传送给PCIe设备。(www.chuimin.cn)

存储器读完成TLP能请求的数据大小为MRRS(Max_Read_Request_Size),该参数的大小为128B~4096B。如果PCIe设备进行DMA读的大小超过该参数时,将以该参数为界,向RC发出多个存储器读请求TLP。而RC可以使用一个存储器读完成报文传递所有数据;也可以以RCB为边界,使用多个存储器读完成报文传递所有数据。大多数RC使用后一种方式传递存储器读完成TLP,而且一次存储器读完成报文的大小也不超过RCB。本章以这种方式为例分析存储器读TLP在事务层中的开销。

假设存储器读请求TLP头的大小为3DW,而且报文头中不包含ECRC校验。PCIe设备进行DMA读的大小恰好为MRRS时,RC需要使用MRRS/RCB个存储器读完成报文传递数据。此时一次DMA读操作中Data Payload所占的比例如公式12-12[104]所示。

Payload_Ratio=MRRS/(MRRS+3×4+3×4×MRRS/RCB) (12-12)

当MRRS为512B,而RCB为64B时,Payload_Ratio=512/(512+12+12*8)≈82.6%。由以上分析可以发现PCIe设备进行DMA读在事务层上的开销大于DMA写在事务层上的开销,这也是PCIe设备DMA写的速度略高于DMA读的主要原因。

除了事务层的开销之外,DMA读操作的数据传送路径也长于DMA写,因而访问延时大于DMA写操作的访问延时,这也为DMA读逻辑的设计带来了不小的麻烦。从第12.2.2节中,也可以发现DMA读逻辑的设计远比DMA写逻辑的设计复杂。

2.链路层的开销

由图12-10所示,链路层向TLP添加Sequence ID和LCRC前后缀,这些开销已经在上文中计算,本小节不再重复计算这些开销。本小节所关心的链路层开销由两部分组成,一个是ACK/NAK协议的开销,另一个是流量控制所带来的开销。如第7.2节所示,发送方在发送TLP时,首先将这些TLP放入到Replay Buffer中,直到收到接收方的ACK报文后,才能确认该TLP已经正确地被接收方接收;如果收到接收方NAK报文,则表示部分TLP没有被正确接收,需要重新发送这些TLP。这些ACK/NAK报文将占用部分链路带宽。

在PCIe设备的实现过程中,设计者可以调整TLP接收个数的阈值,这个阈值的定义为接收端收到多少TLP后,给发送端提供一次ACK/NAK DLLP。该阈值决定了数据接收端发送ACK/NAK报文的间隔。

该阈值越大,则发送端的Replay Buffer也将随之增大,否则发送端无法将数据及时填入Replay Buffer,从而阻塞了发送流水,并影响PCIe总线的传送效率;如果该阈值越小,则接收端需要发送较多的ACK/NAK报文给接收端,也会影响PCIe总线的效率。因此接收端需要合理地设置ACK/NAK的阈值,以最大程度地利用PCIe总线的带宽。

在链路层的设计中,需要选择合适的Replay Buffer的大小。如果Replay Buffer过小,事务层无法及时地将TLP发送到Replay Buffer,从而造成TLP发送流水线的中断。而保存在Replay Buffer中的报文需要得到对端设备的确认报文后,才能释放。

因此可以发现Replay Buffer的大小,只需要保证事务层发送TLP时,有足够的缓冲即可。Replay Buffer的大小与PCIe链路的延时相关。在实现中,Replay Buffer不能过大,否则将使用较多的芯片资源。

在链路层中,除了ACK/NAK报文的开销外,流量控制报文也需要占用PCIe总线的链路开销。PCIe总线使用Credit-Based流量控制策略,发送端需要保证接收端有足够的缓冲之后才能发送报文,而且接收端需要按照某种策略及时使用FC Update报文,向发送端通知剩余的数据缓冲。因此流量控制也需要占用一些PCIe总线的带宽。在PCIe总线中,流量控制是基于“端到端”的,而且PCIe总线并没有规定PCIe设备使用的流量算法,因此流量控制对PCIe总线带宽的影响与设备相关,并没有一个统一的公式。

3.物理层的开销

在PCIe V2.1总线规范中,TLP在物理层中还需要进行8/10b转换,这个转换将极大地降低PCIe总线的实际链路带宽,而且在PCIe总线中,这种带宽的浪费是无法避免的。在PCIe V3.0规范中,这个8/10b转换被升级为128/130转换。128/130转换将极大节约PCIe链路带宽的浪费。但是无论如何,TLP在发送过程中,仍然会因为这种转换浪费PCIe链路的一些带宽。

除了8/10b转换之外,物理层为了解决接收时钟与逻辑时钟间的漂移所带来的问题,每一个Lane需要在发送1180~1538个字符后,发送一个SKIP序列进行时钟补偿。这种定时的时钟补偿序列也将浪费PCIe链路的部分带宽。

有关PCI Express体系结构导读的文章

存储器读写请求TLP的格式如图6-8所示。在存储器读写和I/O读写请求的第3和第4个双字中,存放TLP的32或者64位地址。存储器、I/O和原子操作读写请求使用的TLP头较为类似。此时与这个存储器读请求TLP对应的读完成TLP中不包含有效数据。......

2023-10-20

当TLP的TH位为1时,表示在当前TLP中包含Processing Hint字段,PH字段由PCIe V2.1总线规范引入。Processing Hint字段的产生与智能设备的大量涌现密切相关。有些智能设备,如在显卡中使用的GPU和GP-GPU的处理能力甚至超过多数通用处理器。该TLP Prefix也被称为TPH TLP Prefix,其格式如图6-15所示。TPH Requester Capability结构使用ST Mode Sele ct字段定义了ST字段的三种使用模式。......

2023-10-20

VC不同的TLP间没有序的要求,在PCIe总线中,“序”是指VC相同的TLP之间的传送顺序,其关系如表11-5所示。表11-5 PCIe总线的序各个表项的含义如下。如在第11.1.1节描述的生产/消费者模型中,生产者首先将数据写入数据缓冲,然后将Flag位置1。B2 b对应TLP的IDO位为1的情况。......

2023-10-20

而PCI总线的突发传送仍然存在缺陷。为此PCI-X总线使用基于数据块的突发传送方式,发送端以ADB为单位,将数据发送给接收端,一次突发读写为一个以上的ADB。采用这种方式,接收端可以事先预知是否有足够的接收缓冲,接收来自发送端的数据,从而可以及时断连当前总线周期,以节约PCI-X总线的带宽。因此在PC领域和嵌入式领域很少有基于PCI-X总线的设备,PCI-X设备仅在一些高端服务器上出现。因此本节不对PCI-X总线做进一步描述。......

2023-10-20

为此PCI桥需要对Non-Posted总线事务进行优化处理,并使用Delayed总线事务处理这些Non-Posted总线事务,PCI总线规定只有Non-Posted总线事务可以使用Delayed总线事务。PCI总线的Delay总线事务由Delay读写请求和Delay读写完成总线事务组成,当Delay读写请求到达目的地后,将被转换为Delay读写完成总线事务。为了进一步提高Non-Posted总线事务的执行效率,PCI-X总线将PCI总线使用的Delayed总线事务,升级为Split总线事务。......

2023-10-20

此时PCI桥首先Retry当前Non-Posted总线事务,并将其转换为Delayed总线事务。使用Delayed总线请求事务进行数据传送时,需要遵循以下规则。而这些重试操作极大浪费了PCI总线的带宽,这也是Delayed总线事务的缺点。此时这个Delayed总线完成事务除了在以下两种情况之外,不能被随便丢弃。PCI桥在处理Delayed总线事务时,必须能够接收来自这个桥同一侧的Posted存储器写请求。因为Delayed读总线事务A有可能被设备使用重试周期结束。......

2023-10-20

下面以图3-2所示的处理器系统为例,说明处理器向PCI设备11进行存储器写的数据传送过程。PCI设备11在PCI总线域的地址范围是0x7300-0000~0x73FF-FFFF。存储器域将0xF300-0008这个地址发向HOST主桥,0xF000-0000~0xF7FF-FFFF这段地址已经由HOST主桥映射到PCI总线域地址空间,所以HOST主桥认为这是一个对PCI设备的访问。PCI总线0的PCI桥1发现0x7300-0008在自己管理的地址范围内,于是接管这个存储器写请求,并通过总线仲裁逻辑获得PCI总线1的使用权,并将这个请求转发到PCI总线1上。......

2023-10-20

第4.1.4节简单介绍了在PCIe总线中,如何使用Switch进行链路扩展,本节主要介绍Switch[7]的内部结构。值得注意的是,在Switch内部还具有一条虚拟的PCI总线,用于连接各个虚拟PCI桥,系统软件在初始化Switch时,需要为这条虚拟PCI总线编号。Switch的组成结构如图4-10所示。在PCIe体系结构中,Switch处于核心地位。深入理解PCI桥是理解Switch软件组成结构的基础。目前PCIe总线提出了MRA-Switch的概念,这种Switch与传统Switch有较大的区别,有关这部分内容详见第13.3节。......

2023-10-20

相关推荐