【摘要】:表11-4 PCI桥使用的数据访问顺序1.Posted存储器写通过PCI桥时需要按序完成Posted存储器写通过PCI桥时需要遵循“先进先出”的原则,否则将会引发数据完整性问题。

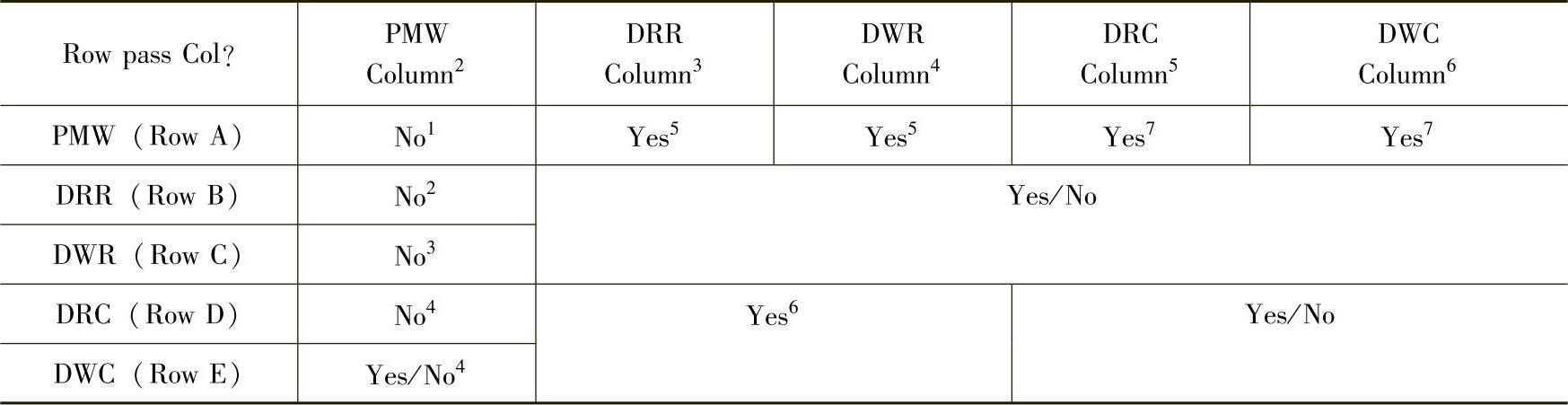

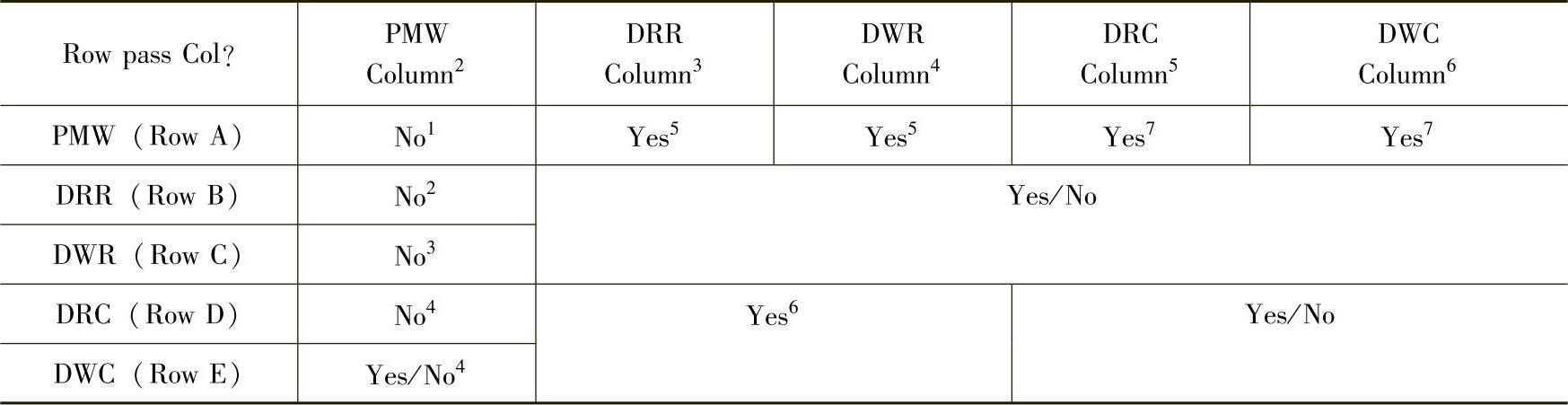

在PCI桥中,设置了许多缓冲暂存各类总线事务,包括Posted存储器写(PMW),De-layed读请求(DRR),Delayed读完成(DRC),Delayed写请求[76](DWR)和Delayed写完成(DWC)。这些不同种类的总线事务在同一方向穿越PCI桥时,无论是从上游总线到下游总线还是从下游总线到上游总线穿越PCI桥时,都必须遵循一定的顺序,以满足生产/消费者模型在PCI总线上的正确运行。有关PCI桥的序如表11-4所示。在该表中出现的“Yes”、“No”和“Yes/No”的定义如下所示。

●“Yes/No”表示Row和Column之间的总线事务没有序的关系,如DWC(Row E)总线事务和PMW(Colunm 2)总线事务在通过PCI桥时没有先后顺序。

●“Yes”表示Row中的总线事务先于Column中的总线事务通过PCI桥。比如PMW总线事务可以超越DRR和DWR总线事务。

●“No”表示Row中的总线事务后于Column中的总线事务通过PCI桥。如PMW总线事务不能超越之前的PMW总线事务。

●表中的“Yes”和“No”的上标对应一个序的规则,例如No1中的上标1对应规则1。这些规则将在下文陆续介绍。

表11-4 PCI桥使用的数据访问顺序

1.Posted存储器写通过PCI桥时需要按序完成

Posted存储器写通过PCI桥时需要遵循“先进先出”的原则,否则将会引发数据完整性问题。这个要求对满足生产/消费者模型的正常运行至关重要。

对于生产者,置Flag位为1和将数据写入数据缓冲都使用Posted存储器写总线事务。如果Flag位和数据缓冲在同一条PCI总线上时,Posted存储器写不按序到达,可能导致Flag位被生产者置1,而数据缓冲并没有收到数据,从而在消费者使用数据缓冲中的数据时,可能会得到无效数据。

2.DRR不能超越PMW

PCI桥首先将DRR保存在缓冲区中,之后PCI桥将缓存在该桥中的所有PMW都刷新出去后,才能执行这个DRR,即“先写后读”,否则读入的数据有可能不是最新的。系统软件可以使用这一功能实现“读刷新”操作。PCIe总线还支持读“0字节”操作,其主要目的就是完成这种“读刷新”操作。

3.DWR不能超越PMW

DWR首先在PCI桥中锁存,之后PCI桥将缓存的所有PMW发送出去后,才能执行这个DWR。在生产/消费者模型中,生产者除了可以使用PMW总线事务设置Flag位之外,也可以使用DWR总线事务设置Flag状态位(Flag状态位可能存放在I/O地址空间中,而且假设在图11-1中,Flag位和数据缓冲都在PCI总线0上)。

此时DWR不能超越PMW,因为生产者必须将所有数据都写入数据缓冲后,才能设置Flag状态位。如果DWR可以超越PMW,则会出现生产者没有将数据完全写入到数据缓冲中,而Flag位已经置1,从而可能引发数据完整性问题。规则2、3与规则5直接相关,DRR、DWR和不能超越PMW,也意味着PMW需要超越DRR和DWR。

4.DRC不能超越PMW

PCI总线使用DRR总线事务处理存储器和I/O读请求,而该总线事务在获得所读取的数据和完成状态后,将被转化为DRC总线事务,并在主设备重新发起读操作时,将数据传递给主设备。DRC要求数据在穿越PCI桥传递给主设备之前,PCI桥将缓存的PMW总线事务刷新出去。

以图11-1为例,如果消费者使用DRC总线事务获得Flag位,当Flag位为1时,必须要求生产者将数据全部写入数据缓冲中。如果DRC可以超越PMW,则可能出现消费者通过DRC获得Flag位,而且Flag位为1时,生产者提供的数据仍在PCI桥中的情况。因为这些数据需要通过PCI桥才能达到缓冲,而Flag位与生产者在同一条总线上,可以立即生效。

当消费者发现Flag位为1时,会立即读取数据缓冲,在图11-1中,如果这个DRC请求能够超越PMW,那么PCI桥首先将Flag位已经为1的消息传递给消费者,之后消费者开始从缓冲中读取数据,而这时生产者使用PMW方式写入缓冲的数据还可能在PCI桥中,从而造成数据完整性的问题。

在PCI总线中,解决该问题的方法是DRC不能超越PMW,这样消费者在收到Flag位为1的信息之前,在PCI桥中的PMW一定被DRC刷新到PCI总线0中,从而不会引发数据完整性问题。规则4与规则7之间相关,DRC不能超越PMW,也意味着PMW需要超越DRC。(www.chuimin.cn)

在PCI总线中,DWC与PMW之间没有序的要求。因为DWC中并不包含有效数据,仅是通知发送DWR的设备,该写请求已经结束。DWC不在生产/消费者模型中出现。

5.PMW可以超越DRR和DWR

PCI总线为了避免死锁,可以使刚进入PCI桥的PMW总线事务,超越已经在PCI桥中暂存的DRR和DWR总线事务,即PMW总线事务可以提前执行。如果PMW不能超越DRR和DWR,则会产生死锁。实际上因为规则2和3的原因,规则5的引入是顺利成章的。

值得注意的是该规则的引入还解决了在PCI总线中使用的不同版本的PCI桥的问题,本小节对这种情况不做深入讨论。

6.Delayed读写完成可以超越Delayed读写请求

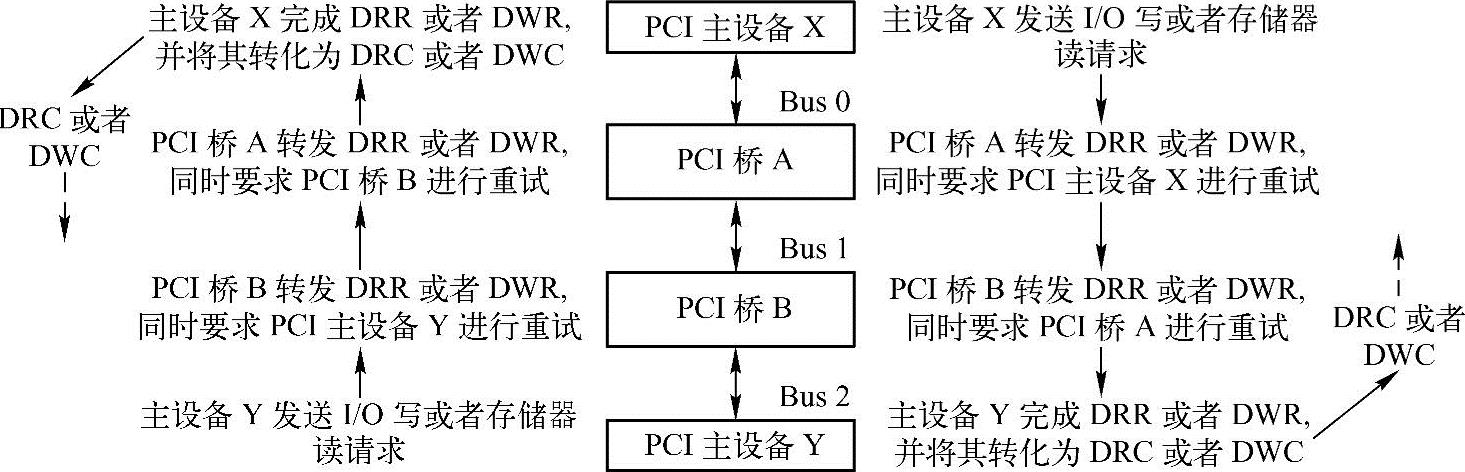

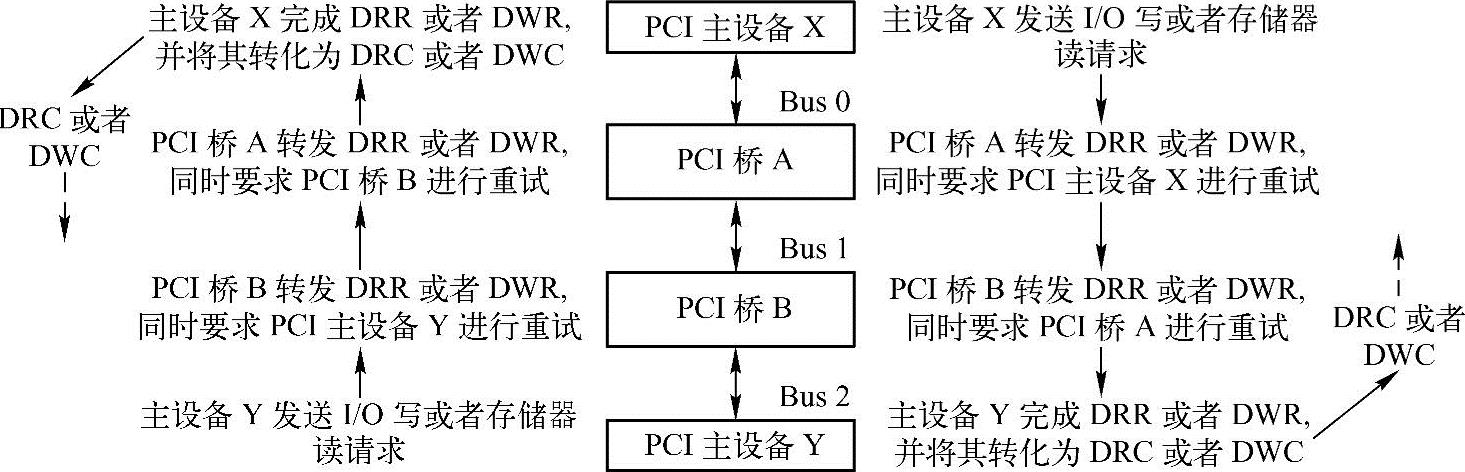

如果DWC和DRC总线事务到达PCI主设备时,这个主设备正在等待DWR和DRR总线事务完成,DWC和DRC必须可以优先到达PCI主设备,否则将引发死锁,下文以图11-4所示的实例说明这种死锁。

我们考虑PCI主设备X和Y通过PCI桥A和B进行数据读写,其步骤如下。

(1)PCI主设备X和Y同时发起一个Non-Posted读写请求。

(2)PCI桥A和B将这个Non-Posted总线读写请求转换为Delayed读写请求,并暂存在桥内缓冲中,分别为DRR-X和DRR-Y,同时使用重试周期结束PCI主设备X和Y的读写请求。之后PCI主设备X和Y将定时重发这个Non-Posted总线读写请求,直到完成本次总线读写请求。

(3)PCI桥A和B依次获得PCI总线1的使用权,并将DRR-X和DRR-Y请求发向对方。PCI桥B和A将来自对方的Delayed读写请求锁存在桥内缓冲中,并发起重试周期结束来自PCI桥A和B的Delayed读写请求。

(4)PCI桥A和B将定时重发这个Delayed总线读写请求,直到获得Delayed总线读写完成信息。

(5)PCI桥A和B将分别获得PCI总线0和2的使用权,将DRR-Y和DRR-X请求发送到最终PCI设备。假设PCI桥A获得PCI总线0的使用权,并完成了PCI主设备Y发起的DRR-Y请求,此时PCI桥A将从PCI主设备X中得到Delayed读写完成信息,并将DRR-Y请求转换为DRC-Y请求,并将其锁存在PCI桥A的缓存中。等待PCI桥B对PCI桥A进行重试。

(6)如果此时PCI桥A在没有完成DRR-X请求(该请求是发向PCI主设备Y)时,不能接收DRC-Y请求将引发死锁。因为DRC-X请求也会因为相同的原因不会被PCI B桥接收,从而PCI桥A无法完成DRR-X请求。

图11-4 DWC/DRC不能超越DRR/DWR而造成死锁

如果Delayed总线完成可以超越Delayed请求时,将有效地避免这类死锁。因为Delayed总线完成是发生在Delayed总线请求之后的事件,这两个请求有因果关系,希望读者认真体会规则6。

7.PMW总线事务可以超越DRC/DWC总线事务

PCI总线规定PMW总线必须可以超越之前已经在PCI桥中暂存的DRC/DWC总线事务,以避免死锁。引入该规则的主要原因是在PCI总线层次结构中可能存在不同版本的PCI桥,它们的缓冲管理策略并不一致,从而有可能造成死锁。本节对这种情况不做进一步描述。

相关推荐