下面以存储器读为例,说明PCI-X设备如何使用Split总线事务。这些PCI-X桥使用Split Response周期结束当前总线事务,释放上游PCI总线。之后继续转发这个存储器读请求,直到Completer认领这个存储器读请求总线事务。Completer准备好数据后,将重新申请总线,并使用存储器读完成总线事务主动地将数据传送给Requester。PCI-X总线提出的Split总线事务被PCIe总线继承。......

2023-10-20

与MPC8572处理器处理MSI中断请求不同,x86处理器使用FSB的Interrupt Message总线事务,处理PCIe设备的MSI/MSI-X中断请求。由上文所示,MPC8572处理器处理MSI中断请求时,首先由MPIC中断控制器截获这个MSI中断请求,之后由MPIC中断控制器向CPU提交中断请求,而CPU通过中断响应周期从MPIC中断控制器的ACK寄存器中获得中断向量。

采用这种方式的主要问题是,当一个处理器中存在多个CPU时,这些CPU都需要通过中断响应周期从MPIC中断控制器的ACK寄存器中获得中断向量。在一个中断较为密集的应用中,ACK寄存器很可能会成为系统瓶颈。而采用Interrupt Message总线事务可以有效地避免这种系统瓶颈,因为使用这种方式中断信息和中断向量将同时到达指定的CPU,而不需要使用中断响应周期获得中断向量。

x86处理器也具有通过中断控制器提交MSI/MSI-X中断请求的方法,在I/O APIC具有一个“The IRQ Pin Assertion Register”寄存器,该寄存器地址为0xFEC00020[74],其第4~0位存放IRQ Number。系统软件可以将PCIe设备的Message Address寄存器设置为0xFEC00020,将Meaasge Data寄存器设置为相应的IRQ Number。

当PCIe设备需要提交MSI中断请求时,将向PCI总线域的0xFEC00020地址写入Mes-sage Data寄存器中的数据。此时这个存储器写请求将数据写入I/O APIC的The IRQ Pin As-sertion Register中,并由I/O APIC将这个MSI中断请求最终发向Local APIC,之后再由Local APIC通过INTR#信号向CPU提交中断请求。

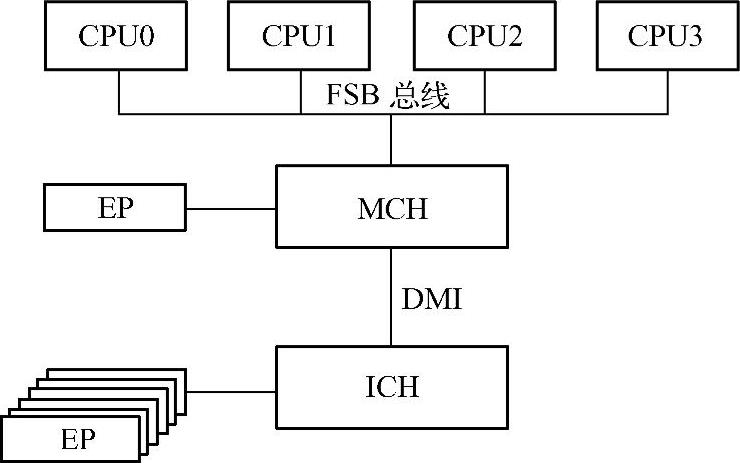

上述步骤与MPC8572处理器传递MSI中断的方法类似。在x86处理器中,这种方式基本上已被弃用。下面以图10-9为例,说明x86处理器如何使用FSB总线的Interrupt Message总线事务,向CPU提交MSI/MSI-X中断请求。

(www.chuimin.cn)

(www.chuimin.cn)

图10-9 使用Interrupt Message总线事务传递MSI中断请求

PCIe设备在发送MSI/MSI-X中断请求之前,系统软件需要合理设置PCIe设备MSI/MSI-X Capability寄存器,使Message Address寄存器的值为0xFEExx00y[75],同时合理地设置Mes-sage Data寄存器Vector字段。

PCIe设备提交MSI/MSI-X中断请求时,需要向0xFEExx00y地址写Message Data寄存器中包含的数据,并以存储器写TLP的形式发送到RC。如果ICH收到这个存储器写TLP时,将通过DMI接口将这个TLP提交到MCH。MCH收到这个TLP后,发现这个TLP的目的地址在FSB Interrupts存储器空间中,则将PCIe总线的存储器写请求转换为Interrupt Message总线事务,并在FSB总线上广播。

FSB总线上的CPU,根据APIC ID信息,选择是否接收这个Interrupt Message总线事务,并进入中断状态,之后该CPU将直接从这个总线事务中获得中断向量号,执行相应的中断服务例程,而不需要从APIC中断控制器获得中断向量。与PowerPC处理器的MPIC中断控制器相比,这种方法更具优势。

有关PCI Express体系结构导读的文章

下面以存储器读为例,说明PCI-X设备如何使用Split总线事务。这些PCI-X桥使用Split Response周期结束当前总线事务,释放上游PCI总线。之后继续转发这个存储器读请求,直到Completer认领这个存储器读请求总线事务。Completer准备好数据后,将重新申请总线,并使用存储器读完成总线事务主动地将数据传送给Requester。PCI-X总线提出的Split总线事务被PCIe总线继承。......

2023-10-20

PCI桥将下游传递到上游的LOCK总线事务转换为普通的总线事务,即去掉这个LOCK标志。如果该LOCK总线事务是Non-Posted总线事务,此时PCI桥并不能立即完成这个LOCK总线事务,因为PCI桥还需要将“Non-Posted总线请求”对应的总线完成信息传递给发起者之后,LOCK总线事务才能最终完成。该PCI桥不会使用Delayed总线事务接收其他Non-Posted总线事务,也不会暂存这些总线事务。丢弃所有暂存在PCI桥中的De-layed总线事务;允许LOCK总线事务超越任何读写请求。......

2023-10-20

事务层是PCIe总线层次结构的最高层,该层次将接收PCIe设备核心层的数据请求,并将其转换为PCIe总线事务,PCIe总线使用的这些总线事务在TLP头中定义。PCIe的事务层还支持流量控制和虚通路管理等一系列特性,而PCI总线并不支持这些新的特性。在PCIe总线中,不同的总线事务采用的路由方式不相同。PCIe总线使用的数据报文首先在事务层中形成,这个数据报文也称为事务层数据报文,即TLP。......

2023-10-20

PCI总线规范定义了一系列与Cache相关的总线事务,以提高PCI设备与主存储器进行数据交换的效率,即DMA读写的效率。PCI设备与主存储器进行的Cache共享一致性增加了HOST主桥的设计复杂度。在高性能处理器中Cache状态机的转换模型十分复杂。因为Cache一致性操作不仅与HOST主桥的设计相关,而且主要与处理器和Cache Memory系统设计密切相关。因为x86处理器重点优化的是PCIe设备,目前x86处理器使用的IOAT技术,显著提高了PCIe设备与主存储器进行数据通信的效率。......

2023-10-20

表11-4 PCI桥使用的数据访问顺序1.Posted存储器写通过PCI桥时需要按序完成Posted存储器写通过PCI桥时需要遵循“先进先出”的原则,否则将会引发数据完整性问题。......

2023-10-20

此时PCI桥首先Retry当前Non-Posted总线事务,并将其转换为Delayed总线事务。使用Delayed总线请求事务进行数据传送时,需要遵循以下规则。而这些重试操作极大浪费了PCI总线的带宽,这也是Delayed总线事务的缺点。此时这个Delayed总线完成事务除了在以下两种情况之外,不能被随便丢弃。PCI桥在处理Delayed总线事务时,必须能够接收来自这个桥同一侧的Posted存储器写请求。因为Delayed读总线事务A有可能被设备使用重试周期结束。......

2023-10-20

PCI总线是由Intel公司提出的。PCI总线不是由ANSI通过的标准,但由于它是由厂家自发制定执行的标准,具有众多的优点,拥护者,执行者众多,成了事实上的标准。PCI总线共有100个引脚,如果只作为目标设备,至少需要47条,如作为主设备则需要49条。本设计使用位命令字,其定义如下:3.PCI总线基本协议PCI上的基本总线传输机制是突发成组传输。......

2023-11-22

在SQL Server 2012中,通过使用事务和锁机制,可以解决数据库的并发性问题。在SQL Server 2012中,事务要求处理时必须满足ACⅠD原则,即原子性、一致性、隔离性(Ⅰ)和持久性。图7—1事务的工作原理事务开始之后,事务所有的操作都陆续写到事务日志中。图7—2事务恢复和检查点......

2023-11-24

相关推荐