【摘要】:在PowerPC处理器系统中,MSI机制的实现过程是PCIe设备向MSIIR寄存器写入指定的数据。MPIC中断控制器发现该寄存器被写入后,将向处理器提交中断请求。处理器收到这个中断请求后,将通过读取MPIC中断控制器的ACK寄存器确定中断向量,并依此确定中断源。表10-3 MSIIR寄存器PCIe设备通过MSI机制,向此寄存器写入数据时,MSIR0~7寄存器的相应位SH0~31将有一位置1。

PowerPC处理器设置了一系列寄存器,处理来自PCIe设备的MSI报文,其中最重要的寄存器是MSIIR寄存器。在PowerPC处理器系统中,PCIe设备Message Address寄存器中存放的值都为MSIIR寄存器的物理地址,而Message Data寄存器中存放的数据也与MSIIR寄存器相关。

在PowerPC处理器系统中,MSI机制的实现过程是PCIe设备向MSIIR寄存器写入指定的数据。MPIC中断控制器发现该寄存器被写入后,将向处理器提交中断请求。处理器收到这个中断请求后,将通过读取MPIC中断控制器的ACK寄存器确定中断向量,并依此确定中断源。为此PowerPC处理器还设置了其他寄存器实现MSI中断机制。

1.MSIIR寄存器

在PowerPC处理器中,MSIIR(Shared Message Signaled Interrupt Index Register)寄存器是实现MSI机制的重要寄存器。

当PCIe设备对MSIIR寄存器进行写操作时,MPC8572处理器将使能MSIR0-MSIR7寄存器的相应位,从而向MPIC中断控制器提交中断请求,而中断控制器将转发这个中断请求,由处理器进一步处理。该寄存器各字段的详细描述如表10-3所示。

表10-3 MSIIR寄存器

PCIe设备通过MSI机制,向此寄存器写入数据时,MSIR0~7寄存器的相应位SH0~31将有一位置1。例如PCIe设备向MSIIR寄存器写入0xFF00000时,MSIR7寄存器的SH31位将置1(SRS字段为0b111用来选择MSIR7,而IBS字段为0b11111用来选择SH31)。

2.MSIR寄存器组

MSIR(Shared Message Signaled Interrupt Registers)寄存器组共由8个寄存器组成,分别为MSIR0~MSIR7。其中每一个MSIRx寄存器中有32个有效位,分别为SH0~31。当PCIe设备对MSIIR寄存器进行写操作时,某一个MSIIRx寄存器的某个SH位将被置为有效。系统软件通过读取该寄存器获得中断源,该寄存器读清除,对此寄存器进行写操作没有意义。

该寄存器组的大小决定了一个PowerPC处理器支持的MSI中断请求的个数。在MPC8572处理器中,有8个MSIRx寄存器,每个寄存器由32个有效位组成,因此MPC8572处理器最多能够处理256个MSI中断请求。该寄存器的结构如图10-6所示。

图10-6 MSIRx寄存器的结构

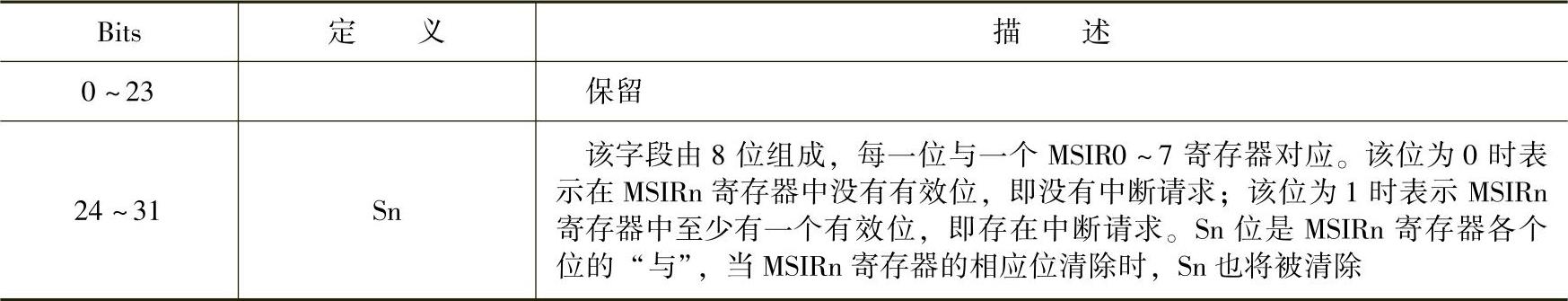

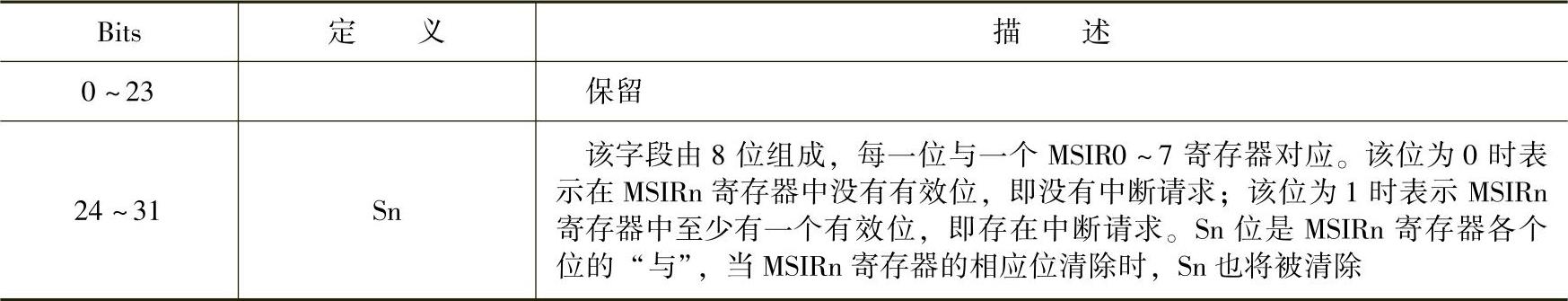

3.MSISR寄存器

MSISR寄存器(Shared Message Signaled Interrupt Status Register)共由8个有效位组成,每一位对应一个MSIR寄存器。MPC8572处理器设置该寄存器的主要目的是方便系统软件定位究竟是哪个MSIR寄存器中存在有效的中断请求。首先系统软件通过MSISR寄存器判断是哪个MSIRx寄存器存在有效请求,之后读取相应的MSIRx寄存器,该寄存器各字段的详细描述如表10-4所示。

表10-4 MSISR寄存器(www.chuimin.cn)

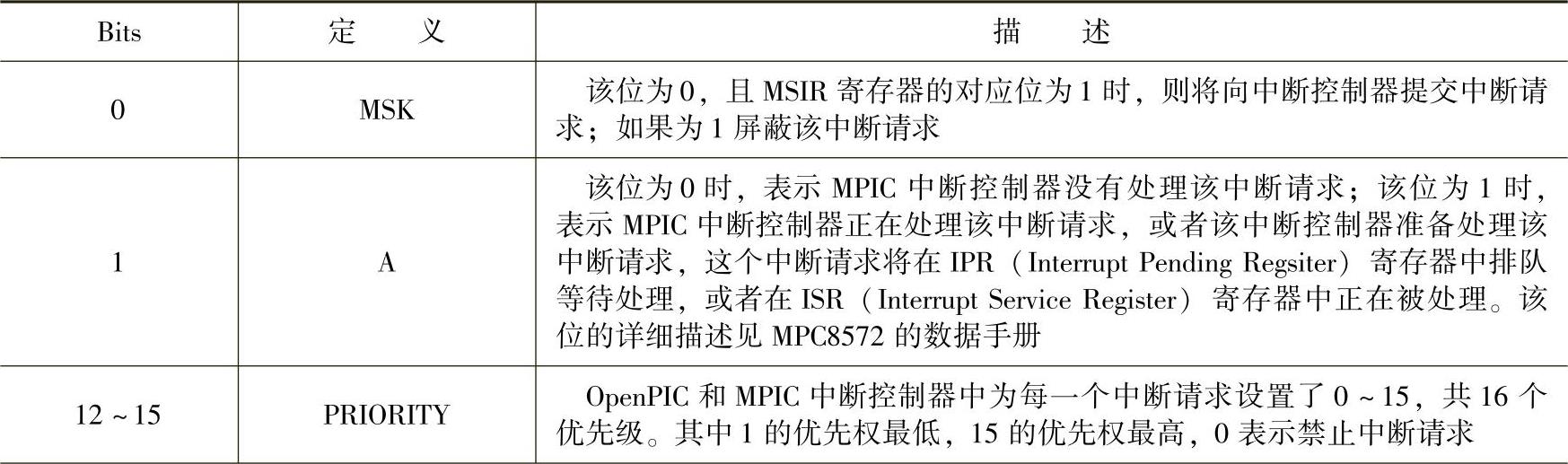

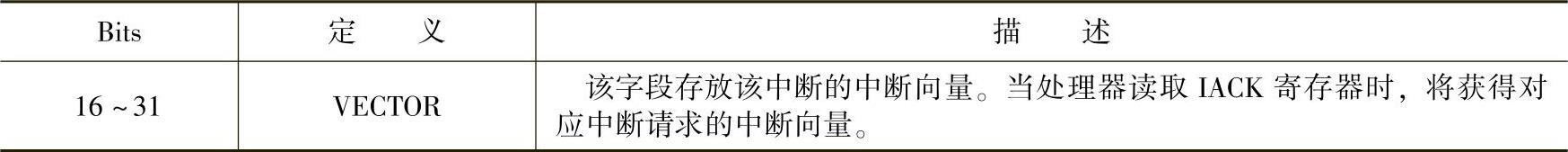

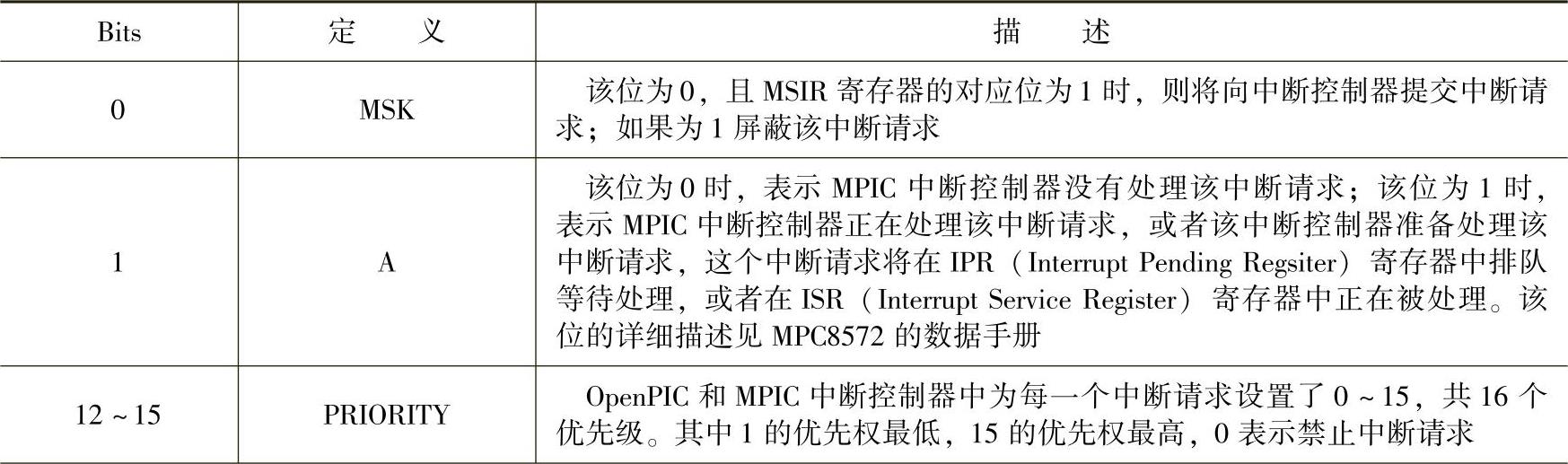

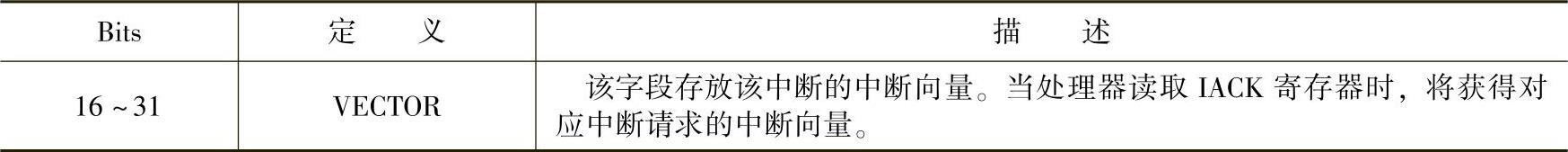

4.MSIVPR寄存器组

MSIVPR(Shared Message Signaled Interrupt Vector/Priority Register)寄存器组由8个寄存器组成,分别为MSIVPR0~7寄存器。该组寄存器设置对应中断请求的优先级别和中断向量。其中每个MSIVPR寄存器对应一个MSIR寄存器,MSIVPR寄存器各字段的详细解释如表10-5所示。

表10-5 MSIVPR寄存器

(续)

通过该组寄存器可以发现,在MPC8572处理器系统中,PCIe设备最多可以使用8个中断向量,并可以共享这些中断向量。

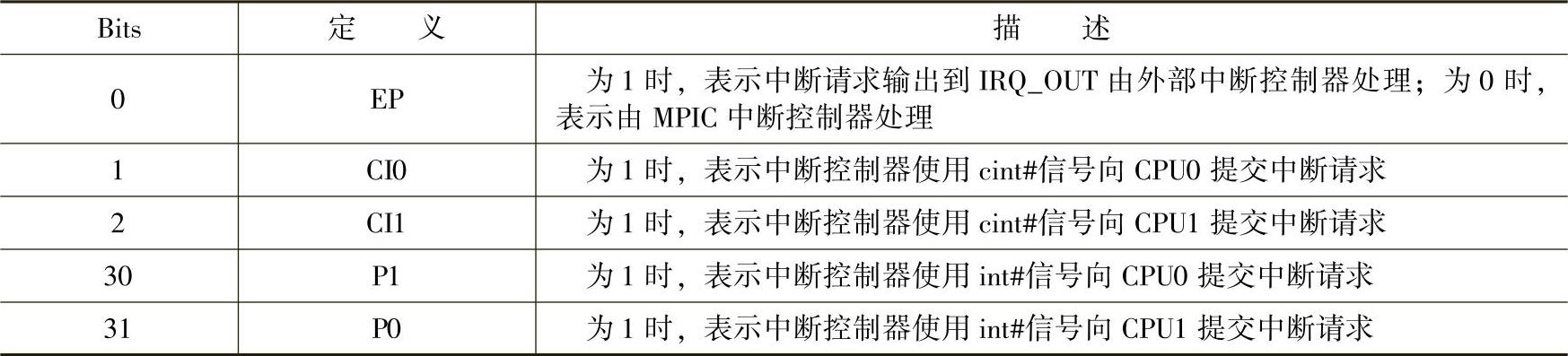

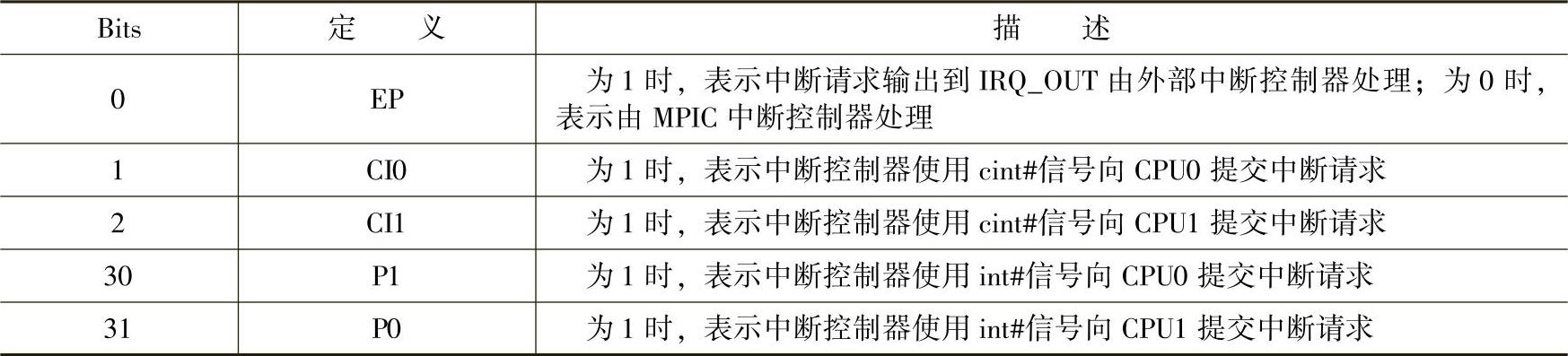

5.MSIDR寄存器组

MSIDR(Shared Message Signaled Interrupt Destination Registers)寄存器组共由8个寄存器组成,分别为MSIDR0~7。其中每一个MSIDRn寄存器对应一个MSIR寄存器。

MPIC中断控制器支持Pass-through方式,在这种方式下,PowerPC处理器可以使用外部中断控制器处理中断请求(这种方法极少使用),而不使用内部中断控制器。MPIC中断控制器可以使用cint#和int#信号提交中断请求,但是绝大多数系统软件都使用int#信号向处理器提交中断请求。

此外在MPC8572处理器中有两个CPU,分别为CPU0和CPU1,MSI机制提交的中断请求可以由CPU0或者CPU1处理。系统软件可以通过设置MSIDRn寄存器完成这些功能,该寄存器各字段的详细描述如表10-6所示。

表10-6 MSIDRn寄存器

相关推荐