HOST处理器对PCI设备的数据访问主要包含两方面内容,一方面是处理器向PCI设备发起存储器和I/O读写请求;另一方面是处理器对PCI设备进行配置读写。HOST处理器访问PCI设备I/O地址空间的过程,与访问存储器地址空间略有不同。处理器必须通过HOST主桥将存储器域的数据访问转换为PCI总线事务才能对PCI总线地址空间进行访问。......

2023-10-20

PowerPC处理器使用OpenPIC中断控制器或者MPIC中断控制器,处理外部中断请求。其中MPIC中断控制器基于OpenPIC中断控制器,但是做出了许多增强,目前Freescale新推出的PowerPC处理器,其中断控制器多与MPIC兼容。

值得注意的是,PowerPC处理器和x86处理器处理MSI报文的方式有较大的不同。其中x86处理器使用的机制比PowerPC处理器更为合理,但是PowerPC处理器的方法使用的硬件资源相对较少。本节将MPC8572处理器为例说明MSI机制的处理过程,在第10.3节介绍x86处理器如何实现MSI机制。

MPIC中断控制器是Freescale的PowerPC处理器使用的通用中断控制器,目前基于E500内核的处理器,如MPC854x、8572等处理器使用这种中断控制器。目前Freescale使用QorIP架构,该架构使用的中断控制器与MPIC兼容。

使用MPIC中断控制器处理MSI中断时,PCIe设备的MSI报文,其目的地址为MPIC中断控制器的MSIIR寄存器。当该寄存器被PCIe设备写入后,MPIC中断控制器将向处理器内核提交中断请求,之后处理器再通过读取MPIC中断控制器的ACK寄存器获得中断向量号,并进行相应的中断处理。这种方式与x86处理器的FSB Interrupt Message机制相比,处理器需要读取ACK寄存器,从而中断处理的延时较大。

目前Freescale的P4080处理器对MPIC中断控制器进行了优化。在P4080处理器中,MPIC中断控制器向处理器提交中断请求的同时,也向处理器内核提交中断向量,处理器内核不必读取ACK寄存器获得中断向量,从而缩短了中断处理延时。使用这种方法的效率与x86处理器使用的FSB Interrupt Message机制相当。

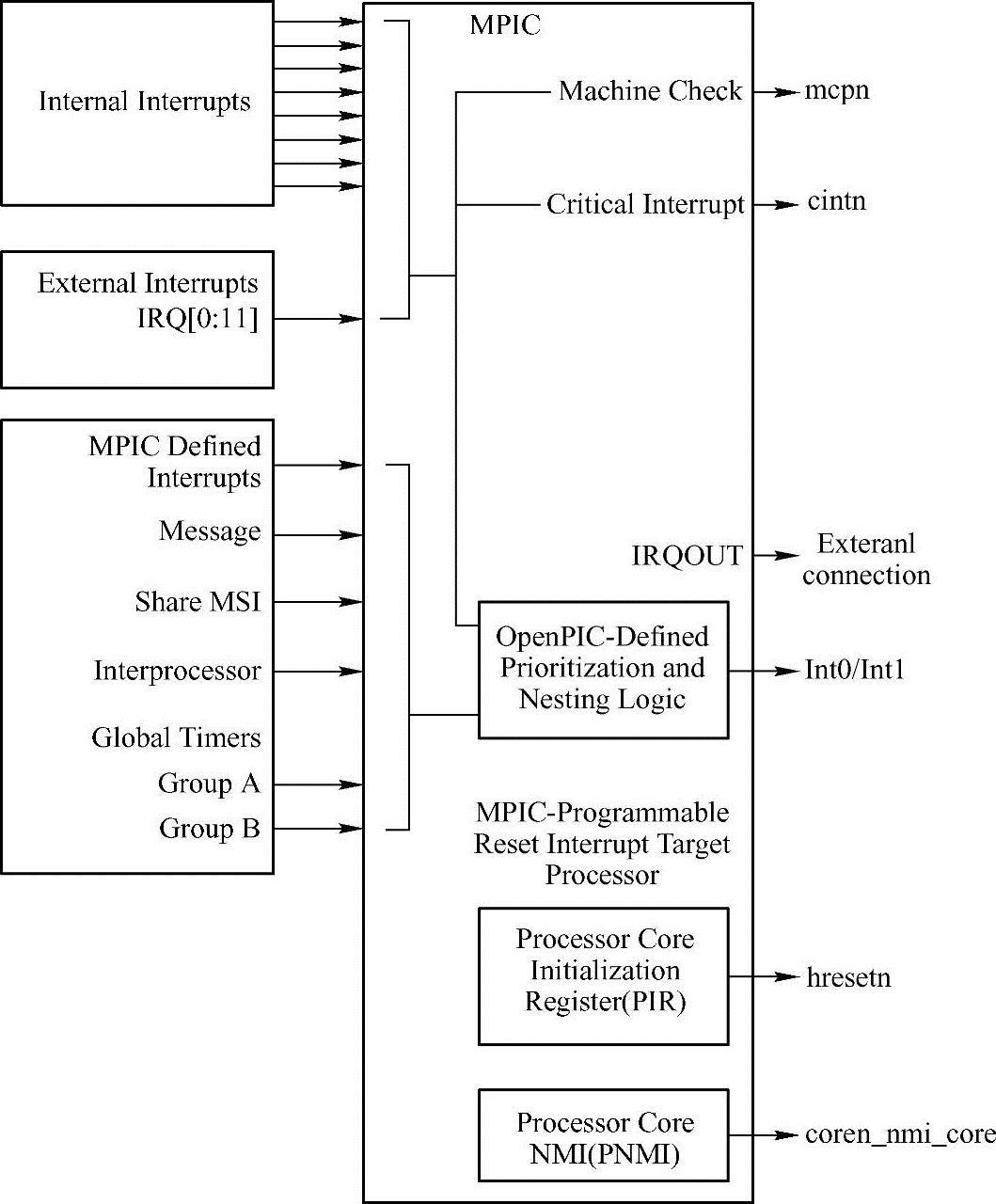

目前Freescale并没有完全公开P4080处理器的实现细节,因此本节仍以MPC8572处理器为例介绍PCIe设备的MSI中断请求。在MPC8572处理器中,MPIC中断控制器的拓扑结构如图10-5所示。(www.chuimin.cn)

图10-5 MPIC中断控制器的拓扑结构

由上图所示,MPIC中断控制器可以处理内部中断请求[68]、外部中断请求,Message、处理器间中断请求和Share MSI中断请求等。而MPIC中断控制器使用Int0、Int1等中断线向处理器提交这些中断请求。其中Internal Interrupts和External Interrupts模块处理MPC8572内部和外部的中断请求,而Share MSI处理来自PCIe设备的MSI或者MSI-X中断请求。

当MPIC中断控制器收到MSI报文后,将使用中断线Int0、Int1或者cintn向处理器内核提交中断请求。处理器内核被中断后,将读取ACK寄存器获得中断向量,然后执行相应的中断服务例程。为此PowerPC处理器设置了一系列寄存器,如下文所示。

有关PCI Express体系结构导读的文章

HOST处理器对PCI设备的数据访问主要包含两方面内容,一方面是处理器向PCI设备发起存储器和I/O读写请求;另一方面是处理器对PCI设备进行配置读写。HOST处理器访问PCI设备I/O地址空间的过程,与访问存储器地址空间略有不同。处理器必须通过HOST主桥将存储器域的数据访问转换为PCI总线事务才能对PCI总线地址空间进行访问。......

2023-10-20

其中,ARM7TDMI是目前使用最广泛的32位嵌入式RICS处理器,属于低端ARM处理器核。ARM9系列微处理器有ARM920T和ARM922T两种类型。ARM10E系列微处理器有ARM1020E、ARM1022E和ARM1026EJ-S共3种类型。基于ARMv6体系结构的ARM11系列处理器将在上述领域发挥巨大的作用。......

2023-11-22

PCIe体系结构以Intel的x86处理器为蓝本实现,已深深地烙下x86处理器的印记。一个基于PCIe架构的处理器系统A如图4-7所示。图4-7 基于PCIe总线的处理器系统A在图4-7的结构中,处理器系统首先使用一个虚拟的PCI桥分离处理器系统的存储器域与PCI总线域。PCI/PCIe总线在x86处理器系统中的地位超乎想象,而且并不仅局限于硬件层面。P4080处理器是Freescale第一颗基于E500mc内核的处理器。多数采用CoreNet架构互连的处理器系统使用目录表法......

2023-10-20

在焊接过程控制中,除了常用的MCU、DSP和ARM等控制处理芯片外,还经常用GAL、CPLD和FPGA等大规模或超大规模数字逻辑芯片,以便扩展上述控制处理芯片的数字逻辑控制功能和I/O接口能力。I/O能力:MultiVolt I/O支持和1.5V、1.8V、2.5V以及3.3V逻辑电平器件的接口。......

2023-06-26

AMD处理器的IOMMU技术与Intel的VT-d技术类似,其完成的主要功能也类似。AMD率先提出了IOMMU的概念,并发布了IOMMU的技术手册,但是Intel首先将这一技术在芯片中实现。AMD处理器使用HT总线连接I/O Hub,其中每一个I/O Hub都含有一个IOMMU,其结构如图13-5所示。图13-5 AMD处理器的IOMMU结构其中每一个IOMMU都使用一个Device Table。表13-1 Next Level字段为0b111时的页表大小AMD64处理器使用这种IO页表方式,可以方便地支持4KB、8KB、……......

2023-10-20

微处理器作为计算机“大脑”,负责大部分控制与执行工作,它决定了计算机的总体性能。当时MITS公司正面临破产窘境,老板爱德华·罗伯茨作为一名计算机爱好者,他敏锐地捕捉到利用Intel微处理器以及相关芯片组装微型计算机的潜在商机,经过一番与英特尔讨价还价,终以极低价格购买到英特尔微处理器。微处理器作为微型计算机“大脑”,其性能快速提升使得微型计算机信息处理能力也发生质的飞跃,为微型计算机更新升级奠定了物质基础。......

2023-11-25

之前介绍的TI处理器都属于ARM体系结构。表2-7TI处理器内核特殊代码目录说明表2-7中有一个奇怪的现象,新一代DaVinci处理器的代码不是在mach-davinci中,而是在mach-omap2中。从这个角度考虑,新一代Da Vinci芯片应该和OMAP2及以后的OMAP处理器在芯片内部结构方面相似度更高一些。因此笔者会以TI官方发布的Android开发包中DM 3730的内核代码为主,进行Linux内核及设备驱动的剖析,但是为了避免局限性,必要时会扩展到其他芯片,以及新版本的内核进行说明。......

2023-11-22

从图5 -18 可看出, 微控制器功能主要包括感应装定功能、转数定距功能、自毁功能。图5-19某型引信专用处理器程序流程图在计转数定距模式, 程序首先配置计转数定距功能需要的片上资源测到预定状态, 然后取出装定数据并以此作为起始圈数对弹丸旋转圈数进行减计数,当装定圈数减到零时给出发火指令。......

2023-06-15

相关推荐