【摘要】:MSI Capability结构共有四种组成方式,分别是32和64位的Message结构,32位和64位带中断Masking的结构。MSI Capability寄存器的结构如图10-1所示。图10-1 MSI Capability结构●Capability ID字段记载MSI Capability结构的ID号,其值为0x05。表10-1 MSI Cabalibities结构的Message Control字段[67] 此时PCI设备配置空间Command寄存器的“Interrupt Disable”位为1。当MSI En able位有效时,该字段存放MSI报文使用的数据。该字段需要与Mask Bits字段联合使用。

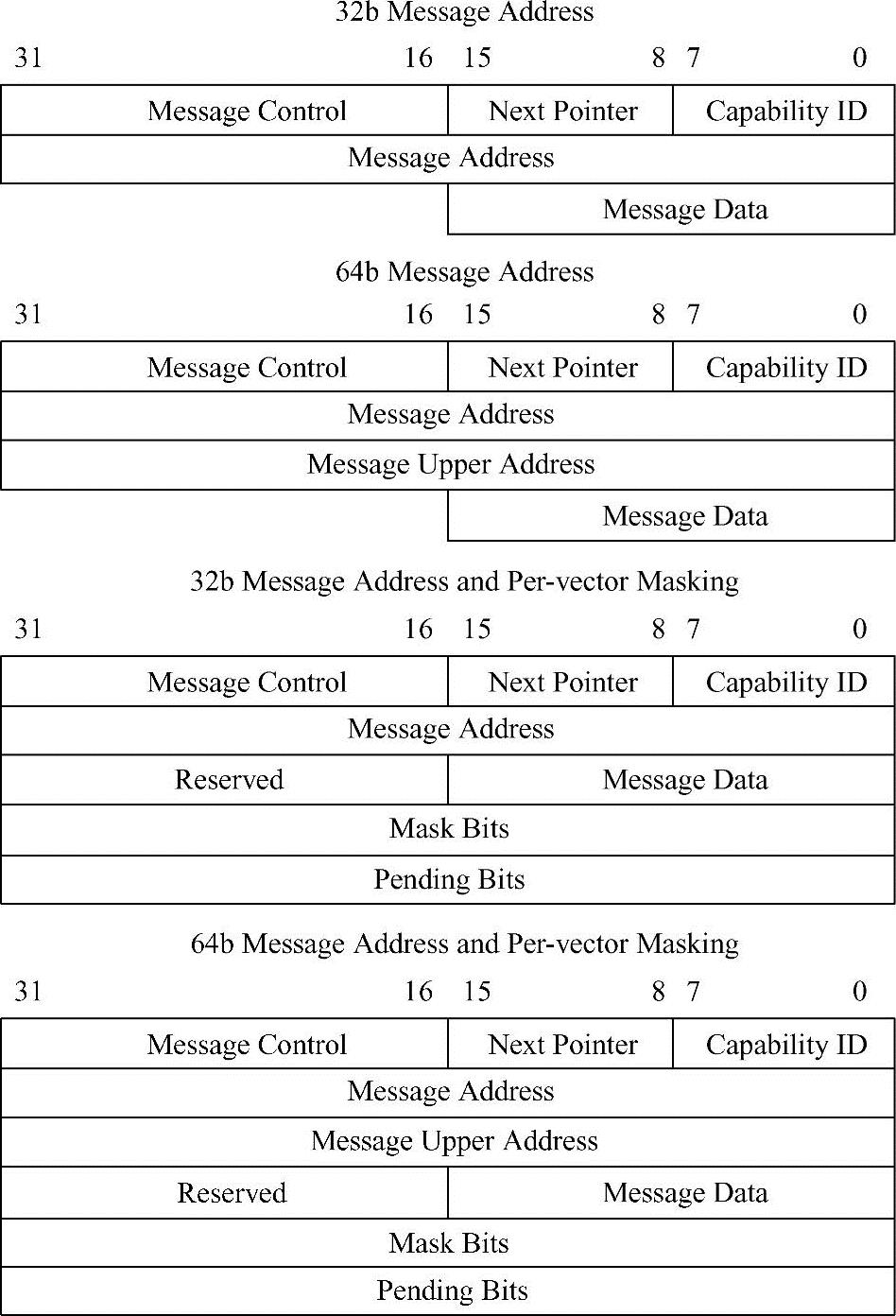

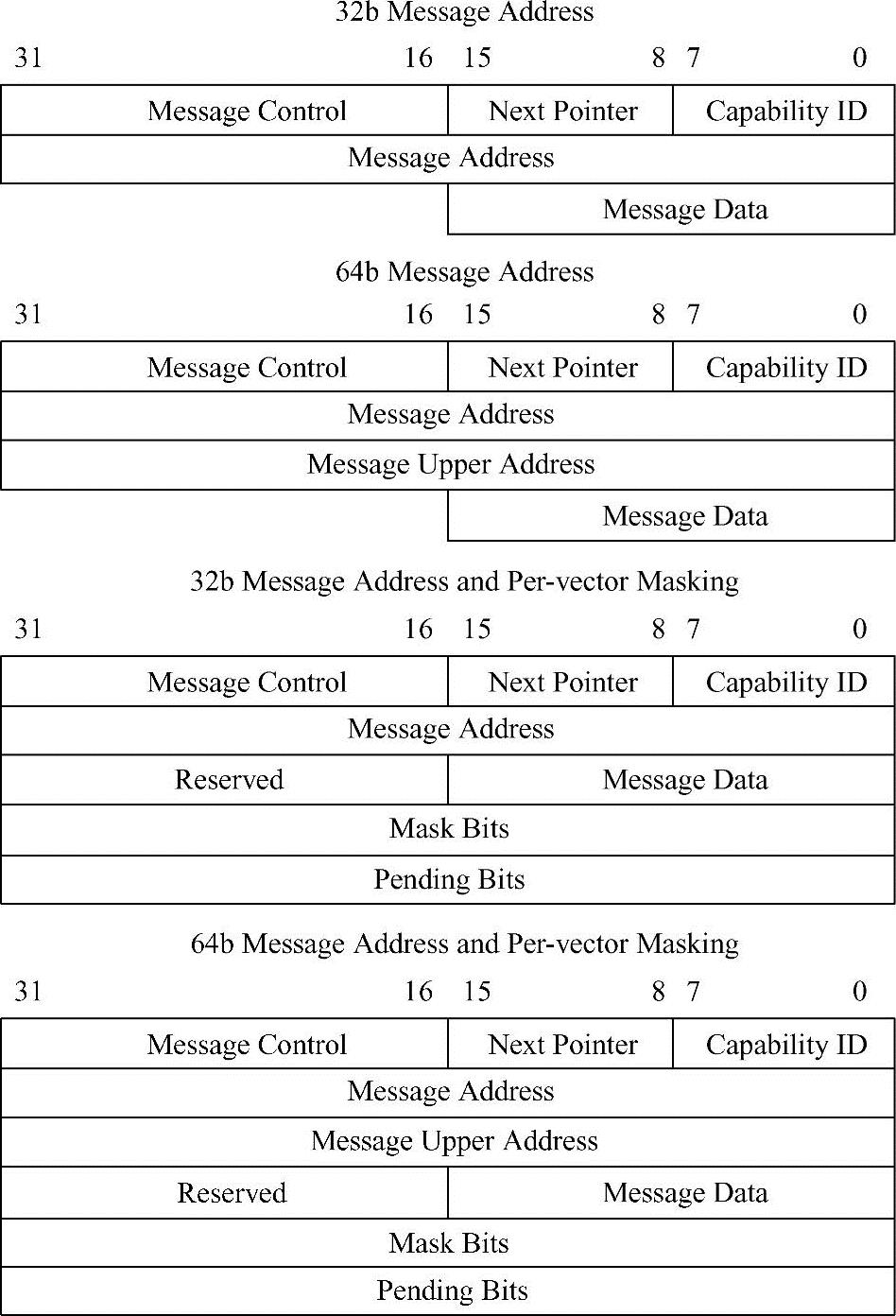

MSI Capability结构共有四种组成方式,分别是32和64位的Message结构,32位和64位带中断Masking的结构。MSI报文可以使用32位地址或者64位地址,而且可以使用Masking机制使能或者禁止某个中断源。MSI Capability寄存器的结构如图10-1所示。

图10-1 MSI Capability结构

●Capability ID字段记载MSI Capability结构的ID号,其值为0x05。在PCIe设备中,每一个Capability结构都有唯一的ID号。

●Next Pointer字段存放下一个Capability结构的地址。

●Message Control字段。该字段存放当前PCIe设备使用MSI机制进行中断请求的状态与控制信息,如表10-1所示。

表10-1 MSI Cabalibities结构的Message Control字段

[67] 此时PCI设备配置空间Command寄存器的“Interrupt Disable”位为1。(www.chuimin.cn)

●Message Address字段。当MSI Enable位有效时,该字段存放MSI存储器写事务的目的地址的低32位。该字段的31∶2字段有效,系统软件可以对该字段进行读写操作;该字段的第1~0位为0。

●Message Upper Address字段。如果64 bit Address Capable位有效,该字段存放MSI存储器写事务的目的地址的高32位。

●Message Data字段,该字段可读写。当MSI En able位有效时,该字段存放MSI报文使用的数据。该字段保存的数值与处理器系统相关,在PCIe设备进行初始化时,处理器将初始化该字段,而且不同的处理器填写该字段的规则并不相同。如果Multiple Message Enable字段不为0b000时(即该设备支持多个中断请求时),PCIe设备可以通过改变Message Data字段的低位数据发送不同的中断请求。

●Mask Bits字段。PCIe总线规定当一个设备使用MSI中断机制时,最多可以使用32个中断向量,从而一个设备最多可以发送32种中断请求。Mask Bits字段由32位组成,其中每一位对应一种中断请求。当相应位为1时表示对应的中断请求被屏蔽,为0时表示允许该中断请求。系统软件可读写该字段,系统初始化时该字段为全0,表示允许所有中断请求。该字段和Pending Bits字段对于MSI中断机制是可选字段,但是PCIe总线规范强烈建议所有PCIe设备支持这两个字段。

●Pending Bits字段。该字段对于系统软件是只读位,PCIe设备内部逻辑可以改变该字段的值。该字段由32位组成,并与PCIe设备使用的MSI中断一一对应。该字段需要

与Mask Bits字段联合使用。

当Mask Bits字段的相应位为1时,如果PCIe设备需要发送对应的中断请求,Pending Bits字段的对应位将被PCIe设备的内部逻辑置1,此时PCIe设备并不会使用MSI报文向中断控制器提交中断请求;当系统软件将Mask Bits字段的相应位从1改写为0时,PCIe设备将发送MSI报文向处理器提交中断请求,同时将Pending Bit字段的对应位清零。在设备驱动程序的开发中,有时需要联合使用Mask Bits和Pending Bits字段防止处理器丢弃中断请求[67]。

相关推荐