在PCIe总线中存在两种仲裁机制,分别是基于VC和基于端口的仲裁机制。端口仲裁机制主要针对RC和Switch,当多个Ingress端口需要向同一个Egress端口发送数据报文时需要进行端口仲裁。当RC的端口1和端口3同时访问Endpoint C时,RC的端口2需要进行端口仲裁,决定来自RC哪个端口的数据可以率先通过。PCIe总线规定,系统设计者可以使用以下三种方式进行端口仲裁。......

2023-10-20

PCIe总线使用FCP(Flow Control Packets)传递Credit信息,FCP是一种DLLP,该报文的使用与事务层的接收缓存直接相关,但是对事务层透明,该报文产生于数据链路层,终止于数据链路层。PCIe总线定义了以下FCP,如表9-4所示。

表9-4 PCIe总线定义的FCP

①V2V1V0与VC对应,PCIe总线规定VC个数的最大值为8,因此使用3位存放VC号。

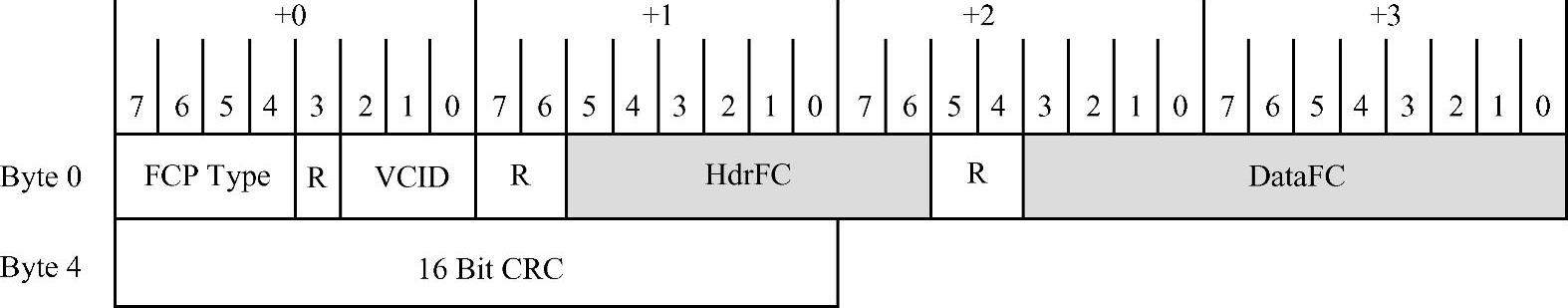

由上表所示FCP共分为三大类InitFC1、InitFC2和Update FC。在这三类报文中有3个重要的字段。其中HdrFC字段存放Header的Credit;DataFC字段存放Data的Credit;而VC ID字段存放不同的VC号。其报文格式如图9-12所示。

图9-12 FCP的格式

Current节点使用以上报文向Upstream节点发送Credit信息,其中InitFC1和InitFC2与VC的初始化相关,而Update FC负责向Upstream节点反馈Credit信息。我们首先讲述Cur-rent节点如何使用InitFC1和InitFC2报文初始化VC的流量控制,并在第9.3.4节讲述如何使用Update FC报文实现PCIe总线的流量控制。

在各个节点能够正常使用之前,首先需要对VC0进行初始化。当VC0初始化完毕之后,PCIe设备可以对VC1~7进行初始化。在VC0初始化完成之前,设备不能接收任何TLP,而VC0初始化完毕后,PCIe总线的相应节点在使用VC0接收TLP的同时,初始化其他VC。在VC的初始化过程中存在两个状态,FC_INIT1和FC_INIT2。

PCIe总线的数据链路层共有三个状态,分别为DL_Inactive(PCIe链路无效状态,链路不可用或者链路上没有连接有效设备)、DL_Init(PCIe链路可用,此时将进行VC0的初始化)和DL_Active(链路可以正常使用)。(www.chuimin.cn)

当Current节点的数据链路层进入DL_Init状态时,该节点的VC0将进入FC_INIT1状态。Cur-rent节点将在FC_INIT1状态首先初始化VC0,之后才能初始化其他VC。其他VC的使能位在Current节点的配置空间中,当系统软件打开这些使能位时,Current节点将初始化其他VC。

当Current节点的VC进入FC_INIT1状态时,事务层需要首先禁止该VC发送数据报文,随后Current节点将向Upstream节点依此发送InitFC1-P、InitFC1-NP和InitFC1-Cpl[64]报文初始化Upstream节点使用的Credit。

此时Current节点还可能收到来自Downstream节点的InitFC1-P、InitFC1-NP和InitFC1-Cpl报文,并初始化Current节点的Credit。当Current节点收到这些来自Downstream节点的FCP后,将设置对应缓冲的FI1状态位为1。

当Current节点所有缓存的FI1状态位有效后,VC将进入FC_INIT2状态。Current节点进入FC_INIT2状态之前,Upstream节点获得的Credit和Current节点的空余缓存大小相等,Current节点获得的Credit和Downstream节点的空余缓存大小相等。这一点和其他流量控制机制类似,即Crd_Bal的初始值为Buf_Alloc。

PCIe总线还提供了FC_INIT2状态,该状态的主要功能是验证FC_INIT1的结果。当节点进入FC_INIT2状态时,与流量控制相关的缓存已经初始化完毕。PCIe总线设置FC_INIT1和FC_INIT2这两个状态与数据链路层的状态机相关。

如第7.1.1节所示,当数据链路层处于DL_Init状态时,将初始化PCIe总线的流量控制机制。当VC处于FC_INIT1状态时,数据链路层通知事务层DL_Down状态位有效,此时事务层不能向对端设备发送TLP,从而流量控制机制的初始化可以在一个“相对没有干扰的环境”下进行。

而当Current节点的VC进入FC_INIT2状态时,事务层需要首先禁止使用这条VC发送报文,之后Current节点向Upstream节点依此发送InitFC2-P、InitFC2-NP和InitFC2-Cpl报文初始化Upstream节点的发送缓冲。当Upstream节点收到这些报文之后,将丢弃这些报文中包含的Credit信息,并设置相应的FI2状态位。

同理Current节点也将收到来自Downstream节点的InitFC2-P、InitFC2-NP和InitFC2-Cpl报文,并设置Current节点的FI2状态位。当所有数据缓存的FI2状态位有效后,将完成PCIe链路流量控制机制的初始化。最后数据链路层通知事务层DL_Active状态位有效,此时事务层可以使用这个VC发送TLP。

有关PCI Express体系结构导读的文章

在PCIe总线中存在两种仲裁机制,分别是基于VC和基于端口的仲裁机制。端口仲裁机制主要针对RC和Switch,当多个Ingress端口需要向同一个Egress端口发送数据报文时需要进行端口仲裁。当RC的端口1和端口3同时访问Endpoint C时,RC的端口2需要进行端口仲裁,决定来自RC哪个端口的数据可以率先通过。PCIe总线规定,系统设计者可以使用以下三种方式进行端口仲裁。......

2023-10-20

Linux PowerPC初始化PCI总线树的步骤与Linux x86类似,也调用了一些Linux系统中与PCI总线相关的通用函数。但是PowerPC处理器使用的HOST主桥与x86处理器并不相同,因此Linux PowerPC初始化PCI总线树的过程与Linux x86有些差别。本节以MPC8572处理器为例,说明Linux PowerPC初始化PCI总线树的过程。Linux PowerPC在引入了Open Firmware机制[22]后,使用dts文件管理PCI总线控制器。Linux PowerPC执行完毕setup_arch函数后,还会执行一些和PCI总线......

2023-10-20

PCIe设备必须支持L0s状态。L0s状态是一个低功耗状态,PCIe设备进入或者退出该状态不需要系统软件的干预,其状态转换由硬件控制完成。图8-13 L0s的接收状态机接收逻辑RX处于L0状态时,如果收到1个EIOS序列后,将进入Rx_L0s.Entry状态。接收逻辑RX在Rx_L0s.Idle状态中将持续监测接收链路,如果发现对端设备的发送逻辑TX退出“Electrical Idle”状态时,接收逻辑RX将进入Rx_L0s.FTS状态。......

2023-10-20

从那时起,PCI总线一直在处理器体系结构中占有重要地位。IAL是现代PC体系架构的重要奠基者。除了以上规范之外,PCISIG还推出了一系列和PCI总线直接相关的规范。其中PCI-to-PCI桥规范最为重要,理解PCI-to-PCI桥是理解PCI体系结构的基础;而CompactPCI总线规范多用于具有背板结构的大型系统,并支持热插拔。PCI和PCI-X总线使用单端并行信号进行数据传递,由于单端信号容易被外部系统干扰,其总线频率很难进一步提高。......

2023-10-20

在一段程序中,存在大量的分支预测指令,因而在某种程度上增加了指令Fetch的难度。但是分支预测单元并不会每次都能正确判断分支指令的执行路径,这为指令Fetch制造了不小的麻烦,在这个背景下许多分支预测策略应运而生。在PowerPC处理器中,条件转移指令“bc”表示Taken;而“bc-”表示Not Taken。BTB的功能相当于存放转移指令的Cache,其状态机转换也与Cache类似。转移指令B执行完毕后,将实际执行结果Rc更新到BHR寄存器中,并同时更新PHT中对应的Entry。......

2023-10-20

如图8-6所示,Detect状态由Detect.Quiet、Detect.Active两个子状态组成。在正常情况下,PCIe链路将从Detect状态迁移到Polling状态。而在Detect状态中,PCIe设备的发送逻辑TX将直接进入到“Electrical Idle”状态,并不会使用Idle序列通知对端设备的接收逻辑RX。当PCIe设备处于Detect.Quiet状态超过12ms之后,或者检测到PCIe链路上的任何一个Lane退出“Electrical Idle”状态时,PCIe设备将进入Detect.Active状态。......

2023-10-20

Linux系统在初始化时,将在do_initcalls函数中执行__initcall_xyz_initx函数,从而执行xyz_init函数。Linux系统使用这种方法规范初始化模块的执行,并保证这些模块可以按照指定的顺序依次执行。在Linux内核的System.map[4]文件中,可以找到在__early_initcall_end和__initcall_end之间所有的函数指针,其中与PCI总线初始化相关的函数如源代码14-4所示,这些函数将按照在以下源代码中出现的顺序依次执行。......

2023-10-20

本章以Montevina平台为例,说明在x86处理器系统中,PCIe体系结构的实现机制。Montevina平台是Intel提供的一个笔记本平台。Montevina平台的拓扑结构如图5-1所示。图5-1 Montevina平台的拓扑结构Montevina平台使用一个虚拟的FSB-to-PCI桥[13]将FSB总线与外部设备分离,这个虚拟PCI桥的上方连接FSB总线,之下连接PCI总线0。在Montevina平台的GMCH和ICH中,所有的外部设备,如存储器控制器,图形控制器等都是虚拟PCI设备,都具有独立的PCI配置空间。......

2023-10-20

相关推荐