【摘要】:PCIe总线将Header和Data缓存分离有利于Data缓存的合理使用。在PCIe总线中,不同的TLP使用对应缓存的Unit数量也不同,Current节点有时需要两种缓存才能接收一个TLP。这也意味着在PCIe设备的VC中,缓存之间存在依赖关系。报文长度的不确定性为PCIe总线流量控制机制带来了许多难以解决的问题。造成这种现象的主要原因是PCIe总线源于PCI总线,其主要应用来自PC领域而不是通信领域。PCIe总线使用Credit-Based流控机制,Upstream节点在发送TLP时,必须首先获得Cur-rent节点相应缓存的Credit。

在PCIe总线的节点中,一个VC的接收缓存由PH(Posted Header)缓存、PD(Posted Data)缓存、NPH(Non-Posted Header)缓存、NPD(Non-Posted Data)缓存、CplH(Com-pletion Header)缓存和CplD(Completion Data)缓存组成。

●PH缓存存放存储器写请求TLP和Message报文使用的TLP头。

●PD缓存存放存储器写请求TLP和Message报文使用的Payload。

●NPH缓存存放Non-Posted请求TLP使用的TLP头。

●NPD缓存存放Non-Posted请求TLP使用的Payload。在Non-Posted请求TLP中,如存储器读请求TLP并不含有Payload字段,但是I/O和配置写请求TLP使用Payload字段。

●CplH缓存存放完成报文使用的TLP头。

●CplD缓存存放完成报文使用的Payload。如上文所述,完成报文分为两大类,带数据的完成报文和不带数据的完成报文。其中不带数据的完成报文不需要使用CplD缓存。

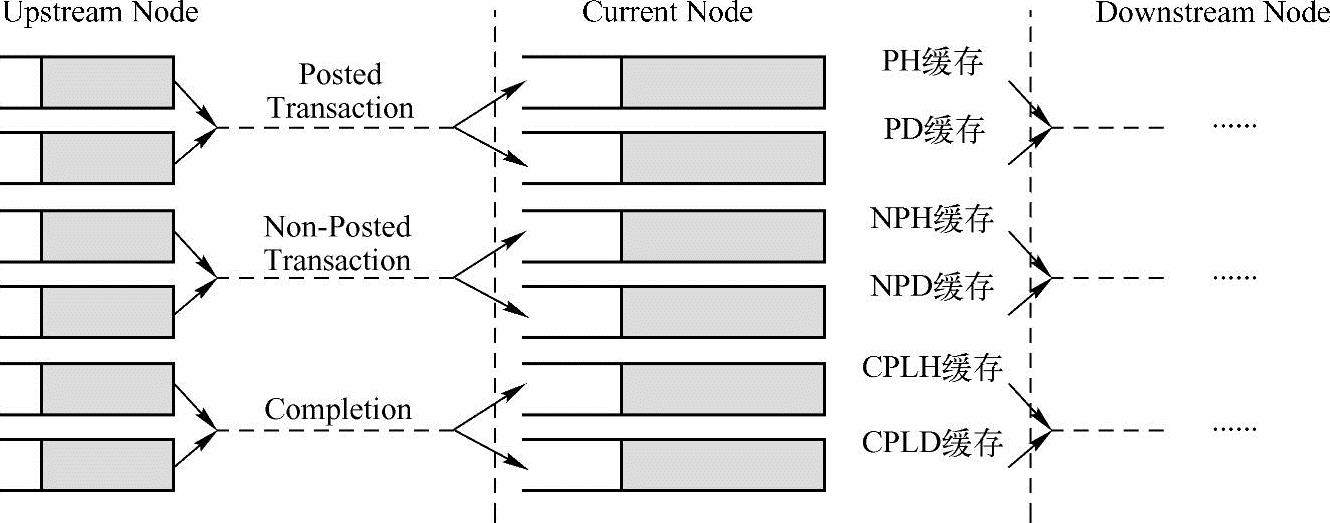

在PCIe总线中,一个TLP从Upstream节点传送到Current节点时,必须同时具备多个缓存的Credit后才能发送。如存储器写请求TLP,需要同时具备PH和PD缓存的Credit,才能发送;而“不带数据的”存储器读完成TLP,仅需要具备CplH缓存即可。这些缓存在PCIe设备中的组成结构如图9-10所示。

图9-10 PCIe总线Current节点的缓冲管理

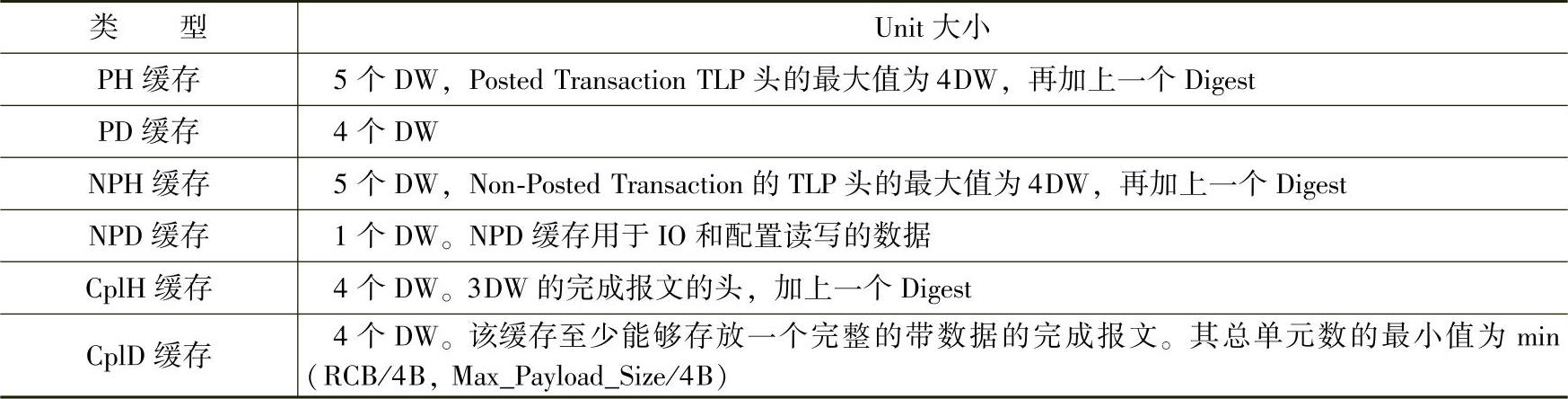

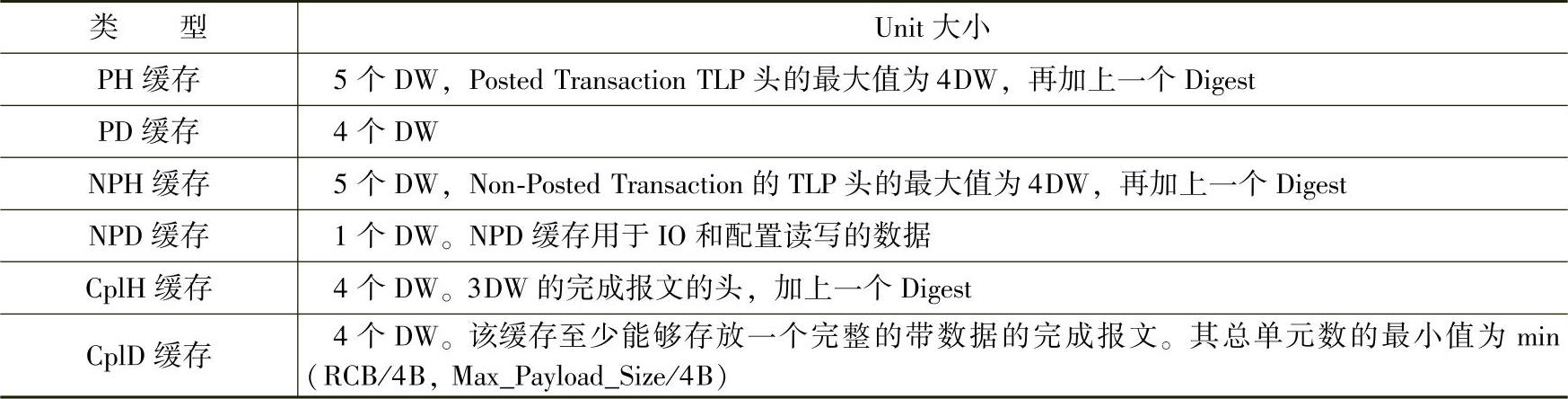

如表6-2所示,PCIe总线根据Type字段将TLP分为15种,而根据这些TLP的传输特性,可以将这些TLP分为Posted Transaction、Non-Posted Transaction和Comple tion三大类。在PCIe总线中,这三大类数据传送需要遵循各自的规则,这些Transaction也有各自的特点。这三大类Transaction在进行数据传递时需要使用不同的缓存,这些缓存由多个单元(Unit)组成。每个Unit的大小与缓存类型相关,如表9-1所示。

表9-1 PCIe总线缓存的单元大小(https://www.chuimin.cn)

PCIe总线将Header和Data缓存分离的主要原因是,一个TLP的Header大小是固定的,如PH和NPH大小在5DW之内,CplH大小在4DW之内;而Data的大小并不固定,除了NPD的大小为1个DW之外,其他数据报文的长度由TLP的Length字段确定,并不固定。PCIe总线将Header和Data缓存分离有利于Data缓存的合理使用。

PCIe总线规范将这些缓存使用的Unit统称为FC(Flow Control)Unit,下文将以FC Unit简称这些对应缓存的Unit。因为Header的大小固定,所以Header缓存能够精确地预知可以容纳几个Header;而由于Data的大小并不固定,Data缓存无法精确预知可以存放几个Data,当然Data缓存也不可能将Data的基本单位设置为Max_Payload_Size参数。因为这样做不仅不合理,而且非常浪费资源。将Header和Data缓存分离,有利于Data缓存使用类似Adap-tive流量控制的方法使所有Data共用一个缓存,从而提高了Data缓存的利用率。但是也造成TLP因为不能同时具有Head和Data缓存,而无法传送。

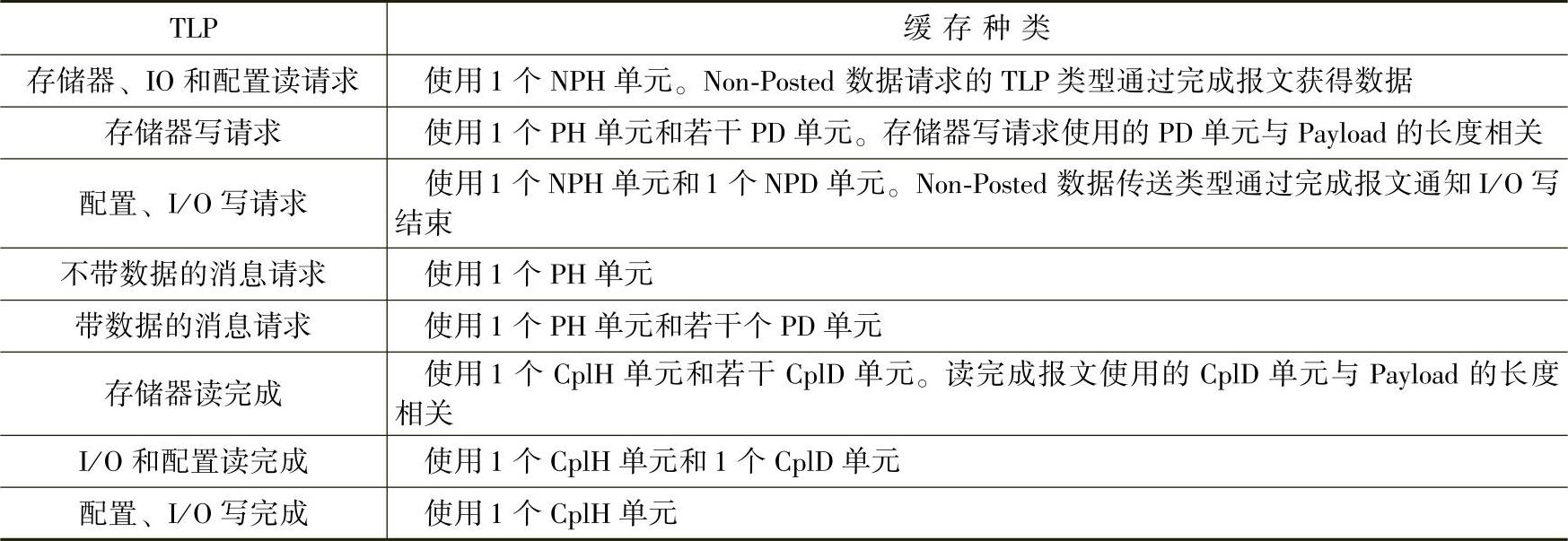

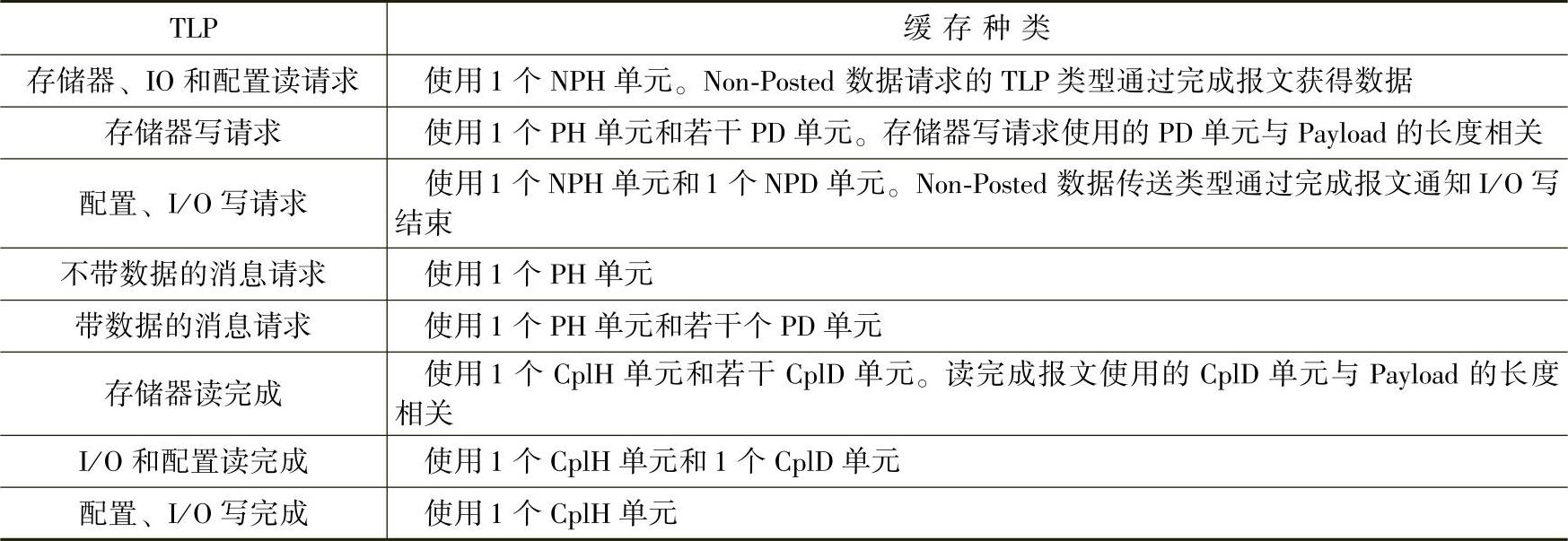

在PCIe总线中,不同的TLP使用对应缓存的Unit数量也不同,Current节点有时需要两种缓存才能接收一个TLP。不同TLP使用的缓存数目如表9-2所示。

表9-2 不同TLP使用的缓存

由上表所示,一个TLP可能需要使用两种缓存,如存储器写请求需要使用PH和PD缓存。这也意味着在PCIe设备的VC中,缓存之间存在依赖关系。当Upstream节点向Current节点进行存储器写时,发送方必须同时具有PH和PD两个缓存的Credit才能进行;而向Current节点发送读完成TLP时,Upstream节点必须同时具有CplH和CplD两个缓存的Credit才能进行。这为PCIe总线的流量控制带来了额外的麻烦。

此外,在PCIe总线中,进行存储器写和存储器读完成TLP时,究竟需要多少个PD或者CplD单元是随TLP而变的,VC无法预知确切的单元数量。无论VC采用何种缓冲分配策略,这种“不可预知”都会给流量控制带来巨大的麻烦。

报文长度的不确定性为PCIe总线流量控制机制带来了许多难以解决的问题。造成这种现象的主要原因是PCIe总线源于PCI总线,其主要应用来自PC领域而不是通信领域。PCIe总线为了向前兼容PCI总线,做出了许多功能上的牺牲。

PCIe总线使用Credit-Based流控机制,Upstream节点在发送TLP时,必须首先获得Cur-rent节点相应缓存的Credit。如Upstream节点发送存储器写请求时,需要同时具有Current节点中PH缓存和PD缓存的Credit,才能进行。

相关推荐