在Upstream节点、Current节点和Downstream节点中存在两个VC,下文以其中的一个VC为例,说明如何使用Credit-Based机制进行数据传递。为简便起见,本章仅讨论在单向通路下,Credit-Based流量控制机制的原理与实现。Credit-Based机制需要使用以下参数进行报文传递。Credit-Based流量控制使用的各个参数之间的关系如图9-5所示。Current节点将这个值作为Credit,发送到Upstream节点。......

2023-10-20

上文讲述了基于单个VC的流控机制,实际上在Upstream、Current和Downstream节点中一般含有多个VC。多个VC之间如何合理地使用缓存值得重点关注,在实际设计中,可以为每一个VC设置独立接收缓存,也可以使多个VC共享同一个接收缓存。在FCVC的实现中,可以根据实际情况选择独立缓存或者共享缓存。

其中,每一个VC都使用独立接收缓存的流量控制方法称为静态(Static)流量控制;而使用共享缓存的流量控制方法称为自适应(Adaptive)流量控制。

假定在一个系统中,一共具有n条VC,而且这几条VC都使用N23算法进行流量控制,那么在使用Static流量控制方式时,该系统一共需要的缓冲大小为(n×N2+N3)×Packet_Size[62]。如果(n×N2+N3)×Packet_Size并不是很大时,为了使数据链路获得更大的带宽,可以使用Static流量控制。使用这种方法,也将极大地简化缓冲管理的设计难度。

值得注意的是,在一个系统工程的架构设计中,应当重点关注“Critical Path”的设计,需要容忍非“Critical Path”的不完美。当(n×N2+N3)×Packet_Size的值大到了可以容忍的范围之外时,设计者必须考虑如何减少Current节点的接收缓存大小。Static流量控制是针对每一个VC都是按照全负荷运转的情况,在绝大多数应用中,几乎不可能出现每一条VC都被充分利用的情况,因为多条VC共享一个物理链路,不可能出现所有VC都在全负荷运行的情况。为此在系统设计时可以使用Adaptive流量控制方法。

Adaptive流量控制的本质是Current节点中,所有VC共享一个接收缓存,从而这个缓存可以远小于(n×N2+N3)×Packet_Size。因为在绝大多数时间内,数据链路的多条VC不可能都被充分使用,因此并不需要为每条VC都提供N2缓冲,而是为所有VC统一提供接收缓冲,从而合理使用这些接收缓冲。

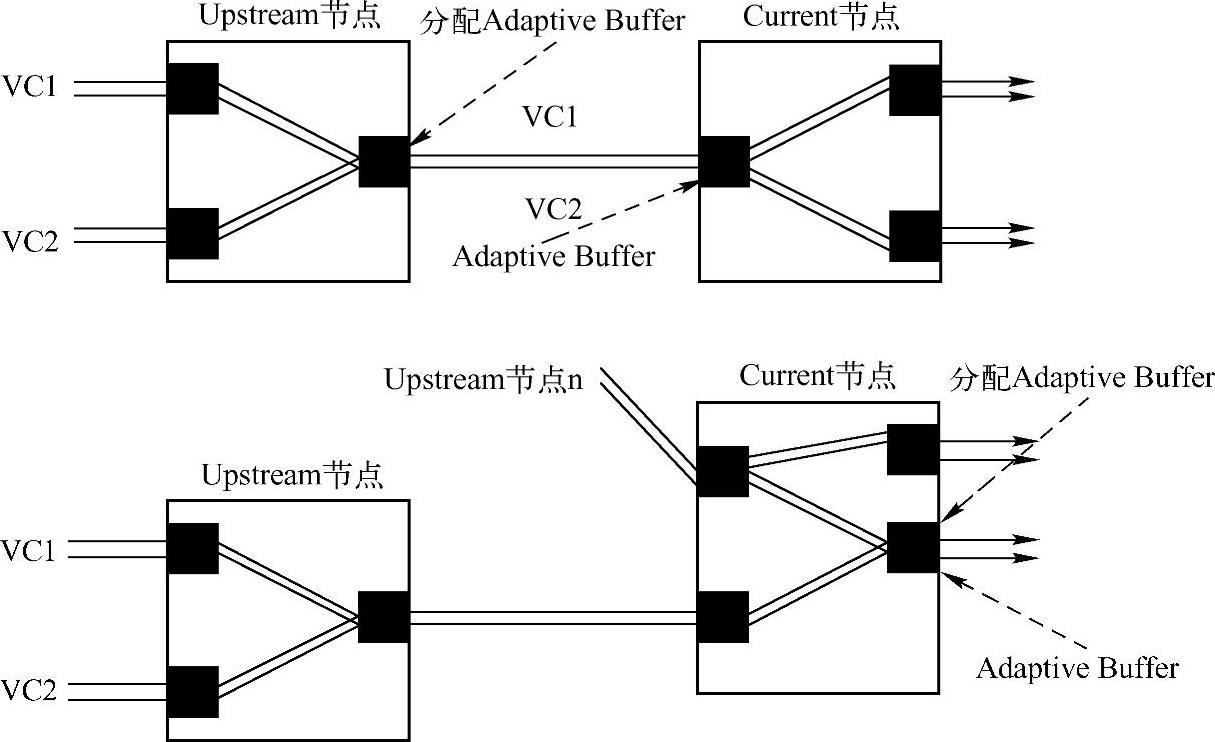

目前接收缓存的分配常使用两种算法,分别是Sender-Oriented和Receiver-Oriented管理算法。这两种算法的缓冲设置如图9-9所示。使用Sender-Oriented管理算法时,Adaptive Buffer的分配在Upstream节点中完成,如果系统中有多个Upstream节点,Current节点需要在其接收端点处为每个Upstream节点准备Adaptive Buffer,而且Current节点并不知道Up-stream节点的使用情况,这为Current节点的缓冲管理带来了不小的困难。(www.chuimin.cn)

图9-9 Sender-Oriented和Receiver-Oriented管理算法

而使用Receiver-Oriented管理算法可以有效避免这类困难,使用这种算法时,所有来自Upstream节点的数据报文在Current节点的发送端准备一个Adaptive Buffer,对这个Buffer的分配也在Current节点内部完成。这两种算法的具体实现都较为复杂,本节并不详细介绍这些算法,在PCIe总线中,RC和Switch的硬件设计将会涉及这些内容,而EP无需关心这些问题。

图中的上半部分是Sender-Oriented管理算法的示意图,而下半部分是Receiver-Oriented管理算法的示意图。由图9-9可以发现,使用这两种算法时Adaptive Buffer都在Current节点中,只是位置不同。

有关PCI Express体系结构导读的文章

在Upstream节点、Current节点和Downstream节点中存在两个VC,下文以其中的一个VC为例,说明如何使用Credit-Based机制进行数据传递。为简便起见,本章仅讨论在单向通路下,Credit-Based流量控制机制的原理与实现。Credit-Based机制需要使用以下参数进行报文传递。Credit-Based流量控制使用的各个参数之间的关系如图9-5所示。Current节点将这个值作为Credit,发送到Upstream节点。......

2023-10-20

目前流量控制从理论到实现大多基于多通道技术,本节也仅讨论基于多通道的流量控制的基本原理。目前几乎所有流量控制算法的核心都是根据接收端缓冲区的容量,向发送端提供反馈。流量控制针对端到端的数据传递,目前流行的流量控制方法共有两种,分别为Rate-Based机制和Credit-Based机制。......

2023-10-20

PCIe总线将Header和Data缓存分离有利于Data缓存的合理使用。在PCIe总线中,不同的TLP使用对应缓存的Unit数量也不同,Current节点有时需要两种缓存才能接收一个TLP。这也意味着在PCIe设备的VC中,缓存之间存在依赖关系。报文长度的不确定性为PCIe总线流量控制机制带来了许多难以解决的问题。造成这种现象的主要原因是PCIe总线源于PCI总线,其主要应用来自PC领域而不是通信领域。PCIe总线使用Credit-Based流控机制,Upstream节点在发送TLP时,必须首先获得Cur-rent节点相应缓存的Credit。......

2023-10-20

流量控制的概念起源于网络通信。我们假设图9-2中Node 4将报文转发到Node 5的速度低于Node 3发送报文的速度。在这种情况下,Node 4将成为整个传送路径上的瓶颈,无论Node 4中的缓存1和2有多大,总会被填满,从而造成节点拥塞。为了避免这类事件发生,网络中的各个组成部件需要对数据传送进行一定的流量控制,合理地接收和发送报文。而流量控制的作用是合理地管理这两类资源,使这些资源能够被有效利用。......

2023-10-20

在PCI总线中,接口控制信号的主要作用是保证数据的正常传递,并根据PCI主从设备的状态,暂停、终止或者正常完成当前总线事务,其主要信号如下。当PCI设备获得总线的使用权后,将置该信号有效,即置为低,启动PCI总线事务,当结束总线事务时,将置该信号无效,即置为高。该信号可以和IRDY#信号联合使用,在PCI总线事务上插入等待周期,对PCI总线的数据传送进行控制。......

2023-10-20

PCIe总线使用的软件电源管理机制与PCI PM兼容。图4-15 Power Management Capability结构Capability ID字段记载Power Management Capability结构的ID号,其值为0x01。该寄存器的结构如图4-16所示,其中PMCR寄存器在Power Management Capability结构的第3~2字节中。系统软件将这个请求处理完毕后,将通知这个PCI设备,之后该PCI设备将PME#信号置为无效。D2位为1表示PCIe设备支持D2状态;D1位为1表示PCIe设备支持D1状态。图4-17 Power Management Status/Control寄存器●Power State字段可读写,该字段记录PCIe设备所处的状态。......

2023-10-20

但是PCI总线规范没有规定PCI设备的INTx信号如何与中断控制器的IRQ_PINx#信号相连,这为系统软件的设计带来了一定的困难,为此系统软件使用中断路由表存放PCI设备的INTx信号与中断控制器的连接关系。在一些简单的嵌入式处理器系统中,Firmware并没有提供中断路由表,系统软件开发者需要事先了解PCI设备的INTx信号与中断控制器的连接关系。此时外部设备与中断控制器的连接关系由硬件设计人员指定。......

2023-10-20

相关推荐