【摘要】:PCIe设备必须支持L0s状态。L0s状态是一个低功耗状态,PCIe设备进入或者退出该状态不需要系统软件的干预,其状态转换由硬件控制完成。图8-13 L0s的接收状态机接收逻辑RX处于L0状态时,如果收到1个EIOS序列后,将进入Rx_L0s.Entry状态。接收逻辑RX在Rx_L0s.Idle状态中将持续监测接收链路,如果发现对端设备的发送逻辑TX退出“Electrical Idle”状态时,接收逻辑RX将进入Rx_L0s.FTS状态。

PCIe设备必须支持L0s状态。L0s状态是一个低功耗状态,PCIe设备进入或者退出该状态不需要系统软件的干预,其状态转换由硬件控制完成。L0s的状态转换由两部分组成,一个是接收状态机,另一个是发送状态机。

同一个PCIe设备的发送逻辑TX和接收逻辑RX,在同一时刻可能处于不同的链路状态,其中一个为L0,而另一个为L0s。例如当一个EP进行DMA写操作时,其发送逻辑TX一直被使用,因此处于L0状态,而接收逻辑RX可能长时间没有被使用,从而可以暂时处于L0s状态,以降低功耗。

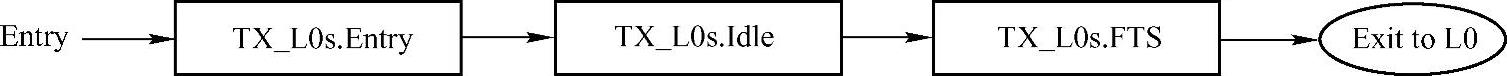

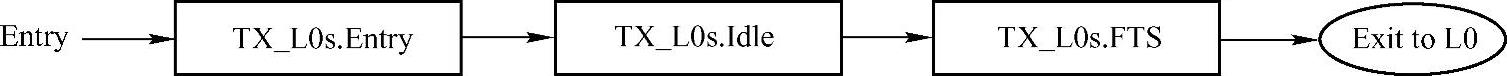

1.发送逻辑TX状态机

L0s的发送状态机如图8-12所示,该状态机由Tx_L0s.Entry、Tx_L0s.Idle和Tx_L0s.FTS状态组成。

图8-12 L0s的发送状态机

PCIe设备处于L0状态发现链路为临时“空闲”状态时,将进入Tx_L0s.Entry状态。处于该状态时,发送逻辑TX首先向对端发送1或者2个EIOS序列[56],之后进入Electrical Idle状态。再经过20ns延时后,发送逻辑TX进入Tx_L0s.Idle状态。

当发送逻辑TX处于Tx_L0s.Idle状态时,如果PCIe设备需要发送数据报文,发送逻辑TX将退出Tx_L0s.Idle状态,进入Tx_L0s.FTS状态。发送逻辑TX处于Tx_L0s.FTS状态时,向对端顺序发送N_FTS个FTS序列[57]和1个SKP序列之后,将进入L0状态。

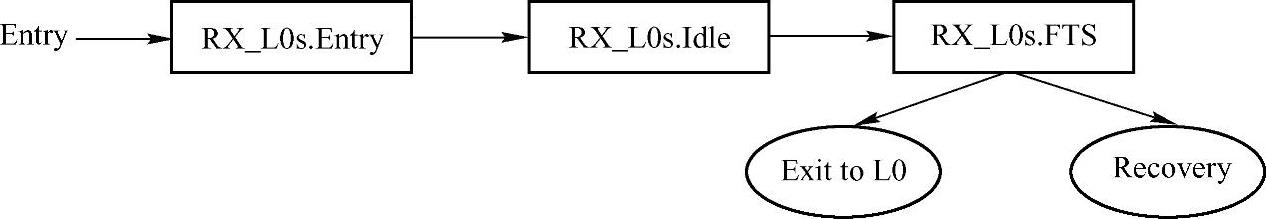

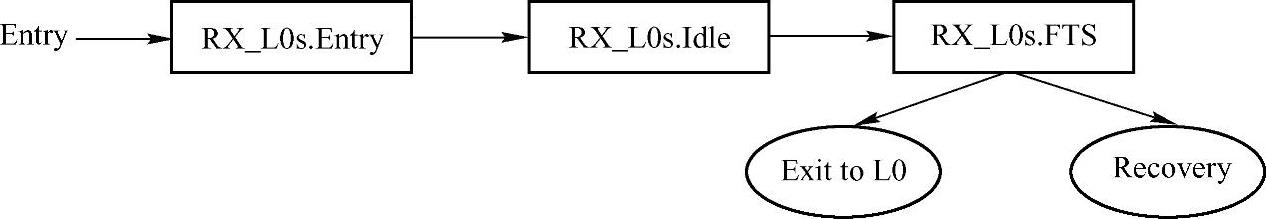

2.接收逻辑RX状态机(www.chuimin.cn)

L0s的接收状态机如图8-13所示,该状态机由Rx_L0s.Entry、Rx_L0s.Idle和Rx_L0s.FTS状态组成。PCIe设备可以从L0s状态进入L0或者Recovery状态。

图8-13 L0s的接收状态机

接收逻辑RX处于L0状态时,如果收到1个EIOS序列后,将进入Rx_L0s.Entry状态。接收逻辑RX在Rx_L0s.Entry状态经过一段延时[58]后,将进入Rx_L0s.Idle状态。

接收逻辑RX在Rx_L0s.Idle状态中将持续监测接收链路,如果发现对端设备的发送逻辑TX退出“Electrical Idle”状态时,接收逻辑RX将进入Rx_L0s.FTS状态。

当接收逻辑RX处于Rx_L0s.FTS状态时,PCIe链路的每一个Lane都将收到N_FTS个FTS序列,接收逻辑RX使用这些FTS序列重新获得Bit/Symbol Lock。如果对端发送逻辑TX发送的FTS序列不足,接收逻辑RX将无法成功获得Bit/Symbol Lock,此时PCIe设备将进入Recovery状态。

当接收逻辑RX收到足够数量的FTS序列,又收到了一个SKP序列后(该SKP序列的作用是De-Skew),将从Rx_L0s.FTS状态迁移到L0状态。

相关推荐