【摘要】:PCIe设备处于Polling.Active状态时,首先检查Link Control 2寄存器的“Enter Compli-ance Bit”位。本节对Polling.Compliance状态不做进一步描述。PCIe链路两端设备进入的LTSSM状态机并不一定同步,可能对端PCIe设备可能已经进入了Polling.Configuration状态,此时该设备将向对端发送TS2序列,详见下文。如果这些条件同时成立时,PCIe设备也将进入Polling.Configuration状态。如果PCIe链路上任何一个Lane的发送链路上连接了一个“对地阻抗为50Ω”的电阻后,PCIe设备也将强制进入Polling.Compliance状态。在许多PCIe设备的具体实现中,并没有使用Polling.Speed子状态。

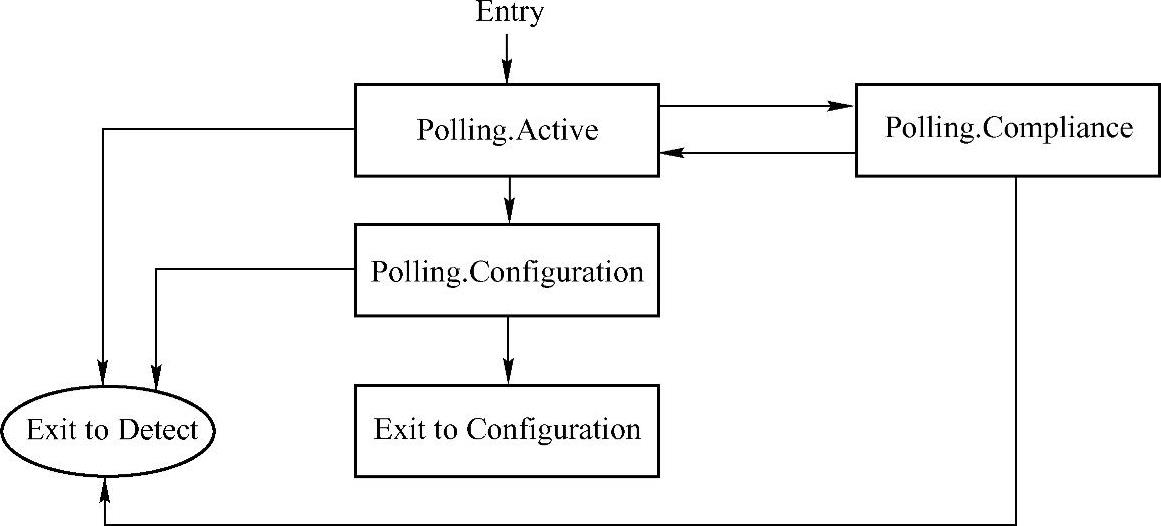

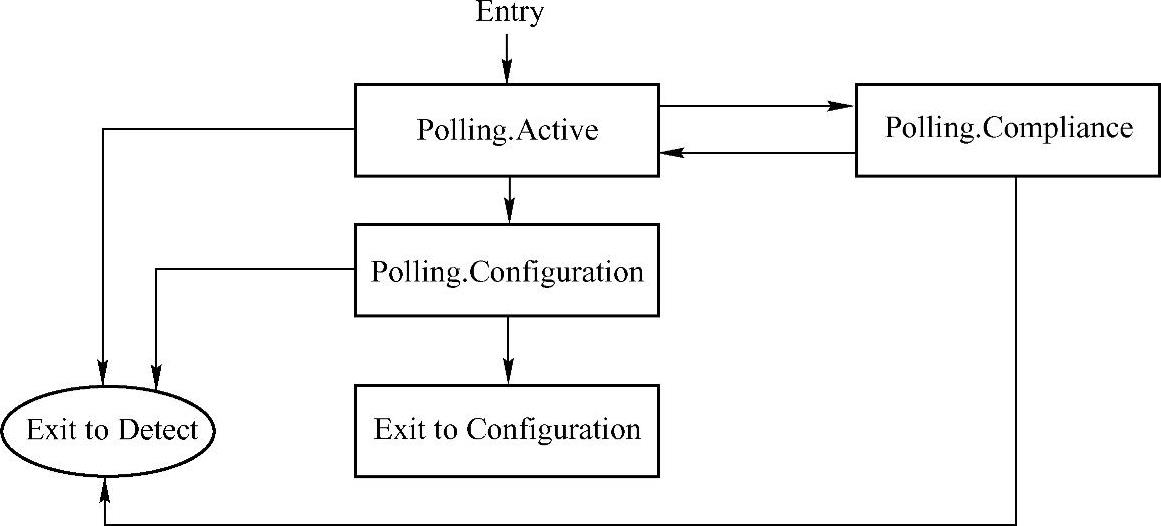

当PCIe设备在Detect状态中,识别完毕当前链路上可用的Lane资源之后,将进入Pol-ling状态,Polling状态由Polling.Active、Polling.Compliance和Polling.Configuration子状态组成。PCIe设备可以从Polling状态进入到Configuration状态,继续进行链路训练,如果PCIe设备在Polling状态中出现某种错误时,将退回到Detect状态,重新进行PCIe链路的训练,Polling状态机的转换逻辑如图8-7所示。

如该图所示,PCIe设备将首先进入Polling.Active状态,然后进入Polling.Configuration状态,最后退出到Configuration状态。

PCIe设备处于Polling.Active状态时,首先检查Link Control 2寄存器的“Enter Compli-ance Bit”位。如果该位为1,PCIe设备将进入Polling.Compliance状态,值得注意的是,PCIe链路两端设备的“Enter Compliance Bit”需要被同时置1,即PCIe链路两端的设备需要同时进入到Polling.Compliance状态。本节对Polling.Compliance状态不做进一步描述。

图8-7 Polling状态机

如果“Enter Compliance Bit”不为1,则PCIe链路两端设备的发送逻辑TX需要向对端[43]至少发送1024个TS1序列,其中TS1序列的Lane/Link Number必须为“PAD”,即不设置Lane/Link Number。PCIe设备使用这些TS1序列,获得Bit/Symbol Lock,这个过程大约需要64μs。值得注意的是,PCIe链路两端设备退出Detect状态时,可能并不完全同步,因此两端设备交换TS1序列的过程也并不完全同步。

发送逻辑TX在发送TS1序列之前,需要保证D+和D-信号的DC共模电压恢复到正常工作值。因为发送逻辑TX在Detect状态进行“Receiver Detect”的过程中,曾经将DC共模电压提高了VTX-RCV-DETECT。

PCIe设备在发送1024个TS1序列[44]的同时,如果其接收逻辑RX从全部“已被正确识别的Lane”中收到了以下任意一种8个连续的报文序列后,该PCIe设备将进入Pol-ling.Configuration状态。

(1)TS1序列[45],其Lane/Link Number为PAD,而“Compliance Receive”位为0。

(2)TS1序列,其Lane/Link Number为PAD,而“Loopback”位为1[46]。值得注意的是,发送逻辑TX发送“Loopback”位为1的TS1序列后,PCIe链路对端设备的接收逻辑RX将收到该序列,并将这个TS1序列使用内部Loopback逻辑直接回送给对端设备(并不是该设备重新生成的TS1序列),之后对端设备的接收逻辑RX将接收到之前发送逻辑TX发送的TS1序列。

(3)TS2序列,其Lane/Link Number为PAD。PCIe链路两端设备进入的LTSSM状态机并不一定同步,可能对端PCIe设备可能已经进入了Polling.Configuration状态,此时该设备将向对端发送TS2序列,详见下文。

如果上述条件没有成立,PCIe设备在经过20ms延时后,判断下列条件。如果这些条件同时成立时,PCIe设备也将进入Polling.Configuration状态。(www.chuimin.cn)

(1)任何一个“已被正确识别的Lane”收到了8个连续的TS1序列,其中Lane/Link Number为PAD,而“Compliance Receive”位为0或者“Loopback”位为1;或者收到8个连续的TS2序列。而且在收到第一个TS1序列之前,发送逻辑TX至少已经发送出1024个TS1序列。

(2)PCIe设备从Electrical Idle状态中退出,并进入到Polling.Active状态时,所有“已被正确识别的Lane”至少有一个Lane检测到对端设备。

如果该条件也没有成立,PCIe设备将可能进入Polling.Compliance状态。如果PCIe链路上任何一个Lane的发送链路上连接了一个“对地阻抗为50Ω”的电阻后,PCIe设备也将强制进入Polling.Compliance状态。该状态的主要作用是对PCIe链路进行检测,本节对此不做进一步描述。

当PCIe设备进入Polling.Configuration状态时,物理层首先处理所有“已识别的”Lane中,是否存在极性翻转(Lane Polarity Inversion)的现象,之后进行以下操作。

(1)置Link Control 2寄存器的“Transmit Margin”字段为0b000。

(2)向对端“已识别的Lane”连续发送TS2序列,其中Link/Lane Number为PAD,而Loopback位为0。

(3)当收到8个连续的TS2序列,而且一共收到16个TS2序列后,PCIe设备将进入Configuration状态,否则经过48ms延时后进入Detect状态。

当PCIe链路两端设备收齐TS2序列后,将基本同步地进入Configuration状态。从这个角度来说,TS2序列是为了同步“异步发送的TS1序列”。

在Polling状态机中,还有一个Polling.Speed子状态,该状态的主要作用是调整PCIe链路使用的数据传送率。当一个PCIe链路两端的设备可以支持高于2.5GT/s的数据传送率时,可以首先进入该状态,改变PCIe链路的数据传送率。

在许多PCIe设备的具体实现中,并没有使用Polling.Speed子状态。此时在PCIe链路的训练过程中,将缺省使用2.5GT/s的数据传送率。此时LTSSM状态机将首先沿着Detect→Polling→Configuration→L0的路径进入L0状态,并使用2.5GT/s的数据传送率,即便PCIe链路两端的设备都支持更高的数据传送率。

当PCIe设备改变数据传送率时,需要在L0状态,通过向对端设备发送TS1序列(其speed_change位为1),使PCIe链路两端设备进入Recovery状态后,才能改变缺省使用的数据传送率。

相关推荐