PCIe总线进行链路训练的主要目的是初始化PCIe链路的物理层、端口配置信息、相应的链路状态,并了解链路对端的拓扑结构,以便PCIe链路两端的设备进行数据通信。此时该PCIe设备在进行链路训练时,必须通知对端链路该设备实际使用的链路状态。此外PCIe总线在链路训练过程中,还需要确定数据传送率。PCIe总线进行链路训练时,需要进行RC或者Switch的Link Number和Lane Number的初始化,在第8.2节中将详细介绍这些内容。......

2023-10-20

PCIe总线进行链路训练时,需要发送一些特殊的字符序列(Ordered-Sets),这些Oder-er-Sets将在下文中详细介绍,PCIe总线规范定义了以下几类Ordered-Sets。有的书籍也将这些Order d-Sets称为PLP,即物理层报文。

●Training Sequence 1和2,简称为TS1和TS2序列。这两种PLP在链路训练的多个状态机中使用,下文将进一步介绍这两种字符序列。

●Idle序列。在正常情况下,发送端进入Electrical Idle状态时,将首先向对端发送若干Idle序列,才能进入。Electrical Idle状态是PCIe链路的一个低功耗状态,第8.1.2节将详细介绍该状态。

●Fast Training Sequence,简称为FTS。该字符序列协助接收逻辑获得Bit/Symbol Lock,接收逻辑需要获得多个FTS后,才能确定Bit/Symbol Lock。

●SKIP序列。该字符序列的主要作用是进行时钟补偿。

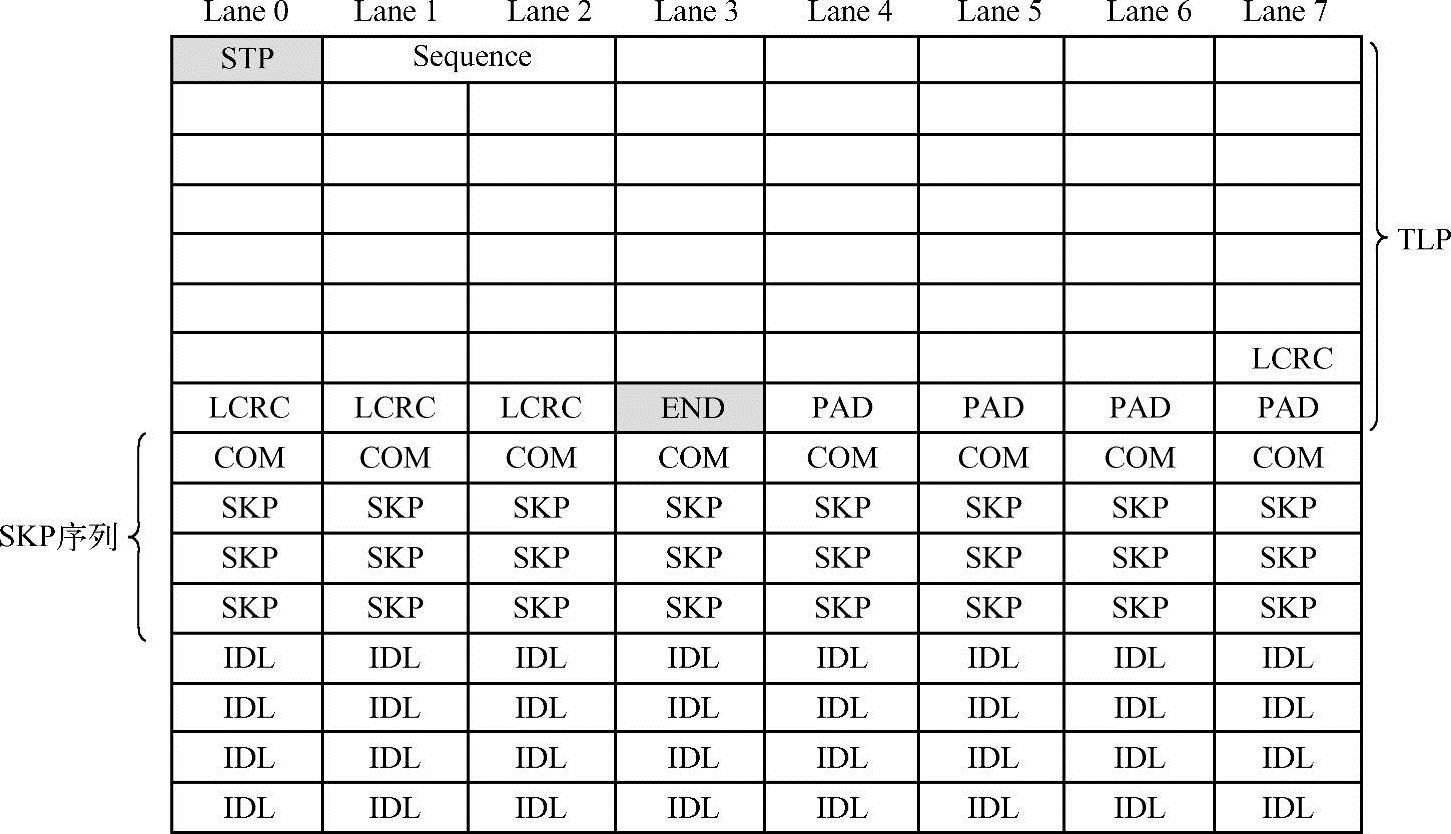

在PCIe总线中,字符序列的发送方式与TLP和DLLP有较大不同。假设一条PCIe链路由多个Lane组成,那么TLP和DLLP报文将分散到多个Lane中。而字符序列必须同时出现在这些不同的Lane,这几个Lane必须“在同一个时间点”发送字符序列。而不能出现一个Lane正在发送这个字符序列进行与链路训练相关的操作,而其他Lane进行其他数据传递的情况。PCIe链路发送TLP与发送字符序列的过程如图8-3所示。

如在一个×4的PCIe链路中发送SKIP序列时,每一个Lane中都要出现“COM、SKP、SKP、SKP”这样的数据流。其他字符序列的发送方法也与此类似。而TLP或者DLLP的发送分散到各个Lane上。

图8-3 特殊字符序列的发送

1.TS1和TS2序列

在物理层的LTSSM状态机中,TS1和TS2序列的使用方法不同。其中TS1序列的主要作用是检测PCIe链路的配置信息,而TS2序列确认TS1序列的检测结果。

TS1和TS2序列由16个字符组成,单纯从结构上看,TS1和TS2仅仅是第6~15个字符的含义不同,但是这两个序列在LTSSM状态机中的使用方法不同。TS1的第6~15个字符为D10.2,而TS2的第6~15个字符为D5.2,其中D10.2和D5.2也是TS1和TS2的标识号。TS1和TS2序列的其他字符如下所示。

●第0字符为COM控制字符,表示TS1/TS2序列的开始。TS1/TS2字符序列将复位LF-SR寄存器。

●在链路训练的初始阶段,第1字符存放控制字符PAD,即为空。而在链路的配置阶段,该字符存放端口使用的Link Number。

●在链路训练的初始阶段,第2字符为控制字符PAD,即为空。而在链路的配置阶段,该字符存放端口使用的Lane Number。

●第3个字符为FTS序列的个数(N_FTS)。不同的PCIe链路需要使用不同数目FTS序列,才能使接收端的PLL锁定接收时钟。

●第4个字符存放当前PCIe设备支持的数据传送率,第1位为1表示支持2.5GT/s传送率;第2位为1表示支持5GT/s传送率;第3位为1表示支持8GT/s的数据传送率(在PCIe V3.0规范中使用);第4~5位保留;第6位是一个多功能位,当PCIe链路的没有配置成功时可以作为Notification位,也可以用作发送链路De-emphasis的使能位;第7位为speed_change位,当该位为1时,通知PCIe链路对端设备需要改变传送速率。

●第5个字符存放命令。第0位为“Hot Reset”,第1位为“Disable Link”,第2位为“Loopback”,第3位为“Disable Scrambling”,第4位为“Compliance Receive”。当接收逻辑RX收到TS1或者TS2序列后,将根据该字符的命令进行对应的操作。(www.chuimin.cn)

2.Idle序列

在正常情况下,当发送端进入Electrical Idle状态之前,必须向对端发送EIOS序列。如果PCIe设备使用2.5GT/s的传送率时,Idle序列由1个COM字符加3个IDL字符组成,即“COM IDL IDL IDL”;如果PCIe设备使用5GT/s的传送率时,Idle序列由两组这样的字符序列组成,即“COM IDL IDL IDL COM IDL IDL IDL”。Electrical Idle状态是一种特殊的Idle状态,处于该状态时,PCIe链路使用的功耗最低,该状态的详细解释见第8.1.2节。

当发送端退出IDLE状态时,必须向对端发送EIEOS序列。EIEOS序列仅在链路传送率大于2.5GT时使用,该序列由1个COM字符、14个EIE字符和D10.2(TS1识别符)组成。

PCIe设备可以根据链路的使用情况确定当前链路是否处于Electrical Idle状态,而不是必须收到Idle序列后进入该状态。如一个PCIe设备在很长一段时间没有收到流量控制报文或者链路处于Electrical Idle状态时,也可以推断出对端设备处于Idle状态。

3.FTS序列

单个FTS序列由1个COM字符加3个FTS字符组成,该序列的主要目的是使接收逻辑RX重新获得Bit/Symbol Lock。发送逻辑需要向对端发送多少个FTS序列由接收到的TS1/2序列决定,TS1/2序列的第3个字符为需要发送FTS序列的个数。

4.SKIP序列

SKIP序列由一个COM字符加3个SKP字符组成。物理层提供SKIP序列的主要原因是进行时钟补偿。假设一个PCIe设备使用的时钟频率为2.5GHz±300ppm,其中300ppm意味着这个时钟源每发出1百万个时钟可能产生300个时钟漂移,即每3333个时钟将可能产生一个时钟漂移。如果PCIe链路不使用SKIP序列,本地时钟与“从报文中提取”的时钟存在的漂移,可能导致数据传送失败。

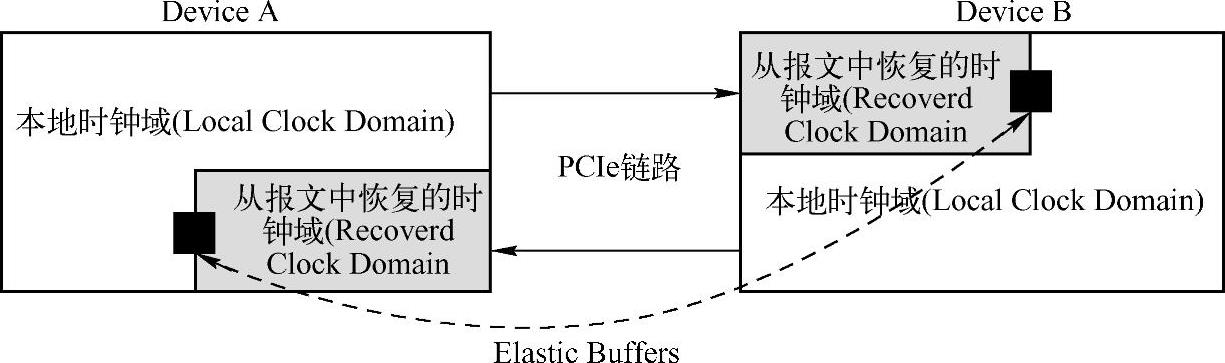

在PCIe设备的接收逻辑RX中,使用了两个时钟,一个时钟是通过PLL从接收报文中恢复的时钟,另一个时钟是接收逻辑RX使用的本地时钟。这两个时钟间的关系如图8-4所示。值得注意的是这两个时钟并不完全同步。

图8-4 本地时钟域与从报文中恢复的时钟域

在PCIe总线中,使用Elastic Buffer[37]技术处理这两个时钟之间的频率差和相位差。Elas-tic Buffer处于本地时钟域与“被恢复的”时钟域之间,由一个同步FIFO组成。该FIFO的一端使用本地时钟域、而另一端使用“被恢复的”时钟域。其中本地时钟与“被恢复的”时钟频率都为2.5GHz±300ppm。

但是如果PCIe设备从数据报文中恢复的时钟频率为2.5GHz-300ppm,而本地时钟频率为2.5GHz+300ppm时,Elastic Buffer两端的时钟频率并不匹配,Elastic Buffer将出现Over-run的现象;而如果本地时钟频率小于“被恢复的”时钟时,Elastic Buffer将可能出现Un-derrun的现象。如果PCIe总线不采取一些必要的补救措施,那么无论Elastic Buffer的容量有多么大,都可能出现Overrun和Underrun的现象。

为此,PCIe总线规定,物理层的每个Lane发送1180~1538个字符之后,必须发送一个SKIP序列进行时钟补偿。因为在最恶劣的情况下,接收逻辑RX每过1667个时钟周期,本地时钟就可能与“被恢复的”时钟相差一个时钟周期[38]。在PCIe总线中,当Elastic Buffer收到SKIP序列时,可以根据自身的状态选择是增加还是减少1~2个SKIP序列,从而补偿本地时钟与“被恢复的”时钟之间的频率与相位差。

在一个具体的实现中,可以通过计算,得到Elastic Buffer不出现Overrun和Underrun所需要的最小尺寸。这个最小尺寸与SKP序列的发送间隔(多少个时钟周期发送一次SKP序列),Max_Payload_Size参数和PCIe链路的数据传送率相关。对此有兴趣的读者可以参考Elastic Buffer Implementations in PCI Express Devices,以获得详细的量化分析结果,本节对此不做进一步说明。

Elastic Buffer技术由来已久,除了PCIe总线之外,USB总线、In finiBand、Fibre Channel和Gigabit Ethernet中也使用该技术处理分属不同时钟域的数据传递。

有关PCI Express体系结构导读的文章

PCIe总线进行链路训练的主要目的是初始化PCIe链路的物理层、端口配置信息、相应的链路状态,并了解链路对端的拓扑结构,以便PCIe链路两端的设备进行数据通信。此时该PCIe设备在进行链路训练时,必须通知对端链路该设备实际使用的链路状态。此外PCIe总线在链路训练过程中,还需要确定数据传送率。PCIe总线进行链路训练时,需要进行RC或者Switch的Link Number和Lane Number的初始化,在第8.2节中将详细介绍这些内容。......

2023-10-20

PCIe总线的序基于PCI总线的序,并进行了许多扩展。在TLP的Attr字段中有一个Relaxed Ordering位,表示该TLP是否支持PCIe总线的Re-laxed Ordering方式,但是TLP是否可以使用Relaxed Ordering还与这个TLP经过的设备有关。目前大多数PCIe设备不支持Relaxed ordering方式进行TLP的传递。在PCIe总线中,所有数据传送类型,如存储器、I/O、配置和Message总线事务都需要遵循规定的传送顺序。......

2023-10-20

PCIe设备使用MSI机制时,通过向中断控制器发送MSI报文以提交中断请求。然而对于PCIe体系结构而言,这个MSI报文与普通的存储器写报文并没有本质的区别,这个报文也可以使用不同的TC。如果设备的数据传送使用TC0,而MSI报文使用TC1时,将可能引发数据完整性的问题。PCIe总线规范并没有约定如何处理传递MSI报文而产生的数据完整性问题。当该读操作结束后,即PCIe设备收到存储器读完成TLP后,再发送MSI报文。......

2023-10-20

PCIe总线定义了一系列与电源管理相关的链路状态。PCIe设备仅使用辅助电源工作,主电源已经被关闭。该状态是一个“伪”状态,PCIe链路处于L2、L3状态时,需要通过LDn状态之后才能进入L0状态。图8-11 电源管理状态机本节重点说明L0、L0s和L1状态的工作原理以及如何使用ASPM机制进行状态迁移。在第8.4节将讲述系统软件如何设置寄存器使PCIe设备进入L0、L0s和L1状态。在PCIe设备中,Link Capabilities寄存器的ASPM Support字段表示当前PCIe设备可以支持的链路状态,该字段只读。......

2023-10-20

PCI总线作为处理器系统的局部总线,其主要目的是为了连接外部设备,而不是作为处理器的系统总线连接Cache和主存储器。孤立地研究PCI总线并不可取,因为PCI总线仅是处理器系统的一个部分。深入理解PCI总线需要了解一些与处理器体系结构相关的知识。PCI规范并没有对HOST主桥的设计进行约束。PCI桥是PCI总线的一个重要组成部件,该部件的存在使得PCI总线极具扩展性。PCI总线提供的峰值带宽远高于这些总线。......

2023-10-20

PPP 协议在进行数据通信前需要建立一条PPP 链路。PPP 协议的起始和终止状态称为链路静止状态,此时,用户PC 和ISP 的路由器之间不存在物理连接。图3.5PPP 协议链路状态转换在建立链路后链路打开前,PPP 协议所进行身份验证(鉴别)中主要支持两种验证协议:密码验证协议和质询-握手验证协议。CHAP 针对PAP 的不安全性进行了改进,使用三次握手验证。除了IP 协议以外,PPP 协议还可以携带其他协议。......

2023-10-19

图12-1 Capric卡的组成结构Capric卡基于PCIe总线,主要功能是通过DMA读写方式与HOST处理器进行数据交换。Capric卡由LogiCORE、发送部件、接收部件、BAR空间、DMA控制逻辑和FPGA片内SRAM组成,其工作原理较为简单。Capric卡仅使用了BAR0空间,处理器使用存储器映像寻址方式,而不是I/O映像寻址方式访问BAR0空间。......

2023-10-20

PCI Express Extended Capabilities结构存放在PCI配置空间0x100之后的位置,该结构是PCIe设备独有的,PCI设备并不支持该结构。在一个PCIe设备中可能含有多个PCI Express Extended Capabilities结构,并形成一个单向链表,其中第一个Capability结构的基地址为0x100,其结构如图4-19所示。图4-19 PCI Express Extended Capabilities结构一个PCI Express Extended Capabilities结构由以下参数组成。但是在PCIe总线中,这些扩展的Capability结构并没有得到充分利用。本节仅详细介绍PCI Express Extended Capabilities结构组中的MFVC结构。......

2023-10-20

相关推荐