ICMP请求与应答报文可以由源主机主动发出请求报文,为了响应请求,ICMP软件需要发送一个ICMP应答报文。图8-11 回送请求与应答ICMP报文格式回送请求ICMP报文的类型字段为8,应答ICMP报文类型为0,代码字段都为0。一台主机可以同时向多台目的主机发送ICMP请求报文,不同的请求报文标识符和序号不同。......

2023-11-20

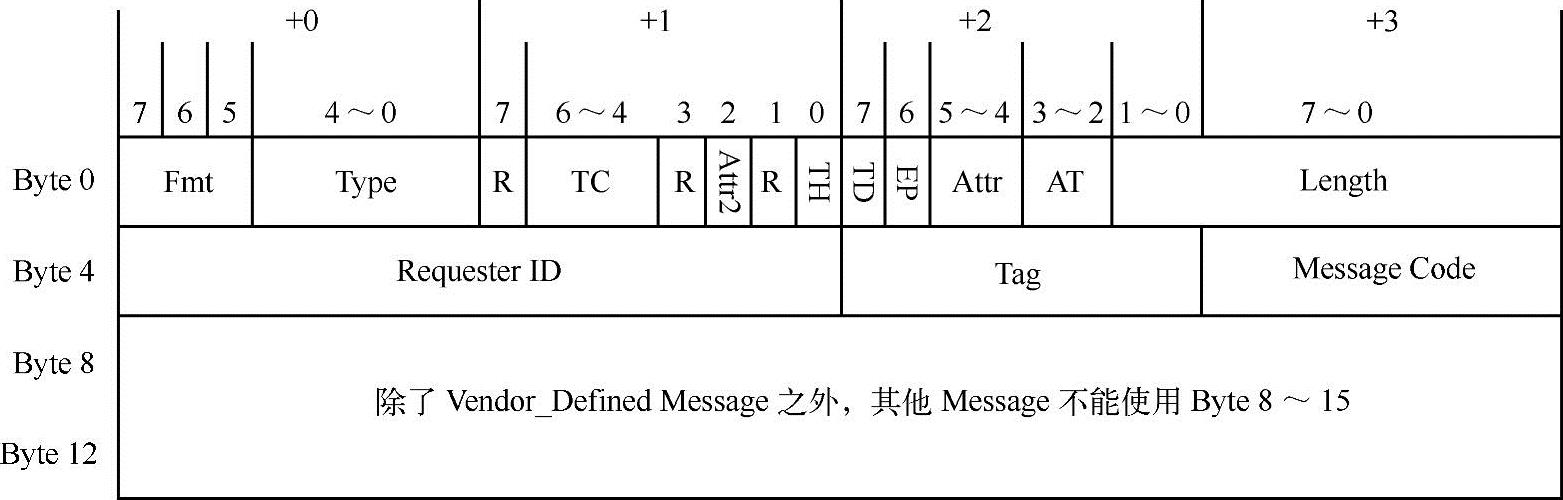

在PCIe总线中,多数消息报文使用隐式路由方式,其格式如图6-13所示。其中Byte 0字段为通用TLP头,而Byte 4的第3字节中存放Message Code字段。

图6-13 Message请求TLP头格式

PCIe总线规定了以下几类消息报文。

●INTx中断消息报文(INTx Interrupt Signaling)。

●电源管理消息报文(Power Management)。

●错误消息报文(Error Signaling)。

●锁定事务消息报文(Locked Transaction Support)。

●插槽电源限制消息报文(Slot Power Limit Support)。

●Vendor-Defined Messages。

本节将重点讲述INTx中断和错误信息相关的消息报文,请读者阅读PCIe总线规范了解其他消息报文。

1.INTx中断消息报文

PCIe总线推荐设备使用MSI或者MSI-X机制提交中断请求,但是MSI中断机制并不是由PCIe总线首先提出的,在PCI总线中就已经存在这种中断请求机制。

在PCI总线中,虽然提出了MSI中断机制,但是几乎没有PCI设备使用这种机制进行中断请求。MSI中断机制是一种基于存储器写的中断请求机制,而PCI设备提交MSI中断请求,将占用PCI总线的带宽,因此多数PCI设备使用INTx信号进行中断请求。(www.chuimin.cn)

在PCIe总线中,PCIe设备可以使用Legacy中断方式提交中断请求,此时需要使用INTx中断消息报文向RC通知中断事件。除此之外在PCIe体系结构中仍然存在PCI设备,这些设备可能使用INTx信号提交中断请求。

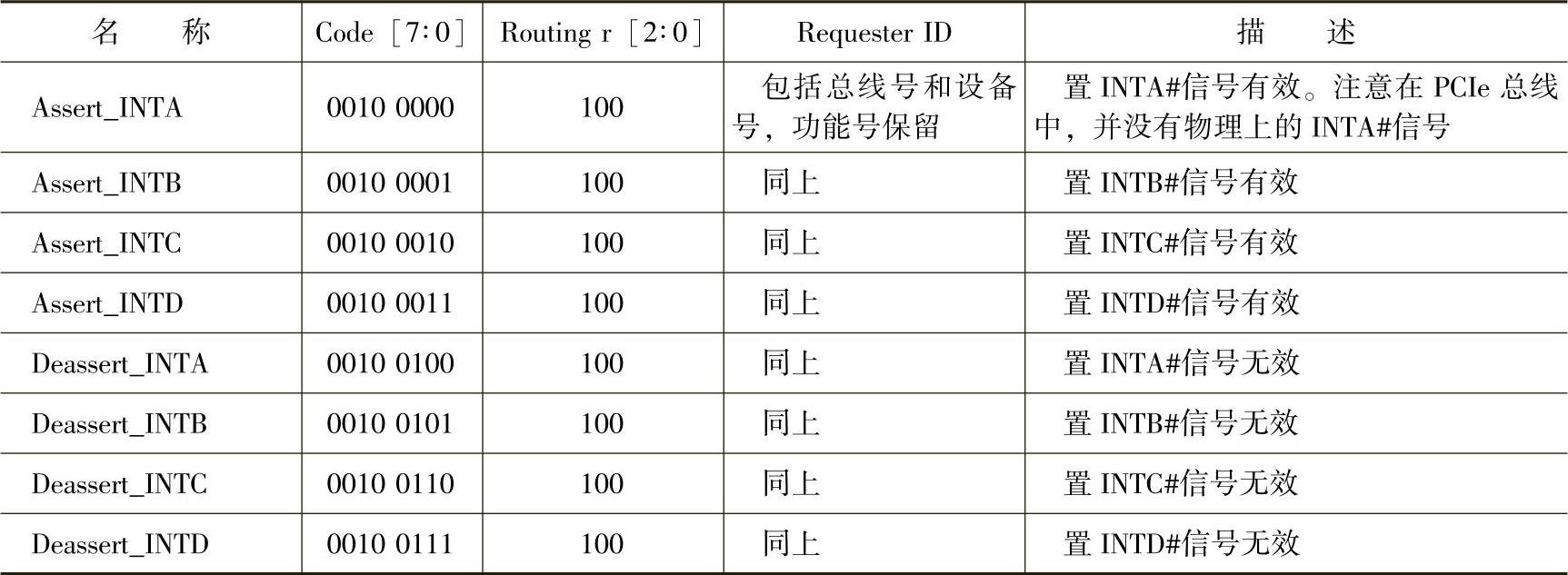

例如在PCIe桥片上挂接的PCI设备可能并不支持MSI中断机制,因此需要使用INTx中断信号提交中断请求,此时PCIe桥需要将INTx信号转换为INTx中断消息报文,并向RC提交中断请求。在PCIe总线中,共有8种INTx中断消息报文,见表6-7。

表6-7 INTx中断消息报文

当PCIe设备不使用MSI报文向RC提交中断请求时,可以首先使用Assert_INTx报文向处理器系统提交中断请求,当中断处理完毕,再使用Deassert_INTx报文。这些INTx中断消息报文的r[2∶0]字段为0b100,即为Local消息报文。设备收到该消息报文后,将结束收到的INTx中断消息报文,然后产生一个新的INTx中断消息报文。

在一个处理器系统中,PCI设备首先需要通过PCIe桥,之后可能通过多级Switch,最终到达RC。假设PCI设备使用INTA#信号进行中断请求,但是由于中断路由表的存在,PCIe桥可能将INTA#信号转换为INTB中断消息,而这个INTB中断消息通过Switch时,可能又被Switch的中断路由表转换为INTC中断消息。因此PCIe设备收到INTx中断消息后,首先需要结束当前中断消息,之后根据中断路由表产生一个新的INTx中断消息,直到这个中断消息传递到RC。

2.错误消息报文

在第4.3.3节中简要介绍了AER Capability结构。如果PCIe设备支持AER Capability结构,当PCIe设备出现某种错误时,将向RC或者RC Event Collector发送错误消息报文,之后RC或者RC Event Collector将根据错误类型分别进行处理。

PCIe总线规范定义了两大类错误类型,分别是可恢复错误(Correctable Errors)和不可恢复错误(Uncorre ctable Errors),不可恢复错误又细分为致命错误(Fatal)和非致命错误(Nonfatal)。当PCIe设备出现这些错误时,将使用ERR_COR、ERR_NONFATAL和ERR_FA-TAL错误消息报文向RC或者RC Event Collector发送错误消息报文。

PCIe总线规范并没有详细描述“可恢复错误”和“不可恢复错误”的具体处理方法,也没有详细描述PCIe设备的错误恢复机制。对于PCIe设备,这些处理方法并不重要。PCIe总线定义AER机制的主要考虑是,由PCIe设备将错误信息“统一报告”给RC或者RC E-vent Collector,并由RC或者RC Event Collector“统一处理”这些错误。其中“统一报告”和“统一处理”才是AER机制的设计要点。

当PCIe设备出现某种错误后,首先将这些错误信息保留在设备的AER Capability结构中,之后RC或者RC Event Collector从“来自PCIe设备的错误信息报文”中获得相应的错误信息。为此在RC中设置了一个“Error Source Identification”寄存器保存究竟是哪个PCIe设备发出的错误信息报文,之后RC或者RC Event Collector向处理器系统提交中断请求,由相应的中断服务例程统一处理所有PCIe设备的错误信息。

由RC统一处理所有PCIe设备错误信息的这种做法,势必加大RC和系统软件的设计复杂度。而外部设备的多样性与复杂程度决定了使用这种方法不一定能够取得较好的效果。目前Intel的Chipset已经支持AER机制,但是绝大多数PCIe设备并不支持AER机制。AER机制是Intel统一外部设备错误处理的一种方法,这为PCIe设备的设计提出了更高的要求,而这种方法是否能够取得理想的效果,仍需观察。

有关PCI Express体系结构导读的文章

ICMP请求与应答报文可以由源主机主动发出请求报文,为了响应请求,ICMP软件需要发送一个ICMP应答报文。图8-11 回送请求与应答ICMP报文格式回送请求ICMP报文的类型字段为8,应答ICMP报文类型为0,代码字段都为0。一台主机可以同时向多台目的主机发送ICMP请求报文,不同的请求报文标识符和序号不同。......

2023-11-20

PCIe设备使用MSI机制时,通过向中断控制器发送MSI报文以提交中断请求。然而对于PCIe体系结构而言,这个MSI报文与普通的存储器写报文并没有本质的区别,这个报文也可以使用不同的TC。如果设备的数据传送使用TC0,而MSI报文使用TC1时,将可能引发数据完整性的问题。PCIe总线规范并没有约定如何处理传递MSI报文而产生的数据完整性问题。当该读操作结束后,即PCIe设备收到存储器读完成TLP后,再发送MSI报文。......

2023-10-20

在PCIe总线中,一个地址转换关系由8B组成,这也是地址转换请求TLP的Length字段至少为0b10的原因。当TA收到地址转换请求TLP后,将查找ATPT,然后通过存储器读完成TLP,将转换关系发送给PCIe设备。采用这种方式时,PCIe设备将首先向TA发送地址转换请求TLP,并从ATPT中获得地址转换关系后,使用TA等于0b10的存储器读写TLP,即使用Translated Address与主存储器进行数据交换,从而有效避免了上文所述的安全隐患。......

2023-10-20

PCI总线提供了INTA#、INTB#、INTC#和INTD#四个中断请求信号,PCI设备借助这些中断请求信号,使用电平触发方式向处理器提交中断请求。PCI设备的这些中断请求信号可以通过某种规则进行线与,之后与中断控制器的中断请求信号线相连。而处理器系统需要预先知道这个规则,以便正确处理来自不同PCI设备的中断请求,这个规则也被称为中断路由表,有关中断路由表的详细描述见第1.4.2节。......

2023-10-20

在一些具有自绘属性的列表类控件添加列表项时,产生WM_MEASUREITEM消息回调。在消息回调函数OnMeasureItem中,执行基类函数CWnd::OnMeasureItem将回调路由,进入每个自绘子窗口关联的派生类的虚函数MeasureItem中。使用MFC应用程序向导创建一个工程名为“dr”的对话框程序,用于演示WM_DRAWITEM和WM_MEASUREITEM消息的使用方法。9)在主对话框中,添加WM_DRAWITEM和WM_MEASUREITEM消息映射函数,如图10-46所示。11)修改WM_DRAWITEM消息映射函数代码。WM_MEASUREITEM和WM_DRAWITEM消息,能够在父窗口中提前截获所有子窗口的自绘和测量消息回调。......

2023-11-25

存储器读写请求TLP的格式如图6-8所示。在存储器读写和I/O读写请求的第3和第4个双字中,存放TLP的32或者64位地址。存储器、I/O和原子操作读写请求使用的TLP头较为类似。此时与这个存储器读请求TLP对应的读完成TLP中不包含有效数据。......

2023-10-20

为了实现长报文的传输,BACnet采取了应用层报文分段的机制来对报文进行分段。在BAC-net中只有有证实请求和复杂确认报文可能需要分段。APDU最大长度的确定在BACnet报文中,APDU的最大长度不是固定的,其具体值是下列各长度值中的最小值:1)设备所能发送的APDU的最大长度。......

2023-08-29

PCI设备保证在数据到达目的地之后,再提交中断请求。但是使用MSI中断机制可以取消PCI总线这个INTx#边带信号,可以解决使用INTx中断机制所带来的数据完整性问题。而更为重要的是,PCI设备使用MSI中断机制,向处理器系统提交中断请求时,还可以通知处理器系统产生该中断的原因,即通过不同中断向量号表示中断请求的来源。本书将在第10章详细介绍MSI中断机制。......

2023-10-20

相关推荐