事务层是PCIe总线层次结构的最高层,该层次将接收PCIe设备核心层的数据请求,并将其转换为PCIe总线事务,PCIe总线使用的这些总线事务在TLP头中定义。PCIe的事务层还支持流量控制和虚通路管理等一系列特性,而PCI总线并不支持这些新的特性。在PCIe总线中,不同的总线事务采用的路由方式不相同。PCIe总线使用的数据报文首先在事务层中形成,这个数据报文也称为事务层数据报文,即TLP。......

2025-09-30

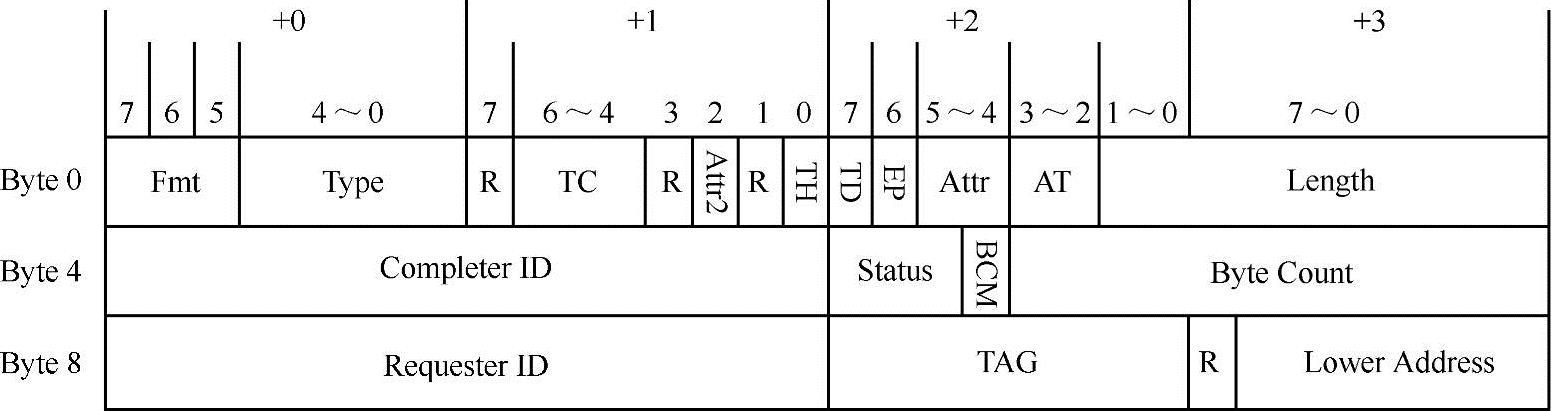

PCIe总线支持Split传送方式,目标设备使用完成报文向源设备主动发送数据。完成报文使用ID路由方式,由TLP Predix、报文头和Data Payload组成,但是某些完成报文可以不含有Data Payload,如I/O或者配置写完成和Zero-Length读完成报文。在PCIe总线中,有以下几类数据请求需要收到完成报文之后,才能完成整个数据传送过程,完成报文格式如图6-11所示。

●所有的数据读请求,包括存储器、I/O读请求、配置读请求和原子操作请求。当一个PCIe设备发出这些数据请求报文后,必须收到目标设备的完成报文后,才能结束一次数据传送。这一类完成报文必须包含Data Payload。

●所有的Non-Posted数据写请求,包括I/O和配置写请求。当一个PCIe设备发出这些数据请求报文后,必须收到目标设备的完成报文后,才能结束数据传送。但是这一类完成报文不包含数据,仅包含应答信息。

●与ATS机制相关的一些报文,详见第13.2节。

图6-11 完成报文头格式

完成报文“Byte 0”中的大部分字段与“存储器,I/O、配置请求报文”的对应字段的含义相同。完成报文一次最多能够传送的报文大小不能超过Max_Payload_Size参数。在多数处理器中,完成报文中包含的数据在一个Cache行之内,完成报文使用RCB参数来处理数据对界,RCB参数的大小与处理器系统的Cache行长度和DDR-SDRAM的一次突发传送长度相关,这些参数的详细描述见第6.4.3节。在x86和PowerPC处理器中,一个存储器读完成报文一般不超过RCB参数。

1.Requester ID和Tag字段

完成报文使用ID路由方式,ID路由方式详见第6.2.2节。完成报文头的长度为3DW,完成报文头中包含Transaction ID信息,由Requester ID和Tag字段组成,这个ID必须与源设备发送的数据请求报文的Transaction ID对应,完成报文使用Transaction ID进行ID路由,并将数据发送给源设备。

当PCIe设备收到存储器读、I/O读写或者配置读写请求TLP时,需要首先保存这些报文的Transaction ID,之后当该设备准备好完成报文后,将完成报文的Requester ID和Tag字段赋值为之前保存的Transaction ID字段。

2.Completer ID字段

Completer ID字段的含义与Requester ID字段较为相似,只是该字段存放“发送完成报文”的PCIe设备的ID号。PCIe设备进行数据请求时需要在TLP字段中包含Requester ID字段;而使用完成报文结束数据请求时,需要提供Completer ID字段。

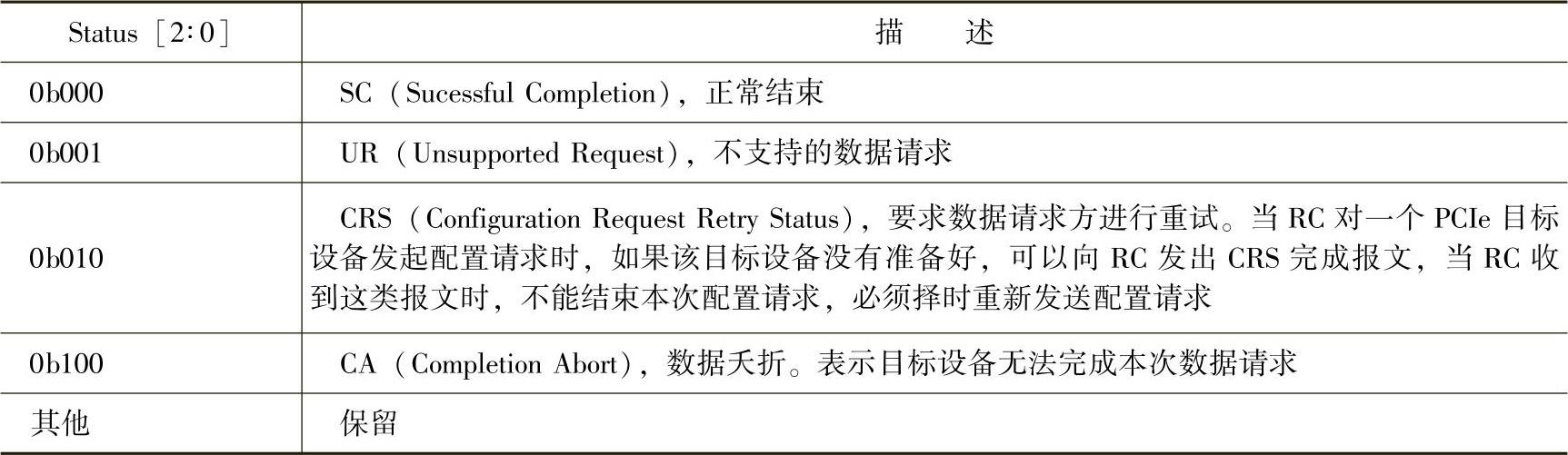

3.Status字段(https://www.chuimin.cn)

Status字段保存当前完成报文的完成状态,表示当前TLP是正确地将数据传递给数据请求端;还是在数据传递过程中出现错误;或者要求数据请求方进行重试。PCIe总线规定了几类完成状态,如表6-6所示。

表6-6 Status字段

4.BCM位与Byte Count字段

BCM(Byte Count Modified)字段由PCI-X设备设置。PCI-X设备也支持Split Trans-action传送方式,当PCI-X设备进行存储器读请求时,目标设备不一定一次就能将所有数据传递给源设备。此时目标设备在进行第一次数据传送时,需要设置Byte Count字段和BCM位。

BCM位表示Byte Count字段是否被更改,该位仅对PCI-X设备有效,而PCIe设备不能操纵BCM位,只有PCI-X设备或者PCIe-to-PCI-X桥可以改变该位。本节对此位不做进一步介绍,对此位感兴趣的读者可以参考PCI-X Addendum to the PCI Local Bus Specification,Revi-sion 2.0。

Byte Count字段记录源设备还需要从目标设备中获得多少字节的数据就能完成全部数据传递,当前TLP中的有效负载也被Byte Count字段统计在内。该字段由12位组成。该字段为0b0000-0000-0001表示还剩一个字节,为0b1111-1111-1111表示还剩4095个字节,而为0b0000-0000-0000表示还剩4096个字节。除了存储器读请求的完成报文外,大多数完成报文的Byte Count字段为4。

如一个源设备向目标设备发送一个“读取128B的存储器读请求TLP”,而目标设备收到这个读请求TLP后,可能使用两个存储器读完成TLP传递数据。其中第1个存储器读完成TLP的有效数据为64B,而Byte Count字段为128;第2个存储器读完成TLP中的有效数据为64B,而Byte Count字段也为64。当数据请求端接收完毕第1个存储器读完成TLP后,发现还有64B的数据没有接收完毕,此时必须等待下一个存储器读完成TLP。等到数据请求端收齐所有数据后,才能结束整个存储器读请求。

目标设备发出的第2个读完成TLP中的有效数据为64B,而Byte Count字段为64,当数据请求端接收完毕这个读完成TLP后,将完成一个完整的存储器读过程,从而可以释放这个存储器读过程使用的Tag资源。

存储器读请求的完成报文的拆分方式较为复杂,Byte Count字段的设置也相对较为复杂。在第12章将结合一个实例讲述该字段的使用方法。

5.Lower Address字段

如果当前完成报文为存储器读完成TLP,该字段存放在存储器读完成TLP中第一个数据所对应地址的最低位。值得注意的是,在完成报文中,并不存在First DW BE和Last DW BE字段,因此接收端必须使用存储器读完成TLP的Low Address字段,识别一个TLP中包含数据的起始地址。第12.2.2节将详细介绍该字段的作用。

相关文章

事务层是PCIe总线层次结构的最高层,该层次将接收PCIe设备核心层的数据请求,并将其转换为PCIe总线事务,PCIe总线使用的这些总线事务在TLP头中定义。PCIe的事务层还支持流量控制和虚通路管理等一系列特性,而PCI总线并不支持这些新的特性。在PCIe总线中,不同的总线事务采用的路由方式不相同。PCIe总线使用的数据报文首先在事务层中形成,这个数据报文也称为事务层数据报文,即TLP。......

2025-09-30

PCI总线0上存储器控制器是一个比较特殊的PCI设备,这个设备除了需要管理DDR SDRAM之外,还管理整个存储器域的地址空间,包括PCI总线域地址空间。从传统外部设备的角度上看,PCI总线0的Device 0并不是一个设备,仅存放与处理器系统密切相关的一组参数。值得注意的是,在x86处理器中,PCI总线0的Device 0的存在并不完全是为了向前兼容,而是Intel使用PCI总线概念统一所有外部设备的方法。表5-1 Device 0的基本配置空间Device 0使用的基本配置空间与其他PCI设备兼容。......

2025-09-30

PCI-X总线改变了PCI总线使用的传送协议。PCI-X 1.0总线可以使用的最高总线频率为133MHz,而PCI-X 2.0总线可以使用的最高总线频率为533MHz,远比PCI总线使用的总线频率高。除了信号传送协议外,PCI-X总线在进行DMA读写时,可以不进行Cache共享一致性操作,而PCI总线进行DMA读写时必须进行Cache一致性操作。第3.3节将详细讨论与Cache一致性相关的PCI总线事务。此外PCI-X总线还支持乱序总线事务,即Relaxed Ordering,该总线事务被PCIe总线继承。......

2025-09-30

PCIe总线规定消息请求报文使用隐式路由方式。表6-4 Route[4∶0]字段使用隐式路由方式的TLP,其Route字段为“000”,“011”,“100”或者“101”。当一个报文使用隐式路由向EP发送时,EP将对Route字段进行检查,如果这个报文是“来自RC的广播报文”,或者是“本地报文”,EP将接收此报文。如果Switch收到一条使用隐式路由的TLP时,将根据报文Route字段的不同而分别处理。......

2025-09-30

为此PCI桥需要对Non-Posted总线事务进行优化处理,并使用Delayed总线事务处理这些Non-Posted总线事务,PCI总线规定只有Non-Posted总线事务可以使用Delayed总线事务。PCI总线的Delay总线事务由Delay读写请求和Delay读写完成总线事务组成,当Delay读写请求到达目的地后,将被转换为Delay读写完成总线事务。为了进一步提高Non-Posted总线事务的执行效率,PCI-X总线将PCI总线使用的Delayed总线事务,升级为Split总线事务。......

2025-09-30

如图9.50所示,OTN 传送网络从垂直方向分为三层,即光通道层网络、光复用段层网络和光传输段层网络。图9.51是光传送网的网络分层示例,用于表示光传送网提供端到端的连接。图9.51提供端到端连接的光传送网结构OTN 网络相邻层之间存在着客户/服务者关系,即每一层网络为相邻上一层网络提供传送服务,同时又使用相邻的下一层网络所提供的传送服务,具体如下。......

2025-09-29

数据跟踪传送(热备)功能用于使控制系统和待机系统的数据保持统一,以确保控制系统停机时,冗余系统通过待机系统继续运行。不进行跟踪传送(热备)的情况下,在系统切换后,在新的控制系统CPU模块中,会有上升沿、下降沿和SCJ指令不能正常工作的情况。图12-77 跟踪传送(热备)的步骤......

2025-09-29

表5-27 数据传送指令注:EDMOV指令仅适合QnU系列PLC。下面以16位数据传送指令MOV为例展开说明。图5-4 K155存储在数据寄存器D8中2)浮点数据传送EMOV指令是将源操作数中存储的浮点型实数数据传送至目标软元件中去。EMOV指令是单精度浮点数据,占32位,双精度指令占64位。4)相同16位数据批量传送指令FMOV的主要功能是将数据同时传送到指定软元件开始的n点位置。......

2025-09-29

相关推荐