而桥设备的主要作用是管理下游的PCI总线,并转发上下游总线之间的总线事务。PCI总线规范将PCI主从设备统称为PCI Agent设备。PCI规范也没有规定如何设计HOST主桥。在PCI总线中,还有一类特殊的设备,即桥设备。本书重点介绍PCI桥,而不介绍其他桥设备的实现原理。PCI桥的出现使得采用PCI总线进行大规模系统互连成为可能。其中对PCI设备配置空间的访问可以从上游总线转发到下游总线,而数据传送可以双方向进行。......

2023-10-20

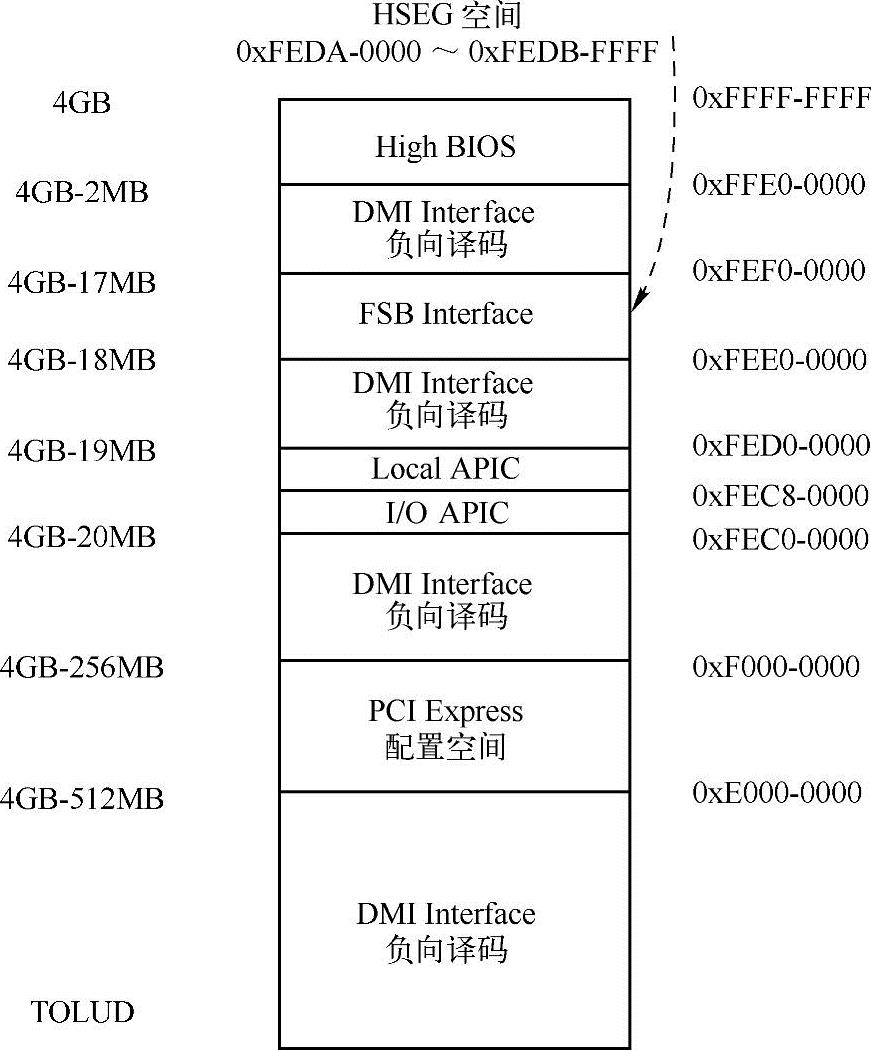

TOLUD~4GB这段PCI总线地址空间主要映射和ICH相连的PCI设备地址空间,此外还包括EPBAR(Egress Port Base Address)指向的空间,以及MCHBAR和DMIBAR指向的空间等。除了PCI总线地址空间外,这段空间还包括High BIOS、APIC(Advanced Programming Interrupt Controller)和FSB Interrupts地址空间,其详细描述如图5-4所示。

其中APIC(Advanced Programmable Interrupt Controller)包括I/O APIC和Local APIC占用0xFEC0-0000~0x FECF-FFFF这段地址空间。APIC是x86处理器使用的中断控制器,负责管理外部和CPU之间的中断请求。而HESG空间占用0xFEDA-0000~0xFEDB-FFFF这段地址空间,这段空间在CPU内核处于SMM状态时,才能访问。

FSB Interrupts存储器空间与MSI中断机制相关,PCIe设备向这段存储器空间进行写操作时,MCH将这个写操作转换为FSB总线的Interrupt Message总线事务。

值得注意的是,在x86处理器中Local APCI使用的寄存器在0xFEE0-0000~0xFEE0-03F0区域之间,在这段区域中,有一些Reserved寄存器,如0xFEE0-0000~0xFEE0-0010,系统软件不能操作这些寄存器。Intel并没有公开这些寄存器的具体含义,但是从原理上推断,这段寄存器所使用的地址正好是PCIe设备使用MSI-X中断方式向APCI ID为0的CPU发送中断所使用的地址,有关x86处理器MSI-X中断方式的详细说明见第10.3节。

(www.chuimin.cn)

(www.chuimin.cn)

图5-4 TOLUD~4GB PCI总线地址空间

在x86处理器中,Local APIC寄存器空间是可变的,其基地址保存在IA32_APIC_BASE寄存器中,该寄存器是x86处理器的MSR(Model Specific Register)寄存器,x86处理器使用RDMSR和WRMSR指令访问这些寄存器。

PCI Express配置空间占用0xE000-0000~0xEFFF-FFFF这段地址空间,下节将详细解释这段空间的使用方法。DMI Interface负向译码空间被分为若干段,用来映射ICH使用的PCI总线地址空间。在ICH中提供了许多PCI设备,包括内嵌在ICH中的虚拟PCI设备和PCIe总线端口。这些PCI设备的BAR空间被映射到这段空间。

Montevina平台使用DMI连接MCH和ICH。当CPU对PCI空间发起数据请求时,这些数据首先到达MCH,当MCH中的所有设备都不响应这个数据请求时,MCH中的DMI接口设备将使用负向译码方式被动地接收这个数据请求,并将其转发到ICH中的DMI接口设备,从而到达ICH。因此Montevina平台将这段空间称为“负向译码空间”。由以上说明可以发现与MCH连接的PCIe设备的访问延时小于与ICH连接中的PCIe设备。

有关PCI Express体系结构导读的文章

而桥设备的主要作用是管理下游的PCI总线,并转发上下游总线之间的总线事务。PCI总线规范将PCI主从设备统称为PCI Agent设备。PCI规范也没有规定如何设计HOST主桥。在PCI总线中,还有一类特殊的设备,即桥设备。本书重点介绍PCI桥,而不介绍其他桥设备的实现原理。PCI桥的出现使得采用PCI总线进行大规模系统互连成为可能。其中对PCI设备配置空间的访问可以从上游总线转发到下游总线,而数据传送可以双方向进行。......

2023-10-20

而这个PCI桥的Secondary Bus在接收Dock设备的请求时仍然使用正向译码方式。PCI桥使用的正向译码方式与PCI设备使用的正向译码方式有所不同。值得注意的是,PCI总线并没有规定HOST主桥使用正向还是负向译码方式接收这个存储器读写总线事务,但是绝大多数HOST主桥使用正向译码方式接收来自下游的存储器读写总线事务。......

2023-10-20

最后这段程序使用acpi_pci_irq_enable函数为当前PCI总线树上的所有PCI设备分配irq号。pcibios_init→pcibios_resource_survey函数将检查当前处理器系统的所有PCI设备的BAR空间,该函数并不会操作PCI设备的BAR寄存器,而只是检查当前处理器系统中所有PCI设备的pci_dev→resource参数是否合法。源代码14-36 pci_find_parent_resource函数pci_find_parent_resource首先对PCI桥管理的地址空间进行检查。pcibios_init函数主要操作Linux系统中的数据结构,并没有对PCI设备的BAR寄存器进行读写操作。......

2023-10-20

系统软件使用CFG_ADDR和CFG_DATA寄存器访问PCI设备的配置空间,而使用INT_ACK寄存器访问挂接在PCI总线上的中断控制器的中断向量,HOST主桥这3个寄存器的地址偏移和属性如表2-1所示。当该位为1时,HOST主桥使能对PCI设备配置空间的访问,当HOST处理器对CFG_DATA寄存器进行访问时,HOST主桥将对这个寄存器的访问转换为PCI配置读写总线事务并发送到PCI总线上。下面以源代码2-1为例说明PowerPC处理器如何访问PCI配置空间。......

2023-10-20

系统软件使用DFS算法对PCI总线进行遍历时,完成这些寄存器的初始化,即分配这些设备在PCI总线域的地址空间。值得注意的是,PCI Agent设备的BAR0~5寄存器和PCI桥的Base寄存器保存的地址都是PCI总线地址。而这些地址在处理器系统的存储器域中具有映像,如果一个PCI设备的BAR空间在存储器域中没有映像,处理器将不能访问该PCI设备的BAR空间。......

2023-10-20

在Linux系统中,PCI设备使用的irq号存放在pdev→irq参数中,该参数在Linux设备驱动程序进行初始化时,由pci_enable_device函数设置。本书在第12.3.2节曾简要介绍过这个函数,下文进一步说明如何使用该函数设置PCI设备的irq号。在acpi_prt_list链表中存放PCI总线的中断路由表,本章将在第15.1.2节进一步介绍该表。其中PCI设备使用低电平触发方式。值得注意的是,PCI设备的INTA#信号首先与LPC的PIRQA#信号相连,而PIRQA#信号再与I/O APIC1的IRQ_PIN16相连。......

2023-10-20

图2-4 MPC8548处理器存储器域到PCI域的转换在介绍MPC8548处理器如何使用Outbound寄存器组进行存储器域地址空间到PCI总线域地址空间的转换之前,本节将首先介绍Outbound寄存器组中的相应寄存器。该位是Outbound窗口的使能位,为1表示当前Outbound寄存器组描述的存储器地址空间到PCI总线地址空间的映射关系有效;为0表示无效。检查LAWBAR和LAWAR寄存器,判断当前36位的物理地址是否属于PCI总线空间。......

2023-10-20

在PCIe总线中,一个地址转换关系由8B组成,这也是地址转换请求TLP的Length字段至少为0b10的原因。当TA收到地址转换请求TLP后,将查找ATPT,然后通过存储器读完成TLP,将转换关系发送给PCIe设备。采用这种方式时,PCIe设备将首先向TA发送地址转换请求TLP,并从ATPT中获得地址转换关系后,使用TA等于0b10的存储器读写TLP,即使用Translated Address与主存储器进行数据交换,从而有效避免了上文所述的安全隐患。......

2023-10-20

相关推荐