PCIe设备使用两种电源信号供电,分别是Vcc与Vaux,其额定电压为3.3V。在PCIe总线中,使用Vaux的主要原因是为了降低功耗和缩短系统恢复时间。PCIe设备使用该信号复位内部逻辑。PCIe总线定义了多种复位方式,其中Cold Reset和Warm Reset这两种复位方式的实现与该信号有关,详见第4.1.5节。当PCIe设备准备退出L2状态时,可以使用Beacon信号,提交唤醒请求。......

2023-10-20

PCI总线0上存储器控制器(Device 0)是一个比较特殊的PCI设备,这个设备除了需要管理DDR SDRAM之外,还管理整个存储器域的地址空间,包括PCI总线域地址空间。在x86处理器系统中,该设备是管理存储器域空间的重要设备,其中含有许多与存储器空间相关的寄存器。

这些寄存器对于系统程序员理解x86处理器的存储器拓扑结构非常重要,对底层编程有兴趣的系统程序员需要掌握这些寄存器。但是在x86处理器系统中,由于BIOS的存在,绝大多数系统程序员并没有机会实际使用这些寄存器。

从底层开发的角度上看,x86处理器系统并不如PowerPC、MIPS和ARM处理器透明。x86处理器首先使用BIOS屏蔽了处理器的硬件实现细节,其次在处理器内核中使用了Mi-crocode[15]进一步屏蔽了CPU的实现细节。这使得底层程序员在没有得到充分的资源时,几乎无法开发x86处理器的底层代码。

但是不可否认的是x86处理器底层开发的复杂程度超过PowerPC、MIPS和ARM处理器,因为x86处理器系统作为通用CPU需要与各类操作系统兼容,而向前兼容对于任何一种处理器都是一个巨大的包袱。x86处理器系统使用BIOS和Microcode屏蔽硬件细节基于许多深层次的考虑,包括技术和商业上的考虑,这种做法在PC领域取得了巨大的成功。

从传统外部设备的角度上看,PCI总线0的Device 0并不是一个设备,仅存放与处理器系统密切相关的一组参数。而除了x86处理器之外,几乎所有处理器都使用存储器映射寻址的寄存器保存这些参数。

x86处理器需要考虑向前兼容,因此存在许多独特的设计。这些独特的设计极易使一些初学者混淆计算机体系结构中的一些基本概念。从这个角度来看,x86处理器并不适合教学,但这并不影响x86处理器在PC领域的地位。值得注意的是,在x86处理器中,PCI总线0的Device 0的存在并不完全是为了向前兼容,而是Intel使用PCI总线概念统一所有外部设备的方法。

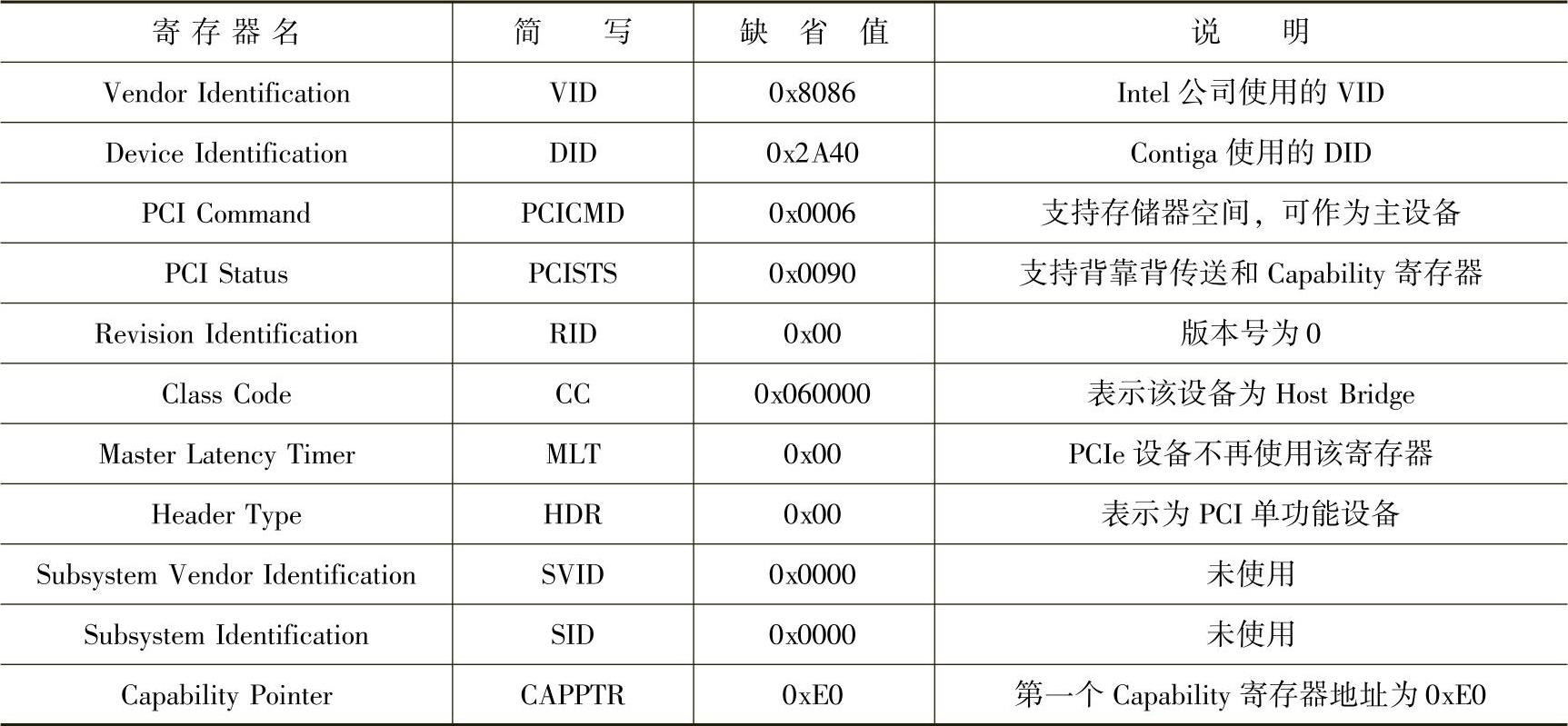

在Montevina平台中,系统软件使用Type 00h配置请求访问存储器控制器,该存储器控制器除了具有一个标准PCI Agent设备的64B的配置空间之外,还使用了PCI设备的扩展配置空间,其包含的主要寄存器如表5-1所示。

表5-1 Device 0的基本配置空间

(www.chuimin.cn)

(www.chuimin.cn)

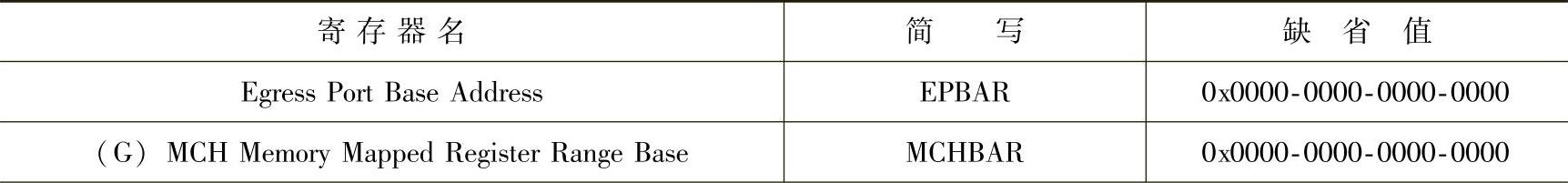

Device 0使用的基本配置空间与其他PCI设备兼容。这里值得注意的是Device 0在PCIe体系结构中,被认为是HOST主桥。而Device 0使用的PCI扩展配置空间也被称为RCRB,RCRB的主要作用是描述当前处理器的存储器地址拓扑结构,包括主存储器地址和PCI总线地址。其简写和复位值如表5-2所示。

表5-2 Device 0的扩展PCI配置空间

(续)

系统软件首先检查Capability Identifier寄存器,该寄存器的地址偏移为0xE0,即CAP-PTR寄存器指向的地址为0xE0。该Capability结构使用的PCI Express Extended Capability ID字段(该字段在CAPID0寄存器中)为0x0A,因此表5-2中的寄存器组为RCRB Capability结构,有关Capability结构的组成结构见第4.3节。

在x86处理器系统中,RCRB存放一些与处理器系统相关的寄存器。而在许多处理器中,如在PowerPC处理器中并不含有RCRB。在PowerPC处理器中,与处理器系统相关的寄存器都存放在以BASE_ADDR为起始地址的1MB连续的物理地址空间中,PowerPC处理器系统使用存储器映射寻址方式访问这些寄存器。

在x86处理器系统中,使用PCI总线管理所有外部设备,这些“与处理器系统相关的寄存器”被保存在RCRB中,处理器使用PCI总线配置周期访问这些寄存器。实际上在RCRB中包含的寄存器与PCIe体系结构并没有直接关系,这些寄存器应该属于存储器域的地址区域。x86处理器的这种做法并非完全合理,在某种程度上容易使初学者混淆存储器域与PCI总线域的区别。RCRB主要寄存器的含义如下所示。

有关PCI Express体系结构导读的文章

PCIe设备使用两种电源信号供电,分别是Vcc与Vaux,其额定电压为3.3V。在PCIe总线中,使用Vaux的主要原因是为了降低功耗和缩短系统恢复时间。PCIe设备使用该信号复位内部逻辑。PCIe总线定义了多种复位方式,其中Cold Reset和Warm Reset这两种复位方式的实现与该信号有关,详见第4.1.5节。当PCIe设备准备退出L2状态时,可以使用Beacon信号,提交唤醒请求。......

2023-10-20

图4-1云计算的架构服务方面,主要以向用户提供各种基于云的服务为主,共包含三个层次:SaaS:这层的作用是将应用以主要基于Web的方式提供给客户。管理方面,主要以云的管理层为主,其功能是确保整个云计算中心能够安全和稳定的运行,并能被有效地管理。......

2023-06-23

事务层是PCIe总线层次结构的最高层,该层次将接收PCIe设备核心层的数据请求,并将其转换为PCIe总线事务,PCIe总线使用的这些总线事务在TLP头中定义。PCIe的事务层还支持流量控制和虚通路管理等一系列特性,而PCI总线并不支持这些新的特性。在PCIe总线中,不同的总线事务采用的路由方式不相同。PCIe总线使用的数据报文首先在事务层中形成,这个数据报文也称为事务层数据报文,即TLP。......

2023-10-20

本章主要讲述在PCI/PCIe总线中,数据传送的“序”与可能出现的死锁。在PCI/PCIe总线中,序与生产/消费者模型密切相关。生产/消费者模型是一种并发协作模型,PCI/PCIe设备使用该模型进行数据传递。在PCI/PCIe总线中,访问“序”的安排必须保证生产/消费者模型的正确运转,这也意味着在PCI/PCIe总线中,数据的传送规则需要与生产/消费者模型一致。而PCI/PCIe总线针对的就是这样的一个通用处理器系统。本章将在第11.3节介绍PCI总线的序,并在第11.4节详细介绍PCIe总线的序。......

2023-10-20

PCIe体系结构以Intel的x86处理器为蓝本实现,已深深地烙下x86处理器的印记。一个基于PCIe架构的处理器系统A如图4-7所示。图4-7 基于PCIe总线的处理器系统A在图4-7的结构中,处理器系统首先使用一个虚拟的PCI桥分离处理器系统的存储器域与PCI总线域。PCI/PCIe总线在x86处理器系统中的地位超乎想象,而且并不仅局限于硬件层面。P4080处理器是Freescale第一颗基于E500mc内核的处理器。多数采用CoreNet架构互连的处理器系统使用目录表法......

2023-10-20

CPU访问主存储器时,首先将读写命令放入读写指令缓冲中,然后将这个命令发送到DRAM控制器或者HOST主桥。目前处理器系统的DRAM一般由DDR-SDRAM组成,有的书籍也将这部分内存称为主存储器。但是这并不意味着DRAM域一定包含在CPU域中,在某些处理器系统中,CPU并不能访问在DRAM域中的某些数据区域。而CPU域中除了包含DRAM域外,还包含外部设备空间。本书使用存储器域统称CPU域与DRAM域。......

2023-10-20

ARM体系架构的版本就是它所使用的指令集的版本。ARM架构支持32位的ARM指令集和16位的Thumb指令集,后者使得代码的存储空间大大减小。一些ARM7系列的处理器和Intel公司的StrongARM处理采用ARMv4指令集。ARMv5TE1999年,ARMv5TE版本改进了Thumb指令集,增加了一些“增强型DSP指令”,简称为E指令集。ARMv5TEJ2000年,ARMv5TEJ版本中增加了Jazelle技术用于提供Java加速功能。ARMv6中包含了一些媒体指令以支持SIMD媒体功能扩展。......

2023-11-22

PCIe总线的电源管理包含ASPM和软件电源管理两方面内容。所谓ASPM是指PCIe链路在没有系统软件参与的情况下,由PCIe链路自发进行的电源管理方式。PCIe总线为PCIe设备提供了几种低功耗模式。但是PCI/PCIe总线提供的电源管理机制远非完美,该管理机制仅考虑了外部设备与处理器系统之间的电源使用关系,并没有考虑外部设备之间电源的使用关系。目前在智能手机的设计中,通常具有专门用于电源管理的微处理器。......

2023-10-20

相关推荐