PCI总线作为处理器系统的局部总线,其主要目的是为了连接外部设备,而不是作为处理器的系统总线连接Cache和主存储器。孤立地研究PCI总线并不可取,因为PCI总线仅是处理器系统的一个部分。深入理解PCI总线需要了解一些与处理器体系结构相关的知识。PCI规范并没有对HOST主桥的设计进行约束。PCI桥是PCI总线的一个重要组成部件,该部件的存在使得PCI总线极具扩展性。PCI总线提供的峰值带宽远高于这些总线。......

2023-10-20

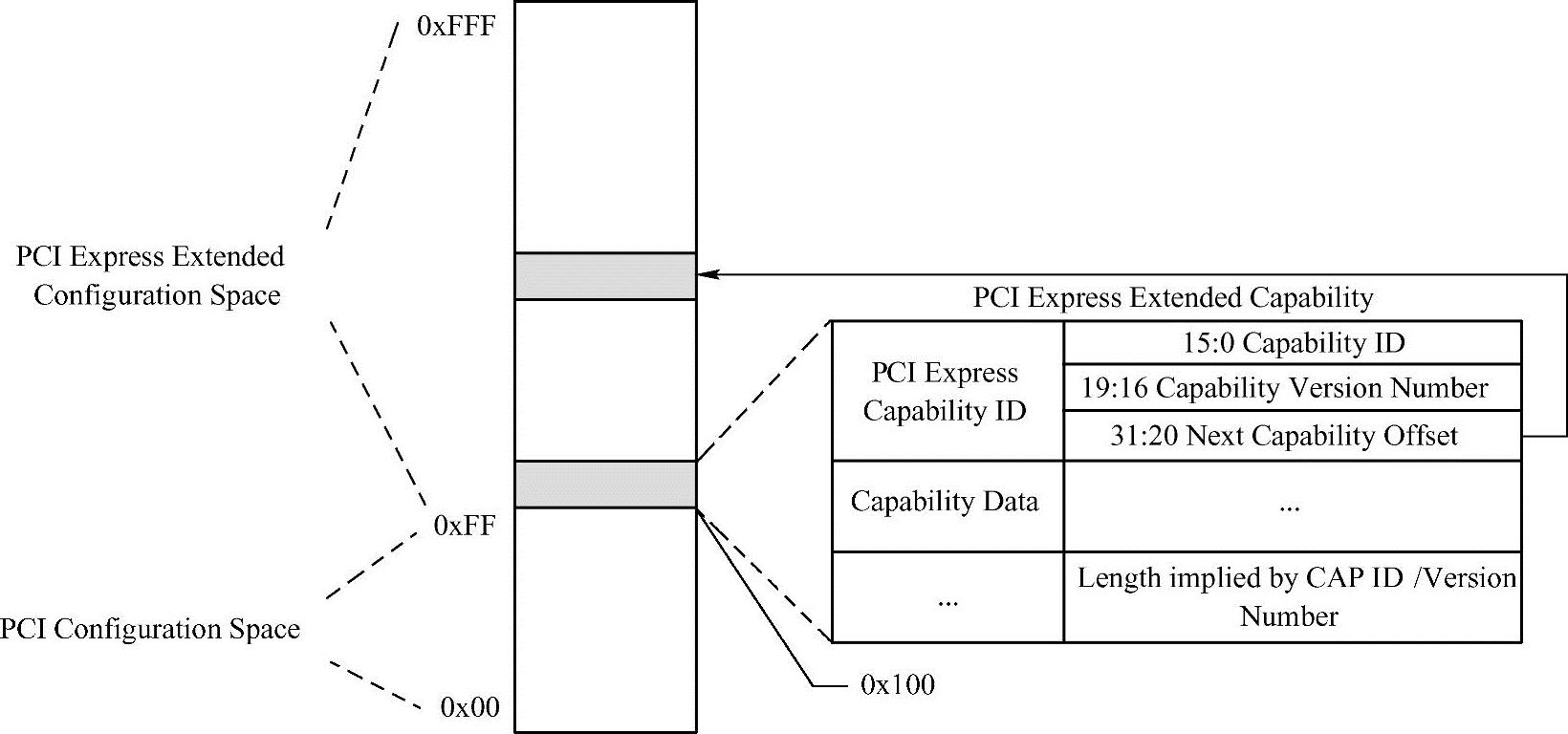

PCI Express Extended Capabilities结构存放在PCI配置空间0x100之后的位置,该结构是PCIe设备独有的,PCI设备并不支持该结构。实际上绝大多数PCIe设备也并不支持该结构。在一个PCIe设备中可能含有多个PCI Express Extended Capabilities结构,并形成一个单向链表,其中第一个Capability结构的基地址为0x100,其结构如图4-19所示。

在这个单向链表的尾部,其Next Capability Offset、Capability ID和Capbility Version字段的值都为0。如果在PCIe设备中不含有PCI Express Extended Capabilities结构,则0x100指针所指向的结构,其Capability ID字段为0xFFFF,而Next Capability Offset字段为0x0。

图4-19 PCI Express Extended Capabilities结构

一个PCI Express Extended Capabilities结构由以下参数组成。

●PCI Express Capability ID字段存放Extended Capability结构的ID号。

●Capability Version字段存放Extended Capability结构的版本号。

●Next Capability Offset字段存放下一个Extended Capability结构的偏移。

PCIe总线定义了一系列PCI Express Extended Capabilities结构,如下所示。

●AER Capability结构。该结构定义了所有PCIe设备可能遇到的错误,包括Uncorre ct-able Error(不可恢复错误)和Correctable Error(可恢复错误)。当PCIe设备发现这些错误时,可以根据该寄存器的设置使用Error Message将错误状态发送给Event Col-lector,并由Event Collector统一处理这些错误。系统软件必须认真处理每一个Error Message,并进行恢复。对一个实际的工程项目,错误处理是保证整个项目可靠性的重要一环,不可忽视。AER机制与Error Message报文的处理相关,第6.3.4节将进一步介绍AER机制。

●Device Serial Number Capability结构。该结构记载PCIe设备使用的序列号。IEEE定义了一个64位宽度的PCIe序列号,其中前24位作为PCIe设备提供商使用的序列号,而后40位由厂商选择使用。

●PCIe RC Link Declaration Capability结构。在RC、RC内部集成的设备或者RCRB中可以包含该结构。该结构存放RC的拓扑结构,如RC使用的PCI链路宽度。如果RC支持多个PCIe链路,该结构还包含每一个链路的描述和端口命名。

●PCIe RC Internal Link Control Capability结构。该结构的主要作用是描述RC内部互连使用的PCIe链路。该结构由Root Complex Link Status和Root Complex Link Control寄存器组成。

●Power Budget Capability结构。当处理器系统为一些动态加入的PCIe设备分配电源配额时,将使用该设备的Power Budget Capability结构。

●ACS(Access Control Services)Capability结构。该结构对PCIe设备进行访问控制管理。RC端口、Switch的下游端口和多功能PCIe设备可以支持该结构。该结构与PCIe总线的ACS机制相关。ACS机制定义了一组与收到的TLP相关的操作,该机制的原理较为简单,本节对此不做进一步分析。

●RCRB Header Capability结构。该结构存放RC中的RCRB,第5.1节将以Montivina平台为例介绍该结构的组成结构。

●RC Event Collector EP Association Extended Capability。在x86处理器系统中,RC包含一个Event Collector控制器,该控制器处理PCIe设备发向RC的各类消息,如PME消息和Error消息。该结构用来描述Event Collector控制器。

●Multicast Capability结构。PCIe总线上的RC、Switch或者EP如果支持Multicast消息,需要使用该结构描述支持哪些Multicast组。PCIe体系结构支持Multicast功能,在PCIe总线中,除了PCIe桥一定不支持Multicast功能外,其他设备都可以支持该功能。本节对Multicast功能不做进一步说明。

此外PCIe总线还可以支持其他Capability结构,如Vendor-Defined Capability、Resizable BAR Capability、DPA(Dynamic Power Allocate)和MFVC(Multi-Function Virtual Channel)Capability结构等其他结构。但是在PCIe总线中,这些扩展的Capability结构并没有得到充分利用。在一个实际的PCIe设备中可能并不包含这些结构。

PCIe设备定义的Capability结构有些过多,使用这种方法可以概括所有PCIe设备的使用特性。许多PCIe设备在支持这些Capability结构后,几乎可以不使用BAR寄存器空间存放与PCIe总线相关的任何信息。但是过多的Capability结构为软硬件工程师在设计上带来了不小的麻烦。一般说来,事务的发展过程是由简入繁,由繁化简。目前PCIe总线的发展仍处在由简入繁的过程。

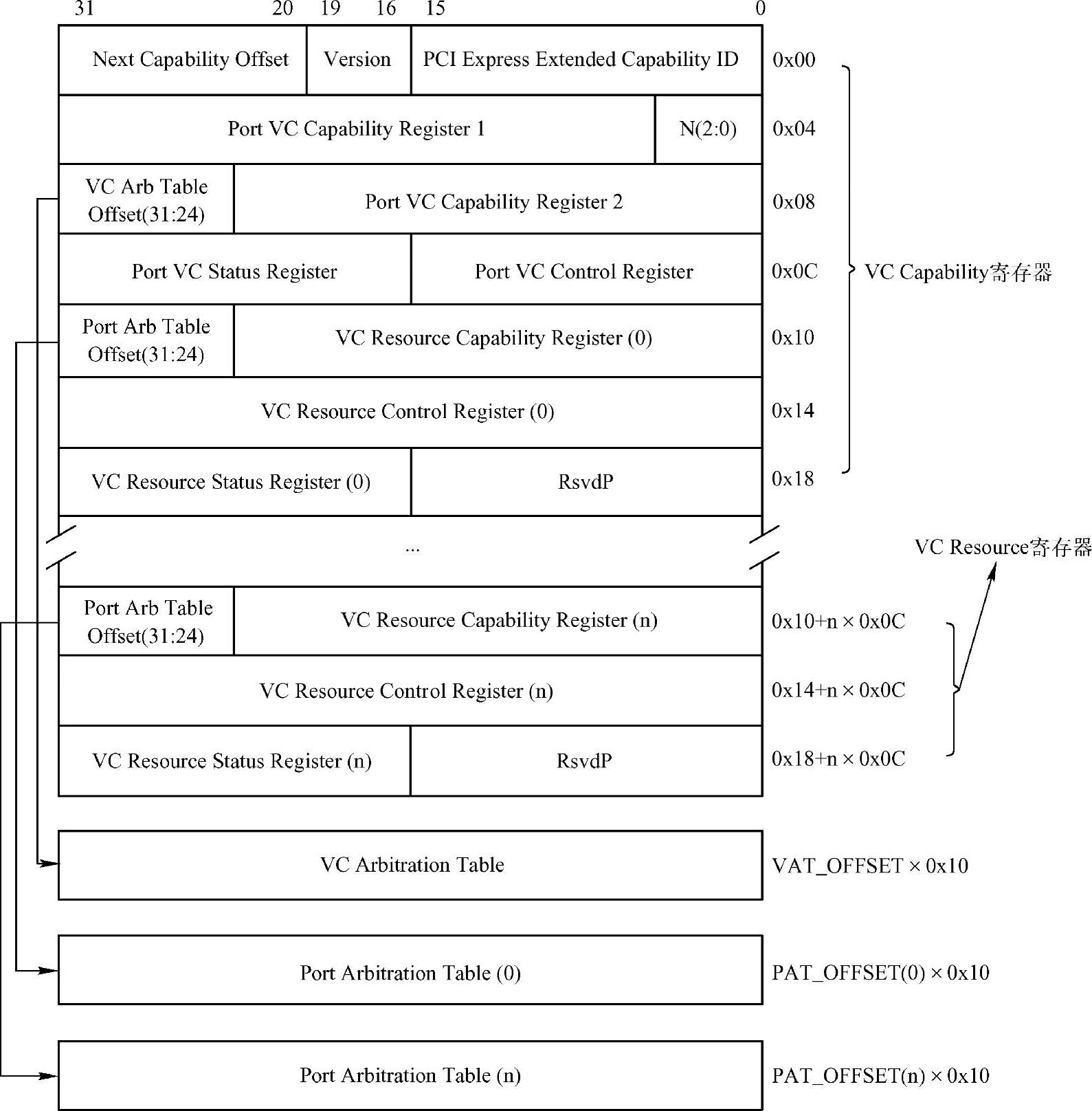

本节仅详细介绍PCI Express Extended Capabilities结构组中的MFVC结构。MFVC结构是PCIe总线的一个可选结构,其结构如图4-20所示。TLP在通过Switch时需要通过TC/VC Mapping,而且在进行VC仲裁和端口仲裁时,需要使用某些仲裁策略。

在PCIe总线中,TC/VC Mapping表和VC/端口仲裁策略在MFVC结构中定义。其结构如图4-20所示。值得注意的是,在许多PCIe设备中,可能只具有一个VC,而且其VC仲裁的算法固定,那么在这个PCIe设备中,MFVC结构并没有存在的必要。目前支持多VC的PCIe设备极少,仅有一些RC和Switch中存在多个VC,而且也仅支持两个VC。

VC Capability的ID为0x02或者0x09,VC Capability结构由两部分组成,分别是一个VC Capability寄存器组和n个VC Resource寄存器组,其中VC Resource寄存器是可选的。如果PCIe设备仅支持一个VC时,该结构中不含有VC Resource寄存器,而在VC Capability寄存器组中包含该VC的描述信息。当一个PCIe设备支持8个Function时,则n为7;如果支持7个设备,则n为6,并以此类推。其中每一个VC Resource寄存器组中都包含一个VC仲裁表、端口仲裁表和VC/TC的映射表。

1.VC Capability寄存器组

该组寄存器由Port VC Capability Register 1、Port VC Capability Register 2、Port VC Control Register和Port VC Status Register寄存器组成。

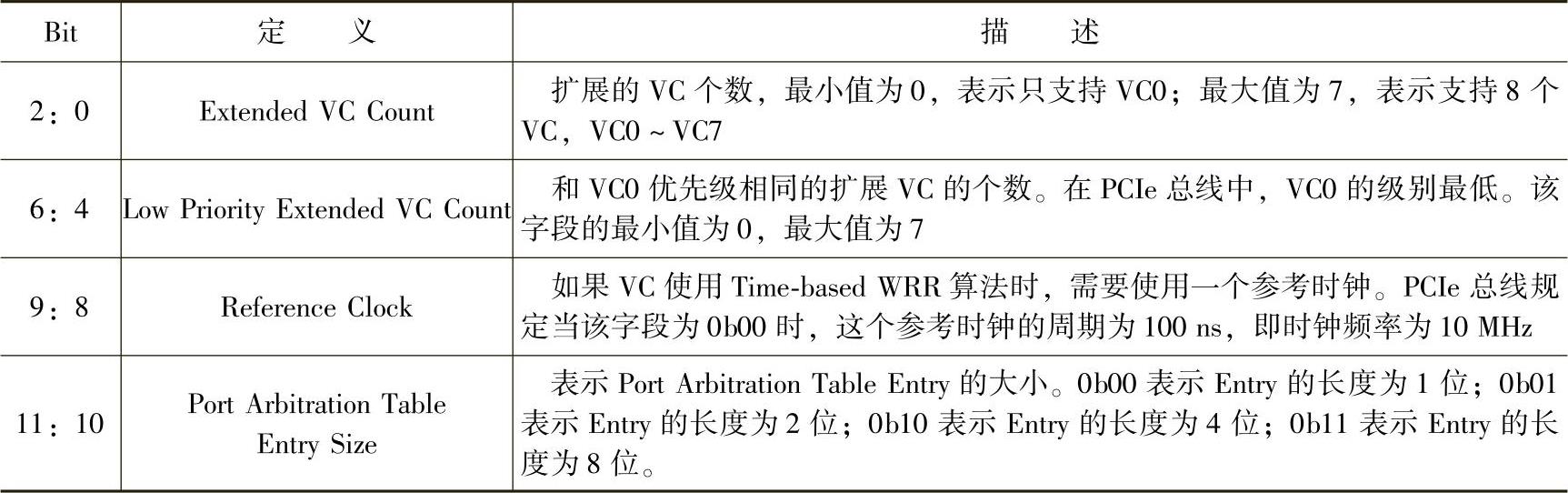

(1)Port VC Capability Register 1主要字段的含义如表4-10所示。

图4-20 MFVC结构

表4-10 Port VC Capability Register 1

(2)Port VC Capability Register 2

该寄存器由两个字段组成。其中VC Arbitration Capability字段存放PCIe设备支持的VC调度算法,PCIe总线提供的调度算法包括Hardware-fixed仲裁策略和WRR仲裁策略。其中WRR仲裁策略分为32、64或者128个Phase,VC仲裁不支持Time-based WRR算法,有关WRR算法的详细说明见下文。

而VC Arbitration Table Offset字段存放VC Arbitration Table的地址偏移,如果在PCIe设备中不含有VC Arbitration Table,该字段为0。

(3)Port VC Control Register(www.chuimin.cn)

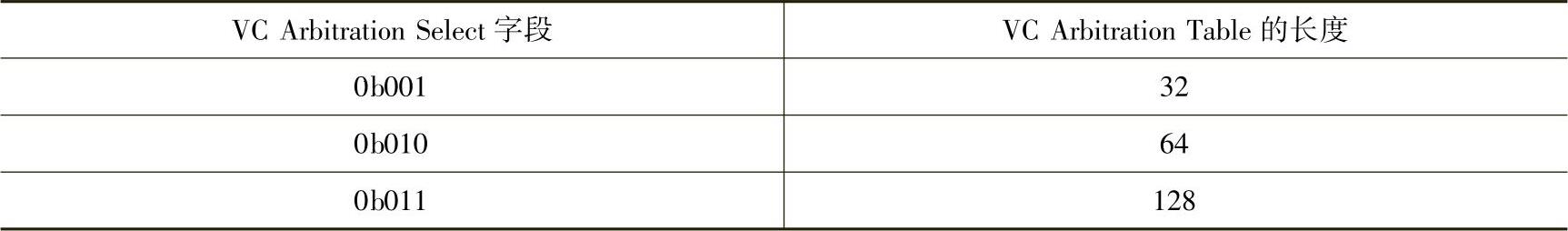

该寄存器由Load VC Arbitration Table位和VC Arbitration Select字段组成。系统软件通过操纵该寄存器更改VC的仲裁算法,其中VC Arbitration Select字段用来选择VC Arbitration Table的长度,其关系如表4-11所示。

表4-11 VC Arbitration Select字段的说明

Load VC Arbitration Table位用来更新VC的仲裁算法。系统软件向Load VC Arbitration Table位写1时更新VC的仲裁算法,PCIe设备可以根据VC Arbitration Select字段选择合适的仲裁算法,系统软件向Load VC Arbitration Table位写0没有意义。

(4)Port VC Status Register

Port VC Status Register使用VC Arbitration Table Status位,控制更新VC仲裁算法的进度。当系统软件向Load VC Arbitration Table位写1时,PCIe设备将更新VC的仲裁算法,并将VC Arbitration Table Status位置1。PCIe设备在没有完成仲裁算法的更换之前,VC Arbitra-tion Table Status位一直为1,当PCIe设备完成仲裁算法的更换后,该位被PCIe设备清零。

2.VC Resource寄存器组

在PCIe设备中,每一个VC都有一组VC Resource寄存器组,这组寄存器设置每一个VC的属性和端口仲裁算法。该组寄存器由VC Resource Capability Register、VC Resource Con-trol Register和VC Resource Status Register寄存器组成。

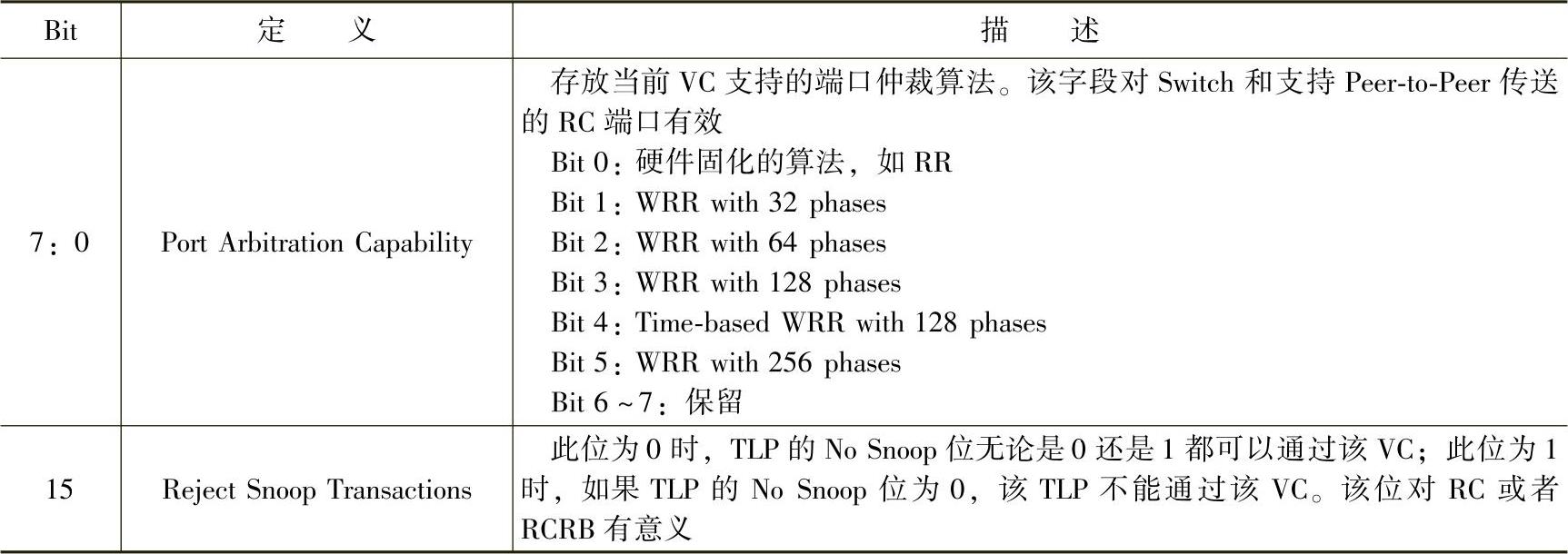

(1)VC Resource Capability Register主要字段的含义如表4-12所示。

表4-12 VC Resource Capability Register

(2)VC Resource Control Register主要字段的含义如下。

●TC/VC Map字段,第7~0位。该字段的每一位对应一个TC,其中第7位对应TC7,该位有效时表示TC7使用该VC进行数据传递;第6位对应TC6,该位有效时表示TC6使用该VC进行数据传递,并以此类推。对于VC0通路,该字段的复位值为0xFF,对于其他VC通路,该字段的复位值为0x00。因此在系统初始化时,所有TC都使用VC0进行数据传递,而PCIe链路必须支持VC0。使用该字段可以保证TC不同的TLP可以使用同一个VC,但是在PCIe总线中,一个TC与一条VC建立了映射关系后,不能与其他VC建立映射关系。

●Load Port Arbitration Table位,第16位。当该位被置1后,PCIe设备将使用Port Arbi-tration Table更新端口仲裁的算法,当该位置1后,VC Resource Status寄存器的Port Arbitration Table Status位也将置1,当端口仲裁算法更新完毕后,Port Arbitration Table Status位将清零;对此位写1没有意义。

●Port Arbitration Select字段,第19~17位。该字段描述Port Arbitration Table表的Entry个数。下文将详细解释该字段。

●VC ID字段,第26~24位。该字段存放当前VC的ID号,PCIe设备的第一个VC ID必须为0。

●VC Enbale位,第31位。该位为1时,当前VC通路有效,否则无效。在系统初始化完毕后,VC0的VC Enable位为1,而其他VC的VC Enable位为0。

(3)VC Resource Status Register主要字段的含义如下。

●Port Arbitration Table Status位,第0位。该位表示当前VC更新端口仲裁算法的状态,该位由PCIe设备维护,对系统软件只读。

●VC Negotiation Pending位,第1位。该位为1表示当前VC通路正在进行初始化或者处于正在关闭的状态,此时当前VC并没有准备好,还没有从FC_INIT2状态中退出;为0表示当前VC准备好,PCIe链路已经完成流量控制的初始化。系统软件必须保证该位为0后,才能对该VC进行操作。有关FC_INIT2状态的详细说明见第9.3.3节。

3.VC Arbitration Table

VC Arbitration Table的长度由Port VC Control寄存器的VC Arbitration Select字段确定,最小为32个Entry,最大为128个Entry。VC Arbitration Table实现VC仲裁的WRR算法。在VC Arbitration Table中,每一个Entry由4位组成,其中最高位保留,最低三位记录VC号。下文举例说明32个Phase的WRR算法,在这种情况下VC Arbitration Table的长度为32,这个表中每一个Entry记录一个VC号,如图4-21所示。

在图4-21中,VC Arbitration Table的每一个Entry都记录一个VC号。假定VC仲裁时从Phase0开始使用,该Entry存放的VC号为VC0,则VC仲裁的结果是传送虚通路VC0中的总线事务,当这个总线事务传送结束后,将处理Phase1中的VC;如果该Entry存放的VC号为VC2,则VC仲裁的结果是传送虚通路VC2中的总线事务,并以此类推直到Phase31后,再对Phase0重新进行处理。

使用这种加权处理的方法,可以保证PCIe总线QoS。值得注意的是,使用该方法时,如果当前Entry存放的VC中,不存在总线事务时,将迅速移动到下一个Entry;如果VC间并没有出现冲突时,不需要使用该表进行仲裁,使用64个Phase和128个Phase的WRR算法的实现机制与此类似。由上文的分析可以发现,与RR算法相比,PCIe总线使用WRR算法可以在保证QoS的基础上,使各个VC公平使用端口资源。

图4-21 32 Phases的VC Arbitration Table

4.Port Arbitration Table

每一个VC都有一个Port Arbitration Table,如图4-12所示。每一个TLP都首先需要进行端口仲裁之后,才能进行VC仲裁,然后通过端口发送。Port Arbitration Table的主要作用是确定端口仲裁的策略。其长度由VC Resource Capability Register的Port Arbitration Capability字段确认,如表4-12所示。

在该表中,每一个Entry的大小由该设备支持的端口数目有关,如果一个设备支持N个端口,则该表Entry的大小为[Log2N]。如果一个设备有6个端口,则Port Arbitration Table的Entry大小为3。PCIe总线支持RR、WRR和Time-based WRR端口仲裁策略。

Time-based WRR端口仲裁策略的引入是为了支持PCIe总线的isochronous数据传送方式。在PCIe总线中使用WRR算法每处理完一个总线事务将移动一个Phase,而Time-based WRR算法需要至少经过一个时间槽后才能移动一个Phase。PCIe总线为Time-based WRR算法使用的基准时钟周期在Port VC Capability Register 1的Reference Clock字段中定义,目前该值为100ns。

PCIe总线中使用的这些仲裁算法源于网络通信,这几种算法都是基于轮询的仲裁算法。在网络中,还经常使用DWRR(Deficit Weighted Round Robin)算法。

WRR算法在支持长度不同的报文时,会出现带宽分配不公平的现象,为此M.Shre edhar与George Varghese提出了DWRR调度算法。DWRR算法给每一个队列分配的权值不是基于报文的个数,而是基于报文的比特数。因此可以使各个队列公平地获得带宽。但是这种算法并不适用于PCIe总线,因为PCIe总线基于报文进行数据传递,而不是基于数据流。该算法在ATM分组交换网中得到了广泛的应用。

有关PCI Express体系结构导读的文章

PCI总线作为处理器系统的局部总线,其主要目的是为了连接外部设备,而不是作为处理器的系统总线连接Cache和主存储器。孤立地研究PCI总线并不可取,因为PCI总线仅是处理器系统的一个部分。深入理解PCI总线需要了解一些与处理器体系结构相关的知识。PCI规范并没有对HOST主桥的设计进行约束。PCI桥是PCI总线的一个重要组成部件,该部件的存在使得PCI总线极具扩展性。PCI总线提供的峰值带宽远高于这些总线。......

2023-10-20

恒定区决定了抗体分子的种属特异性。超变区氨基酸序列决定了该抗体结合抗原的特异性。一个抗体分子上的两个抗原结合部位是相同的,称为抗原结合片段。抗体不仅具有特异性结合抗原的能力,还能活化补体,结合细胞表面的Fc受体,并能通过母体胎盘转移给胎儿,从而赋予被动免疫的重要作用。长期以来,抗体被用于治疗感染和毒素。而在免疫分析中,抗体可用于对抗体和抗原的检测及定量分析,还能研究抗原的结构。......

2023-06-24

现代科学认为,基因是DNA分子的一个片断,是一个遗传功能单位。天然存在的DNA几乎都是右旋DNA,称为B-DNA。DNA的主要生物功能有如下几个方面。(一)DNA的自我复制有生命物质与无生命物质的主要区别在于是否具有自我复制和繁殖能力。每个模板DNA均有转录的终止位点或终止因子。由此证实,核糖体是由rRNA与多种蛋白质组装而成的,其生物学功能为蛋白质合成的场所。......

2023-11-22

我国在市场上销售的乙炔瓶均为公称容积40L的三件组装形式。乙炔瓶典型结构型式如图4-22所示。乙炔瓶的颈圈用低碳圆钢加工而成,是瓶帽与瓶体、瓶阀与瓶体连接的零件。乙炔瓶是储存和运输乙炔的容器,其外形与氧气瓶相似,但构造要比氧气瓶复杂,这是因为乙炔不能以高压压入普通钢瓶,必须利用乙炔的特性,采取必要的措施,才能将乙炔压入钢瓶内。乙炔瓶的瓶体是圆柱形,其外表面漆成白色,并用红漆写明“乙炔”字样。......

2023-11-22

PCIe总线进行链路训练的主要目的是初始化PCIe链路的物理层、端口配置信息、相应的链路状态,并了解链路对端的拓扑结构,以便PCIe链路两端的设备进行数据通信。此时该PCIe设备在进行链路训练时,必须通知对端链路该设备实际使用的链路状态。此外PCIe总线在链路训练过程中,还需要确定数据传送率。PCIe总线进行链路训练时,需要进行RC或者Switch的Link Number和Lane Number的初始化,在第8.2节中将详细介绍这些内容。......

2023-10-20

图12-1 Capric卡的组成结构Capric卡基于PCIe总线,主要功能是通过DMA读写方式与HOST处理器进行数据交换。Capric卡由LogiCORE、发送部件、接收部件、BAR空间、DMA控制逻辑和FPGA片内SRAM组成,其工作原理较为简单。Capric卡仅使用了BAR0空间,处理器使用存储器映像寻址方式,而不是I/O映像寻址方式访问BAR0空间。......

2023-10-20

此外PCI/PCI-X和PCIe设备还扩展了0x40~0xFF这段配置空间,在这段空间主要存放一些与MSI或者MSI-X中断机制和电源管理相关的Capability结构。PCIe设备使用的扩展配置空间最大为4KB,在PCIe总线的扩展配置空间中,存放PCIe设备所独有的一些Capability结构,而PCI设备不能使用这段空间。PCI-X和PCIe总线规范要求其设备必须支持Capabilities结构。......

2023-10-20

并行序列的结束称为合并,在表示同步的水平双线之下,只允许有一个转换符号。图6-12 顺序功能图的三种结构a)单序列 b)选择序列 c)并列序列......

2023-06-15

相关推荐