(一)经轴架经轴架简称轴架,用来放置经轴,位于浆纱机的后方。经纱从若干经轴上引出合并,以达到工艺要求的总经根数。新型浆纱机的经轴架一般由槽钢立柱和横撑连接而成。图7-40经轴架结构1—经轴 2—轴承座 3—开口滑动轴承4—转动手轮 5—调节螺钉 6—加压夹4.经轴架结构 轴架的结构比较简单,如图7-40所示为G142 型浆纱机的轴架结构图。此后,又经第二浸没辊、第二上浆辊和压浆辊做再次浸浆与压浆。......

2025-09-29

在不同的处理器系统中,PCIe体系结构的实现方式不尽相同。PCIe体系结构以Intel的x86处理器为蓝本实现,已深深地烙下x86处理器的印记。在PCIe总线规范中,有许多内容是x86处理器独有的,也仅在x86处理器的Chipset中存在。在PCIe总线规范中,一些最新的功能也在Intel的Chipset中率先实现。

本节将以一个虚拟的处理器系统A和PowerPC处理器为例简要介绍RC的实现,并简单归纳RC的通用实现机制。

1.处理器系统A

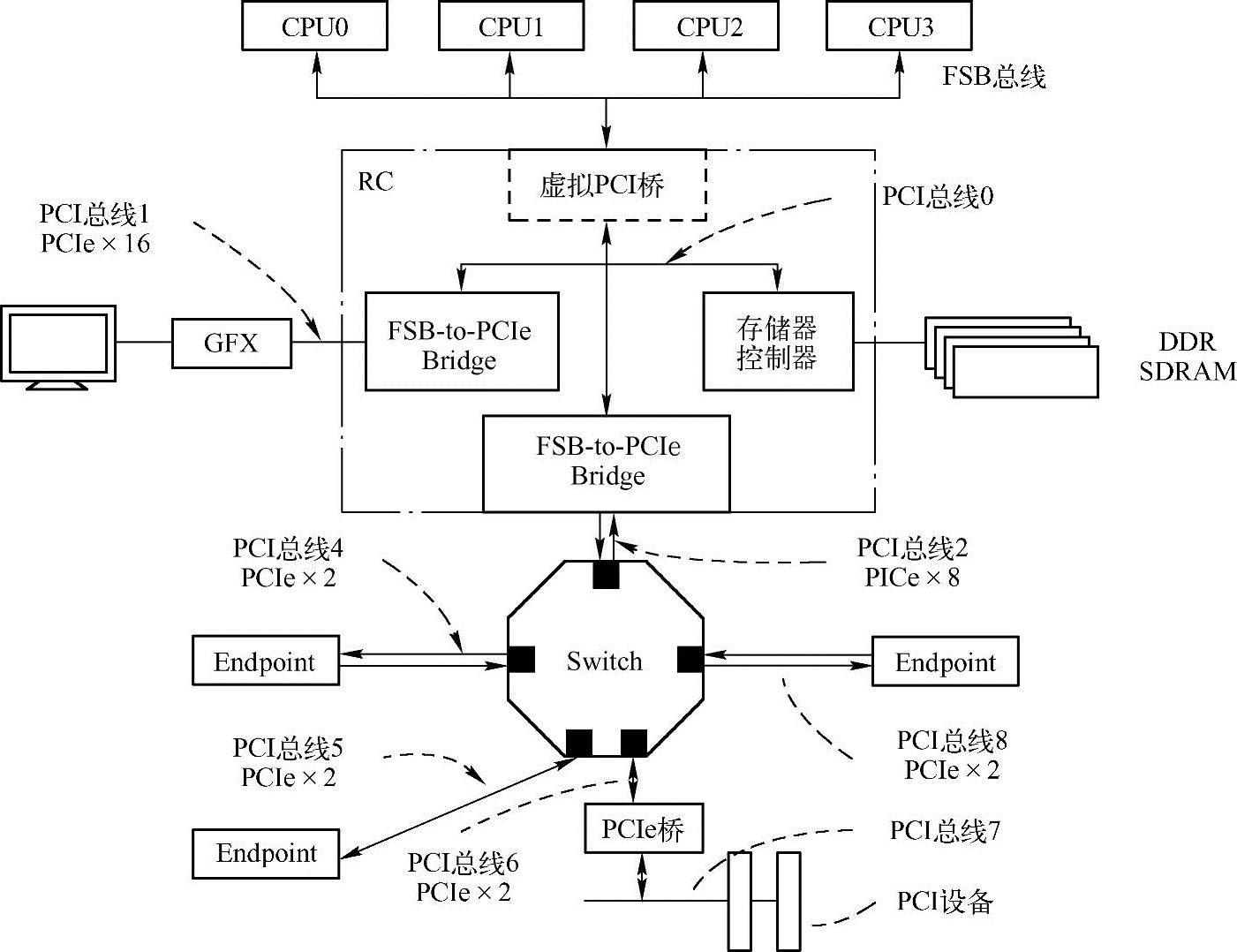

在有些处理器系统中,没有直接提供PCI总线,此时需要使用PCIe桥,将PCIe链路转换为PCI总线之后,才能连接PCI设备。在PCIe体系结构中,也存在PCI总线号的概念,其编号方式与PCI总线兼容。一个基于PCIe架构的处理器系统A如图4-7所示。

图4-7 基于PCIe总线的处理器系统A

在图4-7的结构中,处理器系统首先使用一个虚拟的PCI桥分离处理器系统的存储器域与PCI总线域。FSB总线下的所有外部设备都属于PCI总线域。与这个虚拟PCI桥直接相连的总线为PCI总线0。这种架构与Intel的x86处理器系统较为类似。

在这种结构中,RC由两个FSB-to-PCIe桥和存储器控制器组成。值得注意的是在图4-7中,虚拟PCI桥的作用只是分离存储器域与PCI总线域,但是并不会改变信号的电气特性。RC与处理器通过FSB连接,而从电气特性上看,PCI总线0与FSB兼容,因此在PCI总线0上挂接的是FSB-to-PCIe桥,而不是PCI-to-PCIe桥。

在PCI总线0上有一个存储器控制器和两个FSB-to-PCIe桥。这两个FSB-to-PCIe桥分别推出一个×16和×8的PCIe链路,其中×16的PCIe链路连接显卡控制器(GFX),其编号为PCI总线1;×8的PCIe链路连接一个Switch进行PCIe链路扩展。而存储器控制器作为PCI总线0的一个Agent设备,连接DDR插槽或者颗粒。

此外在这个PCI总线上还可能连接了一些使用“PCI配置空间”管理的设备,这些设备的访问方法与PCI总线兼容,在x86处理器的Chipset中集成了一些内嵌的设备。这些内嵌的设备均使用“PCI配置空间”进行管理,包括存储器控制器。

PCIe总线使用端到端的连接方式,因此只有使用Switch才能对PCIe链路进行扩展,而每扩展一条PCIe链路将产生一个新的PCI总线号。如图4-7所示,Switch可以将1个×8的PCIe端口扩展为4个×2的PCIe端口,其中每一个PCIe端口都可以挂接EP。除此之外PCIe总线还可以使用PCIe桥,将PCIe总线转换为PCI总线或者PCI-X总线,之后挂接PCI/PCI-X设备。多数x86处理器系统使用这种结构连接PCIe或者PCI设备。

采用这种结构,有利于处理器系统对外部设备进行统一管理,因为所有外部设备都属于同一个PCI总线域,系统软件可以使用PCI总线协议统一管理所有外部设备。然而这种外部设备管理方法并非尽善尽美,使用这种结构时,需要注意存储器控制器使用的寄存器也被映射为PCI总线空间,从而属于PCI总线域,而主存储器(如DDR内存空间)仍然属于存储器域。因此在这种结构中,存储器域与PCI总线域的划分并不明晰。

在PCIe总线规范中并没有明确提及PCIe主桥,而使用RC概括除了处理器之外的所有与PCIe总线相关的内容。在PCIe体系结构中,RC是一个很模糊也很混乱的概念。Intel使用PCI总线的概念管理所有外部设备,包括与这些外部设备相关的寄存器,因此在RC中包含一些实际上与PCIe总线无关的寄存器。使用这种方式有利于系统软件使用相同的平台管理所有外部设备,也利于平台软件的一致性,但是仍有其不足之处。

PCIe总线在x86处理器中始终处于核心地位。Intel也借PCIe总线统一管理所有外部设备,并以此构建基于PCIe总线的PC生态系统(Ecosystem)。PCI/PCIe总线在x86处理器系统中的地位超乎想象,而且并不仅局限于硬件层面。

2.PowerPC处理器

PowerPC处理器挂接外部设备使用的拓扑结构与x86处理器不同。在PowerPC处理器中,虽然也含有PCI/PCIe总线,但是仍然有许多外部设备并不是连接在PCI总线上的。在PowerPC处理器中,PCI/PCIe总线并没有在x86处理器中的地位。在PowerPC处理器中,还含有许多内部设备,如TSEC(Three Speed Ethenet Controller)和一些内部集成的快速设备,与SoC平台总线直接相连,而不与PCI/PCIe总线相连。在PowerPC处理器中,PCI/PCIe总线控制器连接在SoC平台总线的下方。

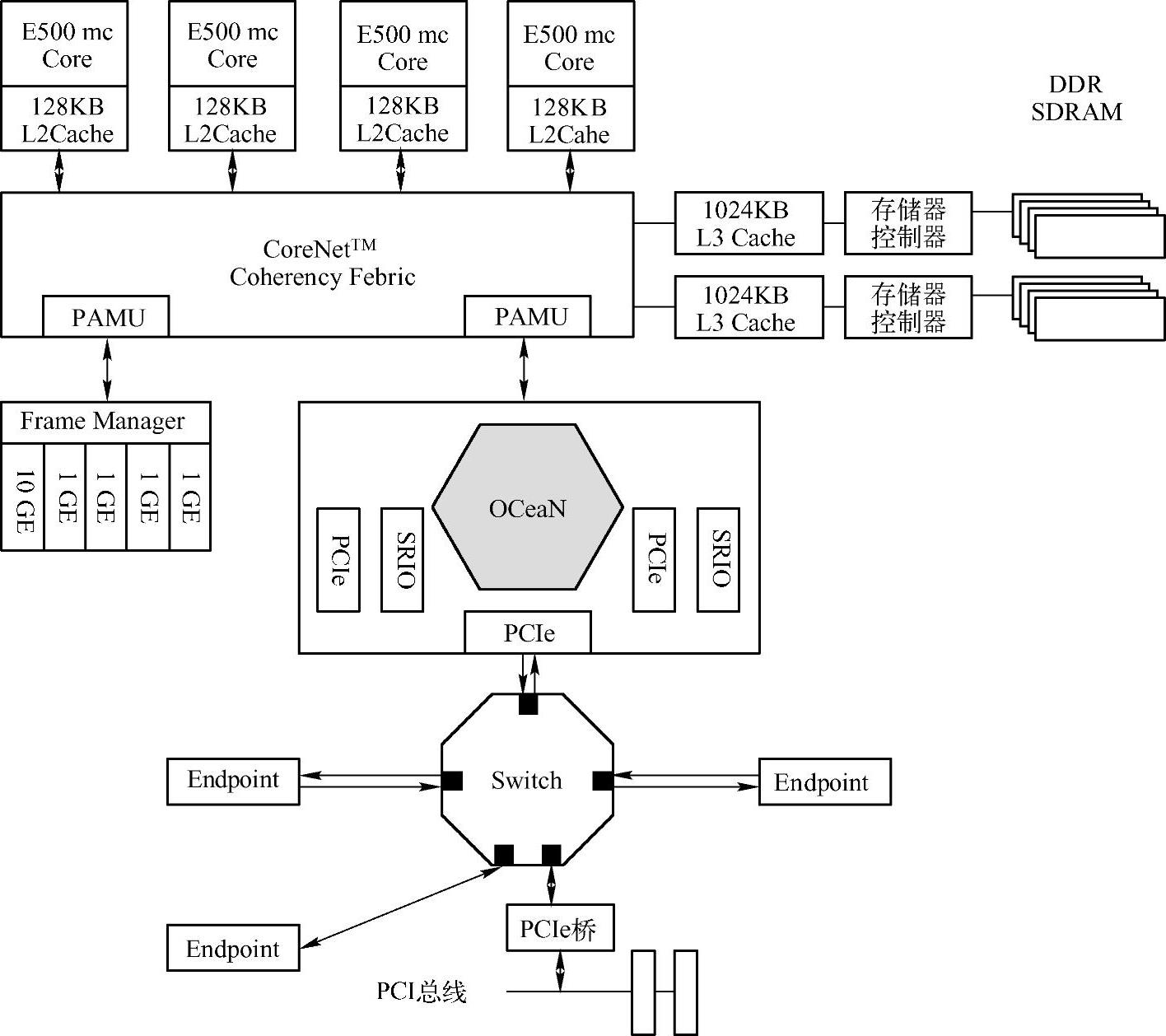

Freescale即将发布的P4080处理器,采用的互连结构与之前的PowerPC处理器有较大的不同。P4080处理器是Freescale第一颗基于E500mc内核的处理器。E500mc内核与之前的E500 V2和V1相比,从指令流水线结构、内存管理和中断处理上说并没有本质的不同。E500mc内核内置了一个128KB大小的L2 Cache,该Cache连接在BSB总线上;而E500V1/V2内核中并不含有L2 Cache,而仅含有L1 Cache,而且与FSB直接相连。在E500mc内核中,还引入了虚拟化的概念。

P4080处理器共集成了8个E500mc内核,并使用CoreNet连接这8个E500mc内核,由CoreNet互连的处理器使用交换结构进行数据交换,而不是基于共享总线结构。在P4080处理器中,一些快速外部设备,如DDR控制器、以太网控制器和PCI/PCIe总线接口控制器也是直接或者间接地连接到CoreNet中,在P4080处理器,L3 Cache也是连接到CoreNet中。P4080处理器的拓扑结构如图4-8所示。

目前Freescale并没有公开P4080处理器的L1、L2和L3 Cache如何进行Cache共享一致性。多数采用CoreNet架构互连的处理器系统使用目录表法进行Cache共享一致性。但是P4080处理器并不是一个追求峰值运算的SMP处理器系统,而针对Data Plane的应用,因此P4080处理器可能并没有使用基于目录表的Cache一致性协议。在基于全互连网络的处理器系统中如果使用“类总线监听法”进行Cache共享一致性,将不利于多个CPU共享同一个存储器系统,在Cache一致性的处理过程中容易形成瓶颈。(https://www.chuimin.cn)

如图4-8所示,P4080处理器的设计重点并不是E500mc内核,而是CoreNet。CoreNet内部由全互连网络组成,其中任意两个端口间的通信并不会影响其他端口间的通信。与MPC8548处理器相同,P4080处理器也使用OceaN[3]结构连接PCIe与RapidIO接口。

图4-8 基于PCIe总线的PowerPC处理器系统

在P4080处理器中不存在RC的概念,而仅存在PCIe总线控制器,当然也可以认为在P4080处理器中,PCIe总线控制器即为RC。P4080处理器内部含有3个PCIe总线控制器,如果该处理器需要连接更多的PCIe设备时,需要使用Switch扩展PCIe链路。

在P4080处理器中,所有外部设备与处理器内核都连接在CoreNet中,而不使用传统的SoC平台总线[4]进行连接,从而在有效提高了处理器与外部设备间通信带宽的同时,极大降低了访问延时。此外P4080处理器系统使用PAMU(Peripheral Access Management Unit)分隔外设地址空间与CoreNet地址空间。在这种结构下,10GE/1 GE接口使用的地址空间与PCI总线空间独立。

P4080处理器使用的PAMU是对MPC8548处理器ATMU的进一步升级。使用这种结构时,外部设备使用的地址空间、PCI总线域地址空间和存储器域地址空间的划分更加明晰。在P4080处理器中,存储器控制器和存储器都属于一个地址空间,即存储器域地址空间。此外这种结构还使用OCeaN连接SRIO[5]和PCIe总线控制器,使得在OCeaN中的PCIe端口之间[6]可以直接通信,而不需要通过CoreNet,从而减轻了CoreNet的负载。

从内核互连和外部设备互连的结构上看,这种结构具有较大的优势。但是采用这种结构需要使用占用芯片更多的资源,CoreNet的设计也十分复杂。而最具挑战的问题是,在这种结构之下,Cache共享一致性模型的设计与实现。

在Boxboro EX处理器系统中,可以使用QPI将多个处理器系统进行点到点连接,也可以组成一个全互连的处理器系统。这种结构与P4080处理器使用的结构类似,但是Boxboro EX处理器系统包含的CPU更多。

这种全互连的处理器结构也许是未来多核处理器发展的趋势,但是在没有合理地解决多核处理器可编程性问题之前,这种结构很可能不会被系统软件高效地利用,这也是这一结构所面临的挑战。

3.基于PCIe总线的通用处理器结构

在不同的处理器系统中,RC的实现有较大差异。PCIe总线规范并没有规定RC的实现细则。在有些处理器系统中,RC相当于PCIe主桥,也有的处理器系统也将PCIe主桥称为PCIe总线控制器。而在x86处理器系统中,RC除了包含PCIe总线控制器之外,还包含一些其他组成部件,因此RC并不等同于PCIe总线控制器。

如果一个RC可以提供多个PCIe端口,这种RC也被称为多端口RC。如MPC8572处理器的RC可以直接提供3条PCIe链路,因此可以直接连接3个EP。如果MPC8572处理器需要连接更多EP时,需要使用Switch进行链路扩展。

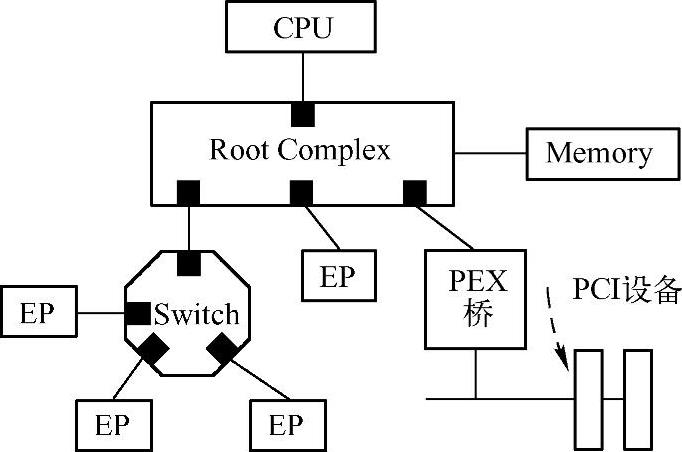

而在x86处理器系统中,RC并不是存在于一个芯片中,如在Montevina平台中,RC由MCH和ICH两个芯片组成。有关Montevina平台的详细说明见第5章。本节并不对x86和PowerPC处理器使用的PCIe总线结构做进一步讨论,而只介绍这两种结构的相同之处。一个通用的、基于PCIe总线的处理器系统如图4-9所示。

图4-9 基于PCIe总线的通用处理器系统

图中所示的结构将PCIe总线端口、存储器控制器等一系列与外部设备有关的接口都集成在一起,并统称为RC。RC具有一个或者多个PCIe端口,可以连接各类PCIe设备。PCIe设备包括EP(如网卡、显卡等设备)、Switch和PCIe桥。

PCIe总线采用端到端的连接方式,每一个PCIe端口只能连接一个EP,当然PCIe端口也可以连接Switch进行链路扩展。通过Switch扩展出的PCIe链路可以继续挂接EP或者其他Switch。

相关文章

(一)经轴架经轴架简称轴架,用来放置经轴,位于浆纱机的后方。经纱从若干经轴上引出合并,以达到工艺要求的总经根数。新型浆纱机的经轴架一般由槽钢立柱和横撑连接而成。图7-40经轴架结构1—经轴 2—轴承座 3—开口滑动轴承4—转动手轮 5—调节螺钉 6—加压夹4.经轴架结构 轴架的结构比较简单,如图7-40所示为G142 型浆纱机的轴架结构图。此后,又经第二浸没辊、第二上浆辊和压浆辊做再次浸浆与压浆。......

2025-09-29

表5-1监控主机功能结构监控主机实现的基本功能包括电网运行监视、操作控制等。具备对全站所有断路器、电动开关、主变有载调压分接头、无功功率补偿装置及与控制运行相关的智能设备的控制及参数设定功能。具备事故紧急控制功能,通过对开关的紧急控制,实现故障区域快速隔离。在满足操作条件的前提下,按照预定的操作顺序自动完成一系列控制功能,宜与智能操作票配合进行。......

2025-09-29

云管理层是云最核心的部分。如图4-2所示,云管理层共有9个模块,这9个模块可分为3层,它们分别是用户层、机制层和检测层。图4-2云管理的架构1.用户层顾名思义,这层主要面向使用云的用户,并通过多种功能来更好地为用户服务,共包含4个模块:用户管理、客户支持、计费管理和服务管理。表4-2机制层模块3.检测层检测层主要监控云计算中心的方方面面,并采集相关数据,以供用户层和机制层使用。......

2025-09-29

如图2-1所示,智能制造系统的整体架构可分为五层。控制系统主要包括适用于流程制造的过程控制系统、适用于离散制造的单元控制系统和适用于运动控制的数据采集与监控系统。图2-1智能制造系统架构3.PLM系统层它主要分为研发设计、生产和服务三个环节。......

2025-09-29

20世纪80年代初期,一个结构完整的生产资源规划及执行控制系统,即所谓的闭环MRP诞生了。制造资源计划是一种以物料需求计划为核心的企业生产管理计划系统。MRP Ⅱ管理系统经过扩充与进一步完善从而发展成为ERP。它是站在全球市场环境下,从企业全局角度对经营与生产进行计划,是制造企业的综合的集成经营系统。IJT的核心是适时、适量生产。......

2025-09-29

新学习系统包含的具体模块主要有分层学习、两卡·两本、导助系统和多向支持等。图2-2是新学习系统的整体架构,从图示中可以看出,新学习系统包括了图2-2 新学习系统的整体架构(一)教学组织:分层学习分层教学是教师根据学生现有的知识、能力水平和潜力倾向把学生科学地分成几组水平相近的群体并区别对待,这些群体在恰当的分层策略和相互合作中得到最好的发展和提高。......

2025-09-29

相关推荐