源代码3-3 软件预读机制的改进程序对于以上这个例子,采用这种预读方法可以有效提高执行效率,对此有兴趣的读者可以对以上几个程序进行简单的对比测试。源代码3-4 软件预读机制的改进程序还可以对ip、数据a和b进行充分预读之后,再一边预读数据,一边计算ip的值,最后计算ip的最终结果。......

2023-10-20

在一个处理器系统中,预读的目标设备并不仅限于存储器,程序员还可以根据实际需要对外部设备进行预读。但并不是所有的外部设备都支持预读,只有“well-behavior”存储器支持预读。处理器使用的内部存储器,如基于SDRAM、DDR-SDRAM或者SRAM的主存储器是“well-behavior”存储器,有些外部设备也是“well-behavior”存储器。这些well-behav-ior存储器具有以下特点。

(1)对这些存储器设备进行读操作时不会改变存储器的内容。显然主存储器具有这种性质。如果一个主存储器的一个数据为0,那么读取这个数据100次也不会将这个结果变为1。但是在外部设备中,一些使用存储器映像寻址的寄存器具有读清除的功能。比如某些中断状态寄存器[51]。当设备含有未处理的中断请求时,该寄存器的中断状态位为1,对此寄存器进行读操作时,硬件将自动地把该中断位清零,这类采用存储映像寻址的寄存器就不是well-behavior存储器。

(2)对“well-behavior”存储器的多次读操作,可以合并为一次读操作。如向这个设备的地址n,n+4,n+8和n+12地址处进行四个双字的读操作,可以合并为对n地址的一次突发读操作(大小为4个双字)。

(3)对“well-behavior”存储器的多次写操作,可以合并为一次写操作。如向这个设备的地址n,n+4,n+8和n+12地址处进行四个双字的写操作,可以合并为对n地址的一次突发写操作。对于主存储器,进行这种操作不会产生副作用,但是对于有些外部设备,不能进行这种操作。

(4)对“well-behavior”的存储器写操作,可以合并为一次写操作。向这个设备的地址n,n+1,n+2和n+3地址处进行四个单字的写操作,可以合并为对n地址的一次DW写操作。对主存储器进行这种操作不会出现错误,但是对于有些外部设备,不能进行这种操作。

如果外部设备满足以上四个条件,该外部设备被称为“well-behavior”。PCI配置空间的BAR寄存器中有一个“Prefectchable”位,该位为1时表示这个BAR寄存器所对应的存储器空间支持预读。PCI总线的预读机制需要HOST主桥、PCI桥和PCI设备的共同参与。在PCI总线中,预读机制需要分两种情况进行讨论,一个是HOST处理器通过HOST主桥和PCI桥访问最终的PCI设备;另一个是PCI设备使用DMA机制访问存储器。

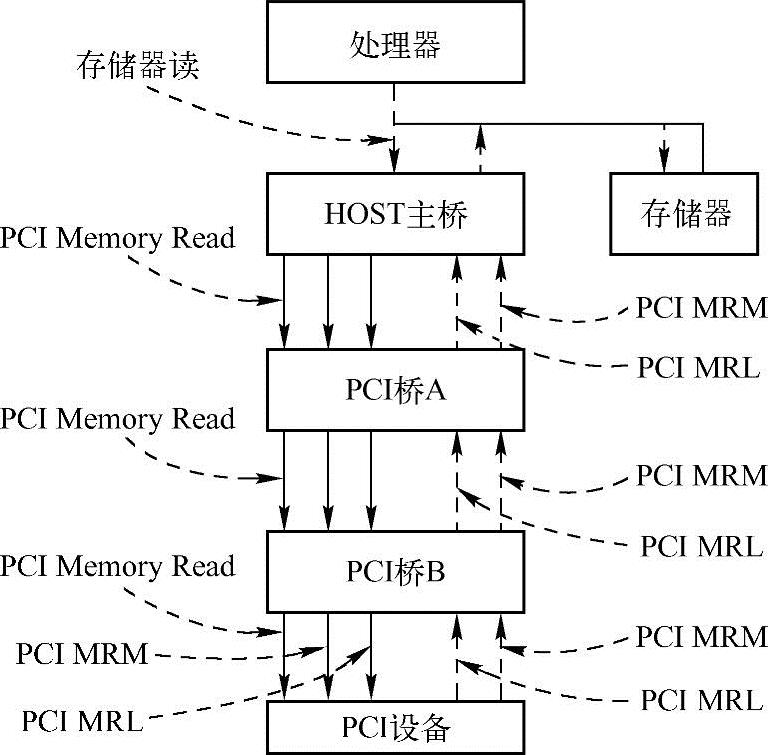

PCI总线预读机制的拓扑结构如图3-12所示。

图3-12 PCI总线的预读

由上图所示,HOST处理器预读PCI设备时,需要经过HOST主桥,并可能通过多级PCI桥,最终到达PCI设备,在这个数据传送路径上,有的PCI桥支持预读,有的不支持预读。而PCI设备对主存储器进行预读时也将经过多级PCI桥。PCI设备除了可以对主存储器进行预读之外,还可以预读其他PCI设备,但是这种情况在实际应用中极少出现,本节仅介绍PCI设备预读主存储器这种情况。

1.HOST处理器预读PCI设备

PCI设备的BAR寄存器可以设置预读位,首先支持预读的BAR寄存器空间必须是一个Well-behavior的存储器空间,其次PCI设备必须能够接收来自PCI桥和HOST主桥的MRM(Memory Read Multiple)和MRL(Memory Read Line)总线事务。

如果PCI设备支持预读,那么当处理器对这个PCI设备进行读操作时,可以通过PCI桥启动预读机制(该PCI桥也需要支持预读),使用MRM和MRL总线事务,对PCI设备进行预读,并将预读的数据暂时存放在PCI桥的预读缓冲中。

之后当PCI主设备继续读取PCI设备的BAR空间时,如果访问的数据在PCI桥的预读缓冲中,PCI桥可以不对PCI设备发起存储器读总线事务,而是直接从预读缓冲中获取数据,并将其传递给PCI主设备。当PCI主设备完成读总线事务后,PCI桥必须丢弃预读的数据以保证数据的完整性。此外当PCI桥预读的地址空间超越了PCI设备可预读BAR空间边界时,PCI设备需要“disconnect”该总线事务。

如果PCI桥支持“可预读”的存储器空间,而且其下挂接的PCI设备BAR空间也支持预读时,系统软件需要从PCI桥“可预读”的存储器空间中为该PCI设备分配空间。此时PCI桥可以将从PCI设备预读的数据暂存在PCI桥的预读缓冲中。

PCI总线规定,如果下游PCI桥地址空间支持预读,则其上游PCI桥地址空间既可以支持也可以不支持预读机制。如图3-12所示,如果PCI桥B管理的PCI子树使用了可预读空间时,PCI桥A可以不支持可预读空间,此时PCI桥A只能使用存储器读总线事务读取PCI设备,而PCI桥B可以将这个存储器读总线事务转换为MRL或者MRM总线事务,预读PCI设备的BAR空间(如果PCI设备的BAR空间支持预读),并将预读的数据保存在PCI桥B的数据缓冲中。

但是PCI总线不允许PCI桥A从其“可预读”的地址空间中,为PCI桥B的“不可预读”区域预留空间,因为这种情况将影响数据的完整性。(www.chuimin.cn)

大多数HOST主桥并不支持对PCI设备的预读,这些HOST主桥并不能向PCI设备发出MRL或者MRM总线事务。由于在许多处理器系统中,PCI设备是直接挂接到HOST主桥上的,如果连HOST主桥也不支持这种预读,即便PCI设备支持了预读机制也没有实际作用。而且如果PCI设备支持预读机制,硬件上需要增加额外的开销,这也是多数PCI设备不支持预读机制的原因。

尽管如此本节仍需要对HOST处理器预读PCI设备进行探讨。假设在图3-12所示的处理器系统中,HOST主桥和PCI桥A不支持预读,而PCI桥B支持预读,而且处理器的Cache行长度为32B(0x20)。

如果HOST处理器对PCI设备的0x8000-0000~0x8000-0003这段地址空间进行读操作时。HOST主桥将使用存储器读总线事务读取PCI设备的“0x8000-0000~0x8000-0003这段地址空间”,这个存储器读请求首先到达PCI桥A,并由PCI桥A转发给PCI桥B。

PCI桥B发现“0x8000-0000~0x8000-0003这段地址空间”属于自己的可预读存储器区域,即该地址区域在该桥的Prefetchable Memory Base定义的范围内,则将该存储器读请求转换为MRL总线事务,并使用该总线事务从PCI设备[52]中读取0x8000-0000~0x8000-001F这段数据,并将该数据存放到PCI桥B的预读缓冲中。MRL总线事务将从需要访问的PCI设备的起始地址开始,一直读到当前Cache行边界。

之后当HOST处理器读取0x8000-0004~0x8000-001F这段PCI总线地址空间的数据时,将从PCI桥B的预读缓冲中直接获取数据,而不必对PCI设备进行读取。

2.PCI设备读取存储器

PCI设备预读存储器地址空间时,需要使用MRL或者MRM总线事务。与MRL总线周期不同,MRM总线事务将从需要访问的存储器起始地址开始,一直读到下一个Cache行边界为止。

对于一个Cache行长度为32B(0x20)的处理器系统,如果一个PCI设备对主存储器的0x1000-0000~0x1000-0007这段存储器地址空间进行读操作时,由于这段空间没有跨越Cache行边界,此时PCI设备将使用MRL总线事务对0x1000-0000~0x1000-001F这段地址区域发起存储器读请求。

如果一个PCI设备对主存储器的0x1000-001C~0x1000-0024这段存储器地址空间进行读操作时,由于这段空间跨越了Cache行边界,此时PCI设备将使用MRM总线事务对0x1000-001C~0x1000-002F这段地址空间发起存储器读请求。

在图3-12所示的例子中,PCI设备读取0x1000-001C~0x1000-0024这段存储器地址空间时,首先将使用MRM总线事务发起读请求,该请求将通过PCI桥B和A最终到达HOST主桥。HOST主桥将从主存储器中读取0x1000-001C~0x1000-002F这段地址空间的数据[53]。如果PCI桥A也支持下游总线到上游总线的预读,这段数据将传递给PCI桥A;如果PCI桥A和B都支持这种预读,这段数据将到达PCI桥B的预读缓冲。

如果PCI桥A和B都不支持预读,0x1000-0024~0x1000-002F这段数据将缓存在HOST主桥中,HOST主桥仅将0x1000-001C~0x1000-0024这段数据通过PCI桥A和B传递给PCI设备。之后当PCI设备需要读取0x1000-0024~0x1000-002F这段数据时,该设备将根据不同情况,从HOST主桥、PCI桥A或者B中获取数据而不必读取主存储器。值得注意的是,PCI设备在完成一次数据传送后,暂存在HOST主桥中的预读数据将被清除。PCI设备采用这种预读方式,可以极大提高访问主存储器的效率。

PCI总线规范有一个缺陷,就是目标设备并不知道源设备究竟需要读取或者写入多少个数据。例如PCI设备使用DMA读方式从存储器中读取4KB大小的数据时,只能通过PCI突发读方式,一次读取一个或者多个Cache行。

假定PCI总线一次突发读写只能读取32B大小的数据,此时PCI设备读取4KB大小的数据,需要使用128次突发周期才能完成全部数据传送。而HOST主桥只能一个一个地处理这些突发传送,从而存储器控制器并不能准确预知何时PCI设备将停止读取数据。在这种情况下,合理地使用预读机制可以有效地提高PCI总线的数据传送效率。

我们首先假定PCI设备一次只能读取一个Cache行大小的数据,然后释放总线,之后再读取一个Cache行大小的数据。如果使用预读机制,虽然PCI设备在一个总线周期内只能获得一个Cache行大小的数据,但是HOST主桥仍然可以从存储器获得2个Cache行以上的数据,并将这个数据暂存在HOST主桥的缓冲中,之后PCI设备再发起突发周期时,HOST主桥可以不从存储器,而是从缓冲中直接将数据传递给PCI设备,从而降低了PCI设备对存储器访问的次数,提高了整个处理器系统的效率。

以上描述仅是实现PCI总线预读的一个例子,而且仅仅是理论上的探讨。实际上绝大多数半导体厂商都没有公开HOST主桥预读存储器系统的细节,在多数处理器中,HOST主桥以Cache行为单位读取主存储器的内容,而且为了支持PCI设备的预读功能HOST主桥需要设置必要的缓冲部件,这些缓冲的管理策略较为复杂。

目前PCI总线已经逐渐退出历史舞台,进一步深入研究PCI桥和HOST主桥,意义并不太大,不过读者依然可以通过学习PCI体系结构,获得处理器系统中有关外部设备的必要知识,并以此为基础,学习PCIe体系结构。

有关PCI Express体系结构导读的文章

源代码3-3 软件预读机制的改进程序对于以上这个例子,采用这种预读方法可以有效提高执行效率,对此有兴趣的读者可以对以上几个程序进行简单的对比测试。源代码3-4 软件预读机制的改进程序还可以对ip、数据a和b进行充分预读之后,再一边预读数据,一边计算ip的值,最后计算ip的最终结果。......

2023-10-20

在一段程序中,存在大量的分支预测指令,因而在某种程度上增加了指令Fetch的难度。但是分支预测单元并不会每次都能正确判断分支指令的执行路径,这为指令Fetch制造了不小的麻烦,在这个背景下许多分支预测策略应运而生。在PowerPC处理器中,条件转移指令“bc”表示Taken;而“bc-”表示Not Taken。BTB的功能相当于存放转移指令的Cache,其状态机转换也与Cache类似。转移指令B执行完毕后,将实际执行结果Rc更新到BHR寄存器中,并同时更新PHT中对应的Entry。......

2023-10-20

填写RD_DMA_SIZE寄存器,以字节为单位。填写DCSR2寄存器的mrd_start位,启动DMA读。等待DMA读完成中断产生后,结束DMA读。从硬件设计的角度来看,DMA读过程比DMA写过程复杂。Capric卡的1次DMA读操作使用两种TLP报文,并通过发送部件和接收部件协调完成。如果一次DMA读请求的数据大于512B[84]时,DMA控制逻辑需要发送多个存储器读请求TLP给RC,而且在DMA读操作中需要进行数据对界。DMA读操作的详细实现过程见第12.2.2节。......

2023-10-20

如图8-6所示,Detect状态由Detect.Quiet、Detect.Active两个子状态组成。在正常情况下,PCIe链路将从Detect状态迁移到Polling状态。而在Detect状态中,PCIe设备的发送逻辑TX将直接进入到“Electrical Idle”状态,并不会使用Idle序列通知对端设备的接收逻辑RX。当PCIe设备处于Detect.Quiet状态超过12ms之后,或者检测到PCIe链路上的任何一个Lane退出“Electrical Idle”状态时,PCIe设备将进入Detect.Active状态。......

2023-10-20

此时PCI桥首先Retry当前Non-Posted总线事务,并将其转换为Delayed总线事务。使用Delayed总线请求事务进行数据传送时,需要遵循以下规则。而这些重试操作极大浪费了PCI总线的带宽,这也是Delayed总线事务的缺点。此时这个Delayed总线完成事务除了在以下两种情况之外,不能被随便丢弃。PCI桥在处理Delayed总线事务时,必须能够接收来自这个桥同一侧的Posted存储器写请求。因为Delayed读总线事务A有可能被设备使用重试周期结束。......

2023-10-20

目前虚拟化技术在处理器体系结构中,已经占据一席之地。本章所强调的虚拟化技术是指在一个处理器系统[109]中运行多个虚拟处理器系统的技术。因此处理器需要为虚拟化环境设置专门的硬件,以支持多个虚拟处理器系统在一个物理环境中的资源共享。虚拟化技术的核心是通过VMM集中管理物理资源,而每个虚拟处理器系统通过VMM访问实际的物理资源。本章重点关注的是VMM对外部设备的管理,而在外部设备中重点关注对PCI设备的管理。......

2023-10-20

而PCI总线的突发传送仍然存在缺陷。为此PCI-X总线使用基于数据块的突发传送方式,发送端以ADB为单位,将数据发送给接收端,一次突发读写为一个以上的ADB。采用这种方式,接收端可以事先预知是否有足够的接收缓冲,接收来自发送端的数据,从而可以及时断连当前总线周期,以节约PCI-X总线的带宽。因此在PC领域和嵌入式领域很少有基于PCI-X总线的设备,PCI-X设备仅在一些高端服务器上出现。因此本节不对PCI-X总线做进一步描述。......

2023-10-20

MSI Capability结构共有四种组成方式,分别是32和64位的Message结构,32位和64位带中断Masking的结构。MSI Capability寄存器的结构如图10-1所示。图10-1 MSI Capability结构●Capability ID字段记载MSI Capability结构的ID号,其值为0x05。表10-1 MSI Cabalibities结构的Message Control字段[67] 此时PCI设备配置空间Command寄存器的“Interrupt Disable”位为1。当MSI En able位有效时,该字段存放MSI报文使用的数据。该字段需要与Mask Bits字段联合使用。......

2023-10-20

相关推荐