对执行过程进行检查和监督,能够保证在规定期限内完成既定目标。因此,不断完善执行检查机制,能够保证执行目标的实现。执行检查机制是对于执行过程中所有事项按照既定标准进行的跟踪检查,以此来明确各个环节及人员的职责明细,促进执行的落实,增强团队成员的执行力。执行检查机制可以对执行过程中出现的问题进行及时有效的解决,避免问题的积压造成执行环节的不流畅。......

2023-07-26

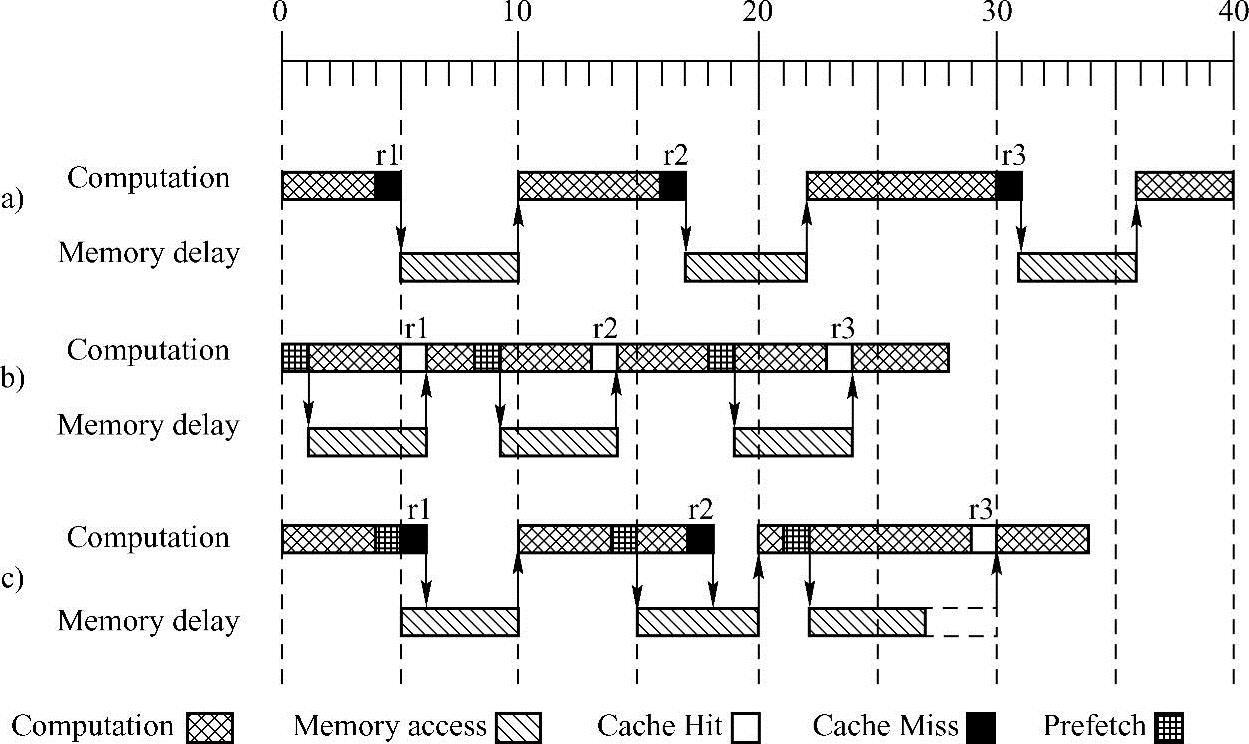

数据预读是指在处理器进行运算时,提前通知存储器系统将运算过程中需要的数据准备好,而当处理器需要这些数据时,可以直接从这些预读缓冲(通常指Cache)中获得这些数据。Steven P.Vanderwiel与David J.Lilja总结了最近出现的各类数据预读机制,下面将以图3-11为例进一步探讨这些数据预读机制。

图3-11 数据预读机制示意图

图3-11列举了三个实例说明数据预读的作用。其中实例a没有使用预读机制;实例b是一个采用预读机制的理想情况;而实例c是一个采用预读机制的次理想情况。我们假设处理器执行某个任务需要经历四个阶段,每个阶段都由处理器执行运算指令和存储指令组成。而处理器一次存储器访问需要5个时钟周期。其中每一个阶段的定义如下所示。

(1)处理器执行4个时钟周期后需要访问存储器。

(2)处理器执行6个时钟周期后需要访问存储器。

(3)处理器执行8个时钟周期后需要访问存储器。

(4)处理器执行4个时钟周期后完成。

实例a由于没有使用预读机制,因此在运算过程中需要使用存储器中的数据时,不可避免地出现Cache Miss。实例a执行上述任务的过程如下。

(1)执行第一阶段任务的4个时钟周期,之后访问存储器,此时将发生Cache Miss。

(2)Cache Miss需要使用一个时钟周期[44],然后在第5个时钟周期启动存储器读操作。

(3)在第10个周期,处理器从存储器获得数据,继续执行第二阶段任务的6个时钟周期,之后访问存储器,此时也将发生Cache Miss。

(4)处理器在第17~22时钟周期从存储器读取数据,并在第22个时钟周期继续执行第三阶段任务的8个时钟周期,之后访问存储器,此时也将发生Cache Miss。(www.chuimin.cn)

(5)处理器在第31~36时钟周期从存储器读取数据,并在第36个时钟周期继续执行第四阶段任务的4个时钟周期,完成整个任务的执行。

采用这种机制执行上述任务共需40个时钟周期。而使用预读机制,可以有效缩短整个执行过程,如图3-11中的实例b所示。在实例b中在执行过程中,都会提前进行预读操作,虽然这些预读操作也会占用一个时钟周期,但是这些预读操作是值得的。合理使用这些数据预读,完成同样的任务CPU仅需要28个时钟周期,从而极大提高了程序的执行效率,其执行过程如下。

(1)首先使用预读指令对即将使用的存储器进行预读[45],然后执行第一阶段任务的4个时钟周期。当处理器进行存储器读时,数据已经准备好,处理器将在Cache中获得这个数据然后继续执行[46]。

(2)处理器在执行第二阶段的任务时,先执行2个时钟周期之后进行预读操作,最后执行剩余的4个时钟周期。当处理器进行存储器读时,数据已经准备好,处理器将在Cache中获得这个数据然后继续执行。

(3)处理器执行第三阶段的任务时,先执行4个时钟周期之后进行预读操作,最后执行剩余的4个时钟周期。当处理器进行存储器读时,数据已经准备好,处理器将在Cache中获得这个数据然后继续执行。

(4)处理器执行第四阶段的任务,执行完4个时钟周期后,完成整个任务的执行。

当然这种情况是非常理想的,处理器在执行整个任务时,从始至终是连贯的,处理器执行和存储器访存完全并行,然而这种理想情况并不多见。

首先在一个任务的执行过程中,并不易确定最佳的预读时机;其次采用预读所获得数据并不一定能够被及时利用,因为在程序执行过程中可能会出现各种各样的分支选择,有时预读的数据并没有被及时使用。

在图3-11所示的实例c中,预读机制没有完全发挥作用,所以处理器在执行任务时,Cache Miss时有发生,从而降低了整个任务的执行效率。即便这样,实例c也比完全没有使用预读的实例a的任务执行效率高一些。在实例c中,执行完毕图3-11中所示的任务共需要34个时钟周期。

但是在某些特殊情况下,采用预读机制有可能会降低效率。首先在一个较为复杂的应用中,很有可能预读的数据没有被充分利用,一个程序可能会按照不同的分支执行,而执行每一个分支所使用的数据并不相同。其次预读的数据即使是有效的,这些预读的数据也会污染整个Cache资源,在大规模并行任务的执行过程中,有可能引发Cache颠簸,从而极大地降低系统效率。

什么时候采用预读机制,关系到处理器系统结构的每一个环节,需要结合软硬件资源统筹考虑,并不能一概而论。处理器提供了必备的软件和硬件资源用以实现预读,而如何“合理”使用预读机制是系统程序员考虑的一个细节问题。数据预读可以使用软件预读或者硬件预读两种方式实现,下文将详细介绍这两种实现方式。

有关PCI Express体系结构导读的文章

对执行过程进行检查和监督,能够保证在规定期限内完成既定目标。因此,不断完善执行检查机制,能够保证执行目标的实现。执行检查机制是对于执行过程中所有事项按照既定标准进行的跟踪检查,以此来明确各个环节及人员的职责明细,促进执行的落实,增强团队成员的执行力。执行检查机制可以对执行过程中出现的问题进行及时有效的解决,避免问题的积压造成执行环节的不流畅。......

2023-07-26

PCI总线的预读机制需要HOST主桥、PCI桥和PCI设备的共同参与。PCI总线预读机制的拓扑结构如图3-12所示。当PCI主设备完成读总线事务后,PCI桥必须丢弃预读的数据以保证数据的完整性。PCI总线规定,如果下游PCI桥地址空间支持预读,则其上游PCI桥地址空间既可以支持也可以不支持预读机制。但是PCI总线不允许PCI桥A从其“可预读”的地址空间中,为PCI桥B的“不可预读”区域预留空间,因为这种情况将影响数据的完整性。......

2023-10-20

最高人民法院裁判的知识产权案件中有关法律适用问题的阐释,对于全国法院知识产权司法保护工作具有指导和借鉴意义。知识产权刑事审判制裁和预防侵犯知识产权犯罪的职能作用进一步发挥。最后,依法履行对知识产权行政行为的司法审查职责,充分发挥监督和支持知识产权行政执法保护的职能。2016年,上海知识产权法院受理各类知识产权案件1877件,同比上升14.38%。......

2023-08-04

源代码3-3 软件预读机制的改进程序对于以上这个例子,采用这种预读方法可以有效提高执行效率,对此有兴趣的读者可以对以上几个程序进行简单的对比测试。源代码3-4 软件预读机制的改进程序还可以对ip、数据a和b进行充分预读之后,再一边预读数据,一边计算ip的值,最后计算ip的最终结果。......

2023-10-20

图5.14过滤器的符号过滤器的主要性能参数过滤器的主要性能参数有过滤精度、过滤比和过滤能力等。国际标准ISO4572 推荐过滤比的测试方法是:在油箱中不断加入某种规格的污染物(试剂),液压泵从油箱中吸油,输出的油液通过被测过滤器,然后回油箱;测量过滤器入口与出口处污染物的数量,即得到过滤比。最常用的有网式和线隙式过滤器两种。此种过滤器结构简单,清洗方便。如图5.15所示为线隙式过滤器。......

2023-06-20

特别是在沙巴特循环中其倾向更加明显。这是因为在沙巴特循环中,如果λ增大,不但随质量热容的减小使热效率增加,还因燃料定压预胀比φ减小,即接近于1,进一步提高了热效率。......

2023-06-28

采用硬件预读的优点是不需要软件进行干预,也不需要浪费一条预读指令来进行预读。在许多处理器中这种硬件预读通常与指令预读协调工作。硬件预读机制的历史比软件预读更为久远,在IBM 370/168处理器系统中就已经支持硬件预读机制。大多数硬件预读仅支持存储器到Cache的预读,并在程序执行过程中,利用数据的局部性原理进行硬件预读。......

2023-10-20

分布式簿记或称分布式账本,是一个在网络成员之间共享、复制和同步的分布式数据库。分布式簿记用于记录网络参与者之间的交易。分布式账本技术的出现可能是账本技术继数字化之后的又一次重大飞跃。UTXO模式实际上是以编码的方式难以篡改地记录了所有交易信息。DLT对传统账本技术的改进表示在以下两方面。DLT从技术层面着手,采用签名加密等技术手段,将数据权利真正交还给个体。......

2023-10-28

相关推荐