本书将PCIe-to-PCI/PCI-X桥片简称为PCIe桥片。许多PowerPC处理器在提供PCIe总线的同时,也提供了PCI总线,因此PCIe-to-PCI桥片对基于PowerPC处理器系统并不是必须的。其中可以连接多个PCI总线的PCIe桥也被称为多端口PCIe桥。PCIe总线规范并没有强制厂商实现多端口PCIe桥的办法。目前多端口PCIe桥多使用右图进行端口扩展。......

2023-10-20

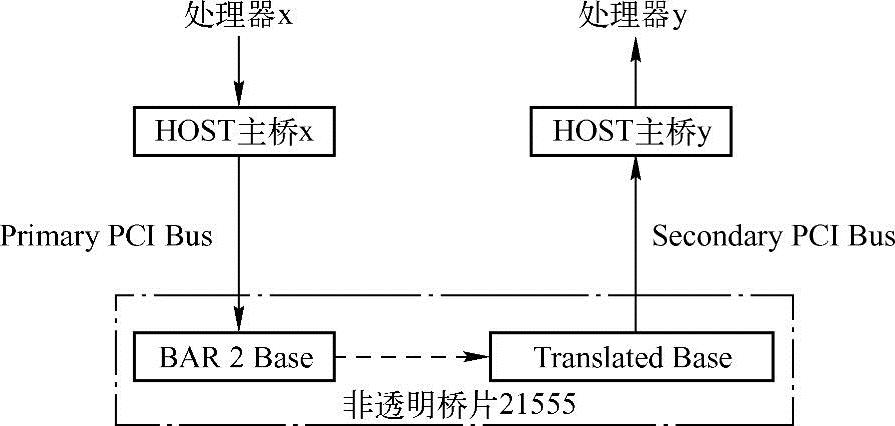

下面以图2-16中处理器x访问处理器y存储器地址空间的实例,说明非透明桥21555如何将PCI总线x域与PCI总线y域联系在一起。

处理器x在访问处理器y的存储器空间之前,需要做一些必要的准备工作。

(1)首先确定由哪一个BAR寄存器空间映射处理器y的存储器地址空间。本节假定使用BAR2寄存器映射处理器y的存储器地址空间。

(2)BAR2寄存器使用Downstream Memory 2 Translated Base寄存器,将来自Primary PCI总线的访问转换为对Secondary PCI总线地址空间的访问。其中Downstream Memory 2 Transla-ted Base寄存器可以由处理器x或者处理器y根据需要进行设置。

假定处理器x和y的HOST主桥使用“直接相等”策略,建立存储器域与PCI总线域间的映射;而处理器x使用BAR2地址空间访问处理器y存储器空间0x1000-000~0x1FFF-FFFF;处理器x的系统软件事先将BAR2寄存器设置完毕。处理器x访问处理器y的这段存储器空间的步骤如下,读者可参考图2-18理解以下步骤。

(1)首先处理器x访问在处理器x域中,且与非透明桥的BAR2空间相对应的存储器地址空间。

(2)HOST主桥将进行存储器域到PCI总线域的转换,并将这个请求发送到Primary PCI总线上。

(3)非透明桥发现这个数据请求发向BAR2地址空间,则接收这个数据请求,并在桥片中暂存这个数据请求。(www.chuimin.cn)

(4)非透明桥根据Downstream Memory 2 Translated Base寄存器的内容,按照图2-17所示的规则进行地址转换。假设Downstream Memory 2 Translated Base寄存器的基地址被预先设置为0x1000-0000,大小为256MB(这个物理地址属于处理器y的主存储器地址空间)。

(5)经过非透明桥的转换后,这个数据请求将穿越非透明桥,从Primary PCI总线域进入Secondary PCI总线域,然后访问处理器y的基地址为0x1000-0000的存储器区域。

(6)处理器y的HOST主桥接收这个存储器访问请求,并最终将数据请求发向处理器y的存储器中。

图2-18 通过非透明桥21555进行数据传递

非透明桥21555除了可以支持存储器到存储器之间的数据传递,还支持PCI总线域到存储器域,以及PCI总线域之间的数据传递,此外非透明桥21555还可以通过I2O和Doorbell寄存器进行Primary PCI总线与Secondary PCI总线之间的中断信号传递。本节对这部分内容不做进一步介绍。

非透明桥有效解决了使用PCI总线连接两个处理器存在的问题,因而得到了广泛的应用。在PCIe体系结构中,也存在非透明PCI桥的概念。如在PLX的Switch芯片中,各个端口都可以设置为非透明模式。

有关PCI Express体系结构导读的文章

本书将PCIe-to-PCI/PCI-X桥片简称为PCIe桥片。许多PowerPC处理器在提供PCIe总线的同时,也提供了PCI总线,因此PCIe-to-PCI桥片对基于PowerPC处理器系统并不是必须的。其中可以连接多个PCI总线的PCIe桥也被称为多端口PCIe桥。PCIe总线规范并没有强制厂商实现多端口PCIe桥的办法。目前多端口PCIe桥多使用右图进行端口扩展。......

2023-10-20

采用非透明桥将有效解决以上这些问题,非透明桥并不是PCI总线定义的标准桥片,但是这类桥片在连接两个处理器系统中得到了广泛的应用。从图2-16中我们可以发现非透明桥可以将PCI总线x域与PCI总线y域进行隔离。为此非透明PCI桥需要对分属不同PCI总线域的地址空间进行转换。值得注意的是,在PCIe体系结构中,也存在非透明PCI桥的概念。......

2023-10-20

PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX和RX,其结构如图4-1所示。目前PCIe总线的最新规范为V2.1,而V3.0正在开发,预计在2010年发布。PCIe总线V1.x和V2.0规范在物理层中使用8/10b编码,即在PCIe链路上的10bit中含有8位的有效数据;而V3.0规范使用128/130b编码方式,即在PCIe链路上的130bit中含有128位的有效数据。PCIe总线也有其弱点,其中最突出的问题是传送延时。......

2023-10-20

下面以图3-2所示的处理器系统为例,说明处理器向PCI设备11进行存储器写的数据传送过程。PCI设备11在PCI总线域的地址范围是0x7300-0000~0x73FF-FFFF。存储器域将0xF300-0008这个地址发向HOST主桥,0xF000-0000~0xF7FF-FFFF这段地址已经由HOST主桥映射到PCI总线域地址空间,所以HOST主桥认为这是一个对PCI设备的访问。PCI总线0的PCI桥1发现0x7300-0008在自己管理的地址范围内,于是接管这个存储器写请求,并通过总线仲裁逻辑获得PCI总线1的使用权,并将这个请求转发到PCI总线1上。......

2023-10-20

本小节主要介绍这类透明盖板材料的辐射特性。图3-14 在两种介质交界面上的投射及折射设有一块厚度为L的半透明介质,在x=0处的光谱辐射强度为Ib,0,现要确定通过L后的光谱辐射强度Ib,λ,如图3-15所示。显然,厚度为L的半透明介质的光谱透射率τλ为上式称为布格尔定律。......

2023-06-23

而桥设备的主要作用是管理下游的PCI总线,并转发上下游总线之间的总线事务。PCI总线规范将PCI主从设备统称为PCI Agent设备。PCI规范也没有规定如何设计HOST主桥。在PCI总线中,还有一类特殊的设备,即桥设备。本书重点介绍PCI桥,而不介绍其他桥设备的实现原理。PCI桥的出现使得采用PCI总线进行大规模系统互连成为可能。其中对PCI设备配置空间的访问可以从上游总线转发到下游总线,而数据传送可以双方向进行。......

2023-10-20

在PCI桥的配置空间中使用两个BAR寄存器的原因是这两个32位的寄存器可以组成一个64位地址空间。在PCI桥的配置空间中,有许多寄存器是PCI桥所特有的。图2-10 PCI桥的配置空间在PCI桥中,与Secondary bus相关的寄存器包括两大类。......

2023-10-20

块茎结构的非中心性,是没有开头、没有结尾的,它有一个范围,因此,从性质上说,它是可以无限地连接下去。参与者的互动与块茎之间信息的传递,导致块茎之间结构的全新组合,在不断发展的动态中生成。如果块茎内部存储着树状结构,此块茎则具有其独立的时空观,受到外界的介入与影响,树状结构随时会被打断。表2-1树状结构与块茎结构的差异......

2023-11-24

相关推荐