PCI总线树的枚举由pci_scan_child_bus函数完成,该函数的主要作用是分配PCI总线树的PCI总线号,而并不初始化PCI设备使用的BAR空间。subordinate总线号记载当前PCI总线树中最后一个PCI总线号,因此只有完成了对PCI总线树的枚举后,才能获得该参数。值得注意的是,在Linux系统中,许多PCIe设备并没有提供该结构。PCI总线规范规定了获取BAR空间的标准实现方法。......

2023-10-20

一条PCI总线会挂接各种各样的PCI设备,而每一个PCI设备在PCI总线下具有唯一的设备号。系统软件通过总线号和设备号定位一个PCI设备之后,才能访问这个PCI设备的配置寄存器。值得注意的是,系统软件使用“地址寻址方式”访问PCI设备的存储器和I/O地址空间,这与访问配置空间使用的“ID寻址方式”不同。

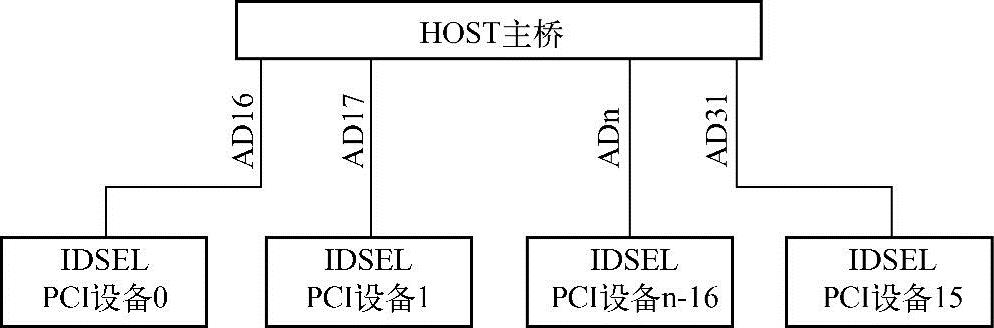

PCI设备的IDSEL信号与PCI总线的AD[31∶0]信号的连接关系决定了该设备在这条PCI总线的设备号。如上文所述,每一个PCI设备都使用独立的IDSEL信号,该信号将与PCI总线的AD[31∶0]信号连接,IDSEL信号的含义见第1.2.2节。

在此我们简要回顾PCI的配置读写事务使用的时序。如图1-3所示,PCI总线事务由一个地址周期加若干个数据周期组成。在进行配置读写请求总线事务时,C/BE#信号线的值在地址周期中为0x1010或者为0x1011,表示当前总线事务为配置读或者配置写请求。此时出现在AD[31∶0]总线上的值并不是目标设备的PCI总线地址,而是目标设备的ID号,这与PCI总线进行I/O或者存储器请求时不同,因为PCI总线使用ID号而不是PCI总线地址对配置空间进行访问。

如图2-12所示,在配置读写总线事务的地址周期中,AD[10∶0]信号已经被Function Number和Re gister Number使用,因此PCI设备的IDSEL只能与AD[31∶11]信号连接。

认真的读者一定可以发现在CONFIG_ADDRESS寄存器中Device Number字段一共有5位可以表示32个设备,而AD[31∶11]只有21位,显然在这两者之间无法建立一一对应的映射关系。因此在一条PCI总线上如果有21个以上的PCI设备,那么总是有几个设备无法与AD[31∶11]信号线连接,从而PCI总线无法访问这些设备。因为PCI总线在配置请求的地址周期中,只能使用第31~11这些AD信号,所以在一条总线上最多也只能挂接21个PCI设备。这21个设备可能是从0到20,也可能是从11到31排列。从而系统软件在遍历PCI总线时,还是需要从0到31遍历整条PCI总线。

在实际的应用中,一条PCI总线能够挂接21个设备已经足够了,实际上由于PCI总线的负载能力有限,即便在总线频率为33MHz的情况下,在一条PCI总线中最多也只能挂接10个负载,一条PCI总线所能挂接的负载详见表1-1。AD信号线与PCI设备IDSEL线的连接关系如图2-14所示。

(www.chuimin.cn)

(www.chuimin.cn)

图2-14 PCI总线设备号的分配

PCI总线推荐了一种Device Number字段与AD[31∶16]之间的映射关系。其中PCI设备0与Device Number字段的0b00000对应;PCI设备1与Device Number字段的0b00001对应,并以此类推,PCI设备15与De vice Number字段的0b01111对应。

在这种映射关系之下,一条PCI总线中,与信号线AD16相连的PCI设备的设备号为0;与信号线AD17相连的PCI设备的设备号为1;以此类推,与信号线AD31相连的PCI设备的设备号为15。在Type 00h配置请求中,设备号并没有像Function Number和Register Num-ber那样以编码的形式出现在AD总线上,而是与AD信号一一对应,如图2-12所示。

这里有一个原则需要读者注意,就是对PCI设备的配置寄存器进行访问时,一定要有确定的Bus Number、Device Number、Function Number和Register Number,这“四元组”缺一不可。在Type 00h配置请求中,Device Number由AD[31∶11]信号线与PCI设备IDSEL信号的连接关系确定;Function Number保存在AD[10∶8]字段中;而Register Number保存在AD[7∶0]字段中;在Type 01h配置请求中,也有完整的四元组信息。

在一个处理器系统的设计中,如果在一条PCI总线上使用的PCI插槽少于4个时,笔者建议优先使用AD[17∶20]信号与PCI设备的IDSEL信号连接。因为PCI-X总线规范建议使用AD17连接PCI设备1、AD18连接PCI设备2、AD19连接PCI设备3、AD20连接PCI设备4,采用这种方法便于实现PCI总线与PCI-X总线的兼容。

有关PCI Express体系结构导读的文章

PCI总线树的枚举由pci_scan_child_bus函数完成,该函数的主要作用是分配PCI总线树的PCI总线号,而并不初始化PCI设备使用的BAR空间。subordinate总线号记载当前PCI总线树中最后一个PCI总线号,因此只有完成了对PCI总线树的枚举后,才能获得该参数。值得注意的是,在Linux系统中,许多PCIe设备并没有提供该结构。PCI总线规范规定了获取BAR空间的标准实现方法。......

2023-10-20

表11-4 PCI桥使用的数据访问顺序1.Posted存储器写通过PCI桥时需要按序完成Posted存储器写通过PCI桥时需要遵循“先进先出”的原则,否则将会引发数据完整性问题。......

2023-10-20

PCI总线是由Intel公司提出的。PCI总线不是由ANSI通过的标准,但由于它是由厂家自发制定执行的标准,具有众多的优点,拥护者,执行者众多,成了事实上的标准。PCI总线共有100个引脚,如果只作为目标设备,至少需要47条,如作为主设备则需要49条。本设计使用位命令字,其定义如下:3.PCI总线基本协议PCI上的基本总线传输机制是突发成组传输。......

2023-11-22

本章主要讲述在PCI/PCIe总线中,数据传送的“序”与可能出现的死锁。在PCI/PCIe总线中,序与生产/消费者模型密切相关。生产/消费者模型是一种并发协作模型,PCI/PCIe设备使用该模型进行数据传递。在PCI/PCIe总线中,访问“序”的安排必须保证生产/消费者模型的正确运转,这也意味着在PCI/PCIe总线中,数据的传送规则需要与生产/消费者模型一致。而PCI/PCIe总线针对的就是这样的一个通用处理器系统。本章将在第11.3节介绍PCI总线的序,并在第11.4节详细介绍PCIe总线的序。......

2023-10-20

PCI总线规范定义了一系列与Cache相关的总线事务,以提高PCI设备与主存储器进行数据交换的效率,即DMA读写的效率。PCI设备与主存储器进行的Cache共享一致性增加了HOST主桥的设计复杂度。在高性能处理器中Cache状态机的转换模型十分复杂。因为Cache一致性操作不仅与HOST主桥的设计相关,而且主要与处理器和Cache Memory系统设计密切相关。因为x86处理器重点优化的是PCIe设备,目前x86处理器使用的IOAT技术,显著提高了PCIe设备与主存储器进行数据通信的效率。......

2023-10-20

值得注意的是,在不同处理器体系结构中,Linux系统初始化PCI总线的过程并不相同。Linux x86将继承BIOS对PCI总线的初始化成果,并在此基础上进行Linux PCI子系统的初始化,并执行PCI设备的Linux驱动程序的初始化模块。在Linux x86中,PCI总线的初始化由一系列模块协调完成。在Linux PCI中,有两个常用的数据结构,分别为pci_dev和pci_bus结构。......

2023-10-20

Linux PCI采用这种方式,可以保证PCI设备BAR寄存器初始化是从上游PCI总线到下游PCI总线,而PCI桥Base、Limit寄存器的初始化是从下游PCI总线到上游PCI总线。目前Linux系统使用从上游总线到下游总线的方法初始化PCI设备的BAR寄存器。pbus_assign_resources_sorted函数负责分配“未初始化PCI设备的BAR寄存器”,该函数将对这些PCI设备的BAR寄存器进行写操作。......

2023-10-20

系统软件在遍历当前PCI总线树时,需要首先对这些PCI总线进行编号,即初始化PCI桥的Primary、Secondary和Sub-ordinate Bus Number寄存器。扫描PCI总线2,发现PCI桥3,并将PCI桥3的Secondary Bus命名为PCI总线3。继续回退到PCI总线1。从以上算法可以看出,PCI桥的Primary Bus和Secondary Bus号的分配在遍历PCI总线树的过程中从上向下分配,而Subordinate Bus号是从下向上分配的,因为只有确定了一个PCI桥之下究竟有多少条PCI总线后,才能初始化该PCI桥的Subordinate Bus号。......

2023-10-20

相关推荐