【摘要】:Intel采用的南北桥架构针对x86处理器的应用领域而设计,并不能说采用这种结构一定比MPC8548处理器中既含有HOST-to-PCI主桥也含有HOST-to-PCIe主桥更为合理。x86处理器使用这两个I/O端口访问PCI设备的配置空间。本书将在第5章以HOST-to-PCIe主桥为例,详细介绍Intel处理器的存储器地址与PCI总线地址的转换关系,而在本节不对x86处理器的HOST主桥做进一步说明。x86处理器系统的升级速度较快,目前在x86的处理器体系结构中,已很难发现HOST主桥的身影。

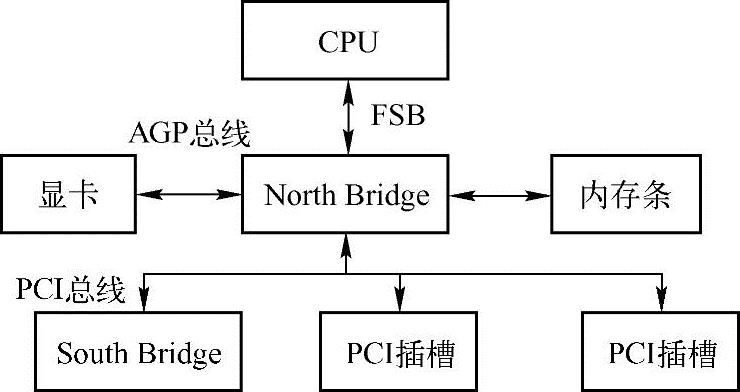

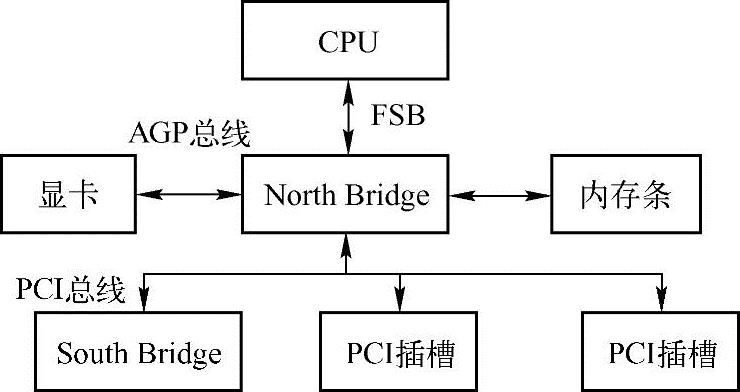

x86处理器使用南北桥结构连接CPU和PCI设备。其中北桥(North Bridge)连接快速设备,如显卡和内存条,并推出PCI总线,HOST主桥包含在北桥中。而南桥(South Bridge)连接慢速设备。x86处理器使用的南北桥结构如图2-6所示。

图2-6 x86处理器的南北桥结构

Intel使用南北桥概念统一PC架构。但是从体系结构的角度上看,南北桥架构并不重要,北桥中存放的主要部件不过是存储器控制器、显卡控制器和HOST主桥而已,而南桥存放的是一些慢速设备,如ISA总线和中断控制器等。

不同的处理器系统集成这些组成部件的方式并不相同,如PowerPC、MIPS和ARM处理器系统通常将CPU和主要外部设备都集成到一颗芯片中,组成一颗基于SoC架构的处理器系统。这些集成方式并不重要,每一个处理器系统都有其针对的应用领域,不同应用领域的需求对处理器系统的集成方式有较大的影响。Intel采用的南北桥架构针对x86处理器的应用领域而设计,并不能说采用这种结构一定比MPC8548处理器中既含有HOST-to-PCI主桥也含有HOST-to-PCIe主桥更为合理。

在许多嵌入式处理器系统中,既含有PCI设备也含有PCIe设备,为此MPC8548处理器同时提供了PCI总线和PCIe总线接口,在这个处理器系统中,PCI设备可以与PCI总线直接相连,而PCIe设备可以与PCIe总线直接相连,因此并不需要使用PCIe桥扩展PCI总线,从而在一定程度上简化了嵌入式系统的设计。

嵌入式系统所面对的应用千变万化,进行芯片设计时所要考虑的因素相对较多,因而在某种程度上为设计带来了一些难度。而x86处理器系统所面对的应用领域针对个人PC和服务器,向前兼容和通用性显得更加重要。在多数情况下,一个通用处理器系统的设计难度超过专用处理器系统的设计,Intel为此付出了极大的代价。

在一些相对较老的北桥中,如Intel 440系列芯片组中包含了HOST主桥,从系统软件的角度上看HOST-to-PCI主桥实现的功能与HOST-to-PCIe主桥实现的功能相近。本节仅简单介绍Intel的HOST-to-PCI主桥如何产生PCI的配置周期,有关Intel HOST-to-PCIe主桥[17]的详细信息参见第5章。

x86处理器定义了两个I/O端口寄存器,分别为CONFIG_ADDRESS和CONFIG_DATA寄存器,其地址为0xCF8和0xCFC。x86处理器使用这两个I/O端口访问PCI设备的配置空间。PCI总线规范也以这两个寄存器为例,说明处理器如何访问PCI设备的配置空间。其中CONFIG_ADDRESS寄存器存放PCI设备的ID号,而CONFIG_DATA寄存器存放进行配置读写的数据。

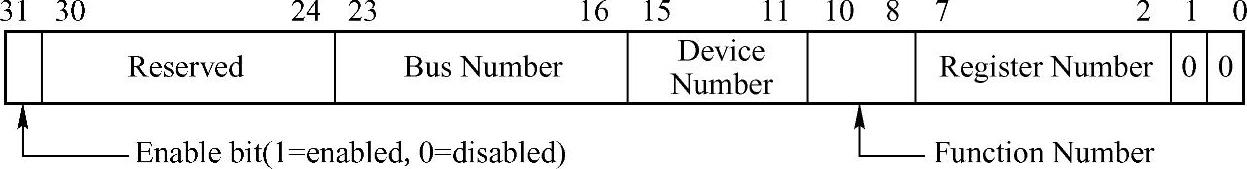

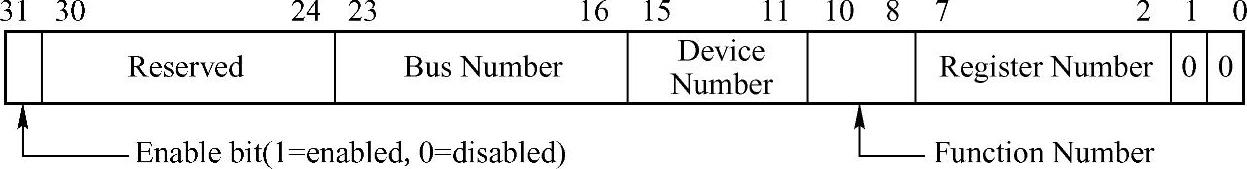

CONFIG_ADDRESS寄存器与PowerPC处理器中的CFG_ADDR寄存器的使用方法类似,而CONFIG_DATA寄存器与PowerPC处理器中的CFG_DATA寄存器的使用方法类似。CON-FIG_ADDRESS寄存器的结构如图2-7所示。

图2-7 CONFIG_ADDRESS寄存器的结构

CONFIG_ADDRESS寄存器的各个字段和位的说明如下所示。(www.chuimin.cn)

●Enable位,第31位。该位为1时,对CONFIG_DATA寄存器进行读写时将引发PCI总线的配置周期。

●Bus Number字段,第23~16位,记录PCI设备的总线号。

●Device Number字段,第15~11位,记录PCI设备的设备号。

●Function Number字段,第10~8位,记录PCI设备的功能号。

●Register Number字段,第7~2位,记录PCI设备的寄存器号。

当x86处理器对CONFIG_DATA寄存器进行I/O读写访问,且CONFIG_ADDR寄存器的Enable位为1时,HOST主桥将这个I/O读写访问转换为PCI配置读写总线事务,然后发送到PCI总线上,PCI总线根据保存在CONFIG_ADDR寄存器中的ID号,将PCI配置读写请求发送到指定PCI设备的指定配置寄存器中。

x86处理器使用小端地址模式,因此从CONFIG_DATA寄存器中读出的数据不需要进行模式转换,这点和PowerPC处理器不同,此外x86处理器的HOST主桥也实现了存储器域到PCI总线域的地址转换,但是这个概念在x86处理器中并不明晰。

本书将在第5章以HOST-to-PCIe主桥为例,详细介绍Intel处理器的存储器地址与PCI总线地址的转换关系,而在本节不对x86处理器的HOST主桥做进一步说明。x86处理器系统的升级速度较快,目前在x86的处理器体系结构中,已很难发现HOST主桥的身影。

目前Inte l对南北桥架构进行了升级,其中北桥被升级为MCH(Memory Controller Hub),而南桥被升级为ICH(I/O Controller Hub)。x86处理器系统在MCH中集成了存储器控制器、显卡芯片和HOST-to-PCIe主桥,并通过Hub Link与ICH相连;而在ICH中集成了一些相对低速总线接口,如AC′97、LPC(Low Pin Count)、IDE和USB总线,当然也包括一些低带宽的PCIe总线接口。

在Intel最新的Nehalem[18]处理器系统中,MCH被一分为二,存储器控制器和图形控制器已经与CPU内核集成在一个DIE中,而MCH剩余的部分与ICH合并成为PCH(Peripheral Controller Hub)。但是从体系结构的角度上看,这些升级与整合并不重要。

目前Intel在Menlow[19]平台基础上,计划推出基于SoC架构的x86处理器,以进军手持设备市场。在基于SoC构架的x86处理器中将逐渐淡化Chipset的概念,其拓扑结构与典型的SoC处理器,如ARM和PowerPC处理器,较为类似。

相关推荐