图2-4 MPC8548处理器存储器域到PCI域的转换在介绍MPC8548处理器如何使用Outbound寄存器组进行存储器域地址空间到PCI总线域地址空间的转换之前,本节将首先介绍Outbound寄存器组中的相应寄存器。该位是Outbound窗口的使能位,为1表示当前Outbound寄存器组描述的存储器地址空间到PCI总线地址空间的映射关系有效;为0表示无效。检查LAWBAR和LAWAR寄存器,判断当前36位的物理地址是否属于PCI总线空间。......

2023-10-20

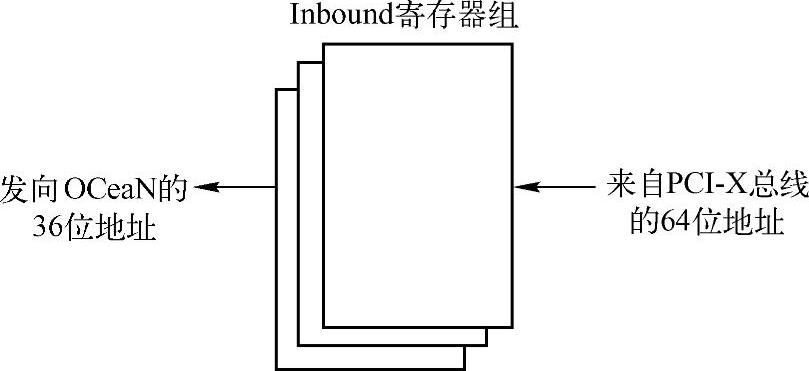

MPC8548处理器使用Inbound寄存器组将PCI总线域地址转换为存储器域的地址。PCI设备进行DMA读写时,只有访问的地址在Inbound窗口中时,HOST主桥才能接收这些读写请求,并将其转发到存储器控制器。MPC8548处理器提供了3组Inbound寄存器,即提供3个Inbound寄存器窗口,实现PCI总线地址到存储器地址的反向映射。

从PCI设备的角度来看,PCI设备访问存储器域的地址空间时,首先需要通过Inbound窗口将PCI总线地址转换为存储器域的地址;而从处理器的角度来看,处理器必须将存储器地址通过Inbound寄存器组反向映射为PCI总线地址空间,才能被PCI设备访问。

PCI设备只能使用PCI总线地址访问PCI总线域的地址空间。HOST主桥将这段地址空间通过Inbound窗口转换为存储器域的地址之后,PCI设备才能访问存储器域地址空间。这个地址转换过程如图2-5所示。

图2-5 MPC8548处理器PCI域到存储器域的转换

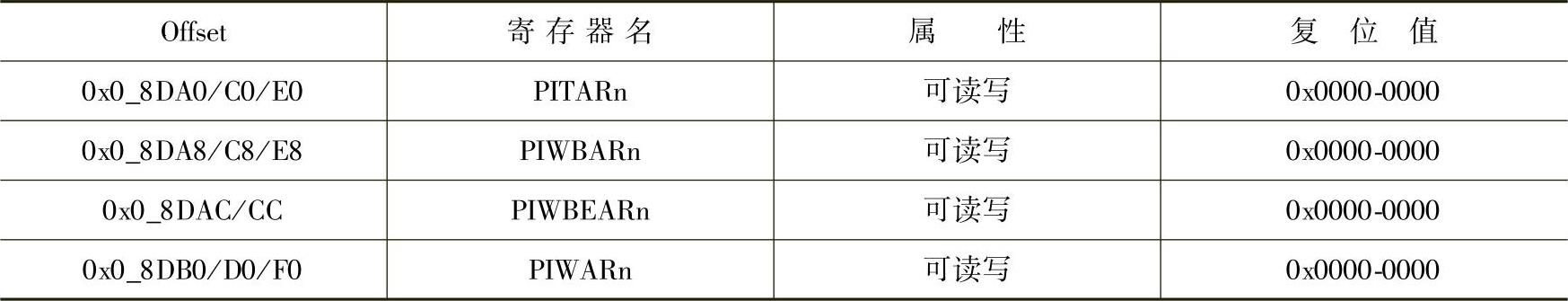

在介绍MPC8548处理器如何使用Inbound寄存器组进行PCI总线域地址空间到存储器域地址空间的转换之前,我们首先简要介绍Inbound寄存器组中的相应寄存器。该组寄存器的地址偏移、属性和复位值如表2-3所示。

表2-3 PCI/X ATMU Inbound寄存器组

值得注意的是,Inbound寄存器组除了可以进行PCI总线地址空间到存储器域地址空间的转换之外,还可以转换分属不同PCI总线域的地址空间,以支持PCI总线的Peer-to-Peer数据传送方式。

1.PITARn寄存器

PITARn寄存器保存当前Inbound窗口在存储器域中的36位地址空间的基地址,其地址窗口的大小至少为4KB,因此在该寄存器中仅存放存储器域地址的第0~23位,该寄存器的主要字段如下所示。

●TEA字段存放存储器地址空间的第0~3位。

●TA字段存放存储器地址空间的第4~23位。

2.PIWBARn和PIWBEARn寄存器

PIWBARn和PIWBEARn寄存器保存当前Inbound窗口在PCI总线域中的64位地址空间的基地址的第63~12位,Inbound窗口使用的最小地址空间为4KB,因此在这两个寄存器中不含有PCI总线地址空间的第11~0位。这两个寄存器的主要字段如下所示。

●PIWBARn寄存器的BEA字段存放PCI总线地址空间的第43~32位。

●PIWBARn寄存器的BA字段存放PCI总线地址空间的第31~12位。(www.chuimin.cn)

●PIWBEARn寄存器的BEA字段存放PCI总线地址空间的第63~44位。

3.PIWARn寄存器

PIWARn寄存器描述当前Inbound窗口的属性,该寄存器由以下位和字段组成。

●EN位,第0位。该位是Inbound窗口的使能位,为1表示当前Inbound寄存器组描述的存储器地址空间到PCI总线地址空间的映射关系有效;为0表示无效。

●PF位,第2位。该位为1表示当前Inbound窗口描述的存储区域支持预读;为0表示不支持预读。

●TGI字段,第8~11位。该字段为0b0010表示当前Inbound窗口描述的存储区域属于PCIe总线域地址空间;为0b1100表示当前Inbound窗口描述的存储区域属于RapidIO总线域地址空间。该字段对于OCeaN实现不同域间的报文转发非常重要,如果当前Inbound窗口的TGI字段为0b0010,此时PCI总线上的设备可以使用该Inbound窗口,通过OCeaN直接读取PCIe总线的地址空间,而不需要经过SoC平台总线。如果TGI字段为0b1111表示Inbound窗口描述的存储器区域属于主存储器地址空间,这也是最常用的方式。使用该字段可以实现HOST主桥的Peer-to-Peer数据传送方式。

●RTT字段和WTT字段,分别为该寄存器的第12~15位和第16~19位。Inbound窗口的RTT/WTT字段的含义与Outbound窗口的RTT/WTT字段基本类似。只是在Inbound窗口中可以规定PCI设备访问主存储器时,是否需要进行Cache一致性操作(Cache Lock and Allocate),在进行DMA写操作时,数据是否可以直接进入Cache。该字段是PowerPC处理器对PCI总线规范的有效补充,由于该字段的存在,PowerPC处理器的PCI设备可以将数据直接写入Cache,也可以视情况决定DMA操作是否需要进行Cache共享一致性操作。

●IWS字段,第26~31位。该字段描述当前窗口的大小,Inbound窗口的大小在4KB~16GB之间,其值为2IWS+1。

4使用Inbound寄存器组进行DMA操作

PCI设备使用DMA操作访问主存储器空间,或者访问其他PCI总线域地址空间时,需要通过Inbound窗口,其步骤如下。

(1)PCI设备在访问主存储器空间时,将首先检查当前PCI总线地址是否在PIW-BARn和PIWBEARn寄存器描述的窗口中。如果在这个窗口中,则将这个PCI总线地址通过PITARn寄存器转换为存储器域的地址或者其他PCI总线域的地址;如果不在将禁止本次访问。

(2)如果PCI设备访问的是存储器地址空间,HOST主桥将来自PCI总线的读写请求发送到存储器空间,进行存储器读写操作,并根据Inbound寄存器组的RTT/WTT位决定是否需要进行Cache一致性操作,或者将数据直接写入到Cache中。

结合Outbound寄存器组,可以发现PCI总线地址空间与存储器地址空间是有一定联系的。如果存储器域地址空间被Inbound寄存器组反向映射到PCI空间,这个存储器地址具有两个地址,一个是在存储器域的地址,一个是在PCI总线域的地址;同理PCI总线空间的地址如果使用Outbound寄存器映射到寄存器地址空间,这个PCI总线地址也具有两个地址,一个是在PCI总线域的地址,一个是在存储器域的地址。

能够被处理器和PCI总线同时访问的地址空间,一定在PCI总线域和存储器域中都存在地址映射。再次强调,绝大多数操作系统将同一个空间的PCI总线域地址和存储器地址设为相同的值,但是这两个相同的值所代表的含义不同。

由此可以看出,如果MPC8548处理器的某段存储器区域没有在Inbound窗口中定义时,PCI设备将不能使用DMA机制访问这段存储器空间;同理如果PCI设备的空间不在Out-bound窗口,HOST处理器也不能访问这段PCI地址空间。

在绝大多数PowerPC处理器系统中,PCI设备地址空间都在HOST主桥的Outbound窗口中建立了映射;而MPC8548处理器可以选择将哪些主存储器空间共享给PCI设备,从而对主存储器空间进行保护。

有关PCI Express体系结构导读的文章

图2-4 MPC8548处理器存储器域到PCI域的转换在介绍MPC8548处理器如何使用Outbound寄存器组进行存储器域地址空间到PCI总线域地址空间的转换之前,本节将首先介绍Outbound寄存器组中的相应寄存器。该位是Outbound窗口的使能位,为1表示当前Outbound寄存器组描述的存储器地址空间到PCI总线地址空间的映射关系有效;为0表示无效。检查LAWBAR和LAWAR寄存器,判断当前36位的物理地址是否属于PCI总线空间。......

2023-10-20

PCI-X总线改变了PCI总线使用的传送协议。PCI-X 1.0总线可以使用的最高总线频率为133MHz,而PCI-X 2.0总线可以使用的最高总线频率为533MHz,远比PCI总线使用的总线频率高。除了信号传送协议外,PCI-X总线在进行DMA读写时,可以不进行Cache共享一致性操作,而PCI总线进行DMA读写时必须进行Cache一致性操作。第3.3节将详细讨论与Cache一致性相关的PCI总线事务。此外PCI-X总线还支持乱序总线事务,即Relaxed Ordering,该总线事务被PCIe总线继承。......

2023-10-20

CPU访问主存储器时,首先将读写命令放入读写指令缓冲中,然后将这个命令发送到DRAM控制器或者HOST主桥。目前处理器系统的DRAM一般由DDR-SDRAM组成,有的书籍也将这部分内存称为主存储器。但是这并不意味着DRAM域一定包含在CPU域中,在某些处理器系统中,CPU并不能访问在DRAM域中的某些数据区域。而CPU域中除了包含DRAM域外,还包含外部设备空间。本书使用存储器域统称CPU域与DRAM域。......

2023-10-20

不过,这里仍然给我们遗留下一个问题:人们所陈述的奶树这个象征符号的意义和与奶树紧密相关的模式化的行为形式之间相互冲突。当地在抽象层面上对奶树象征符号的解释,似乎表示奶树所代表的个人和群体之间不存在不相容或矛盾。但是,如我们所见的,正是这些群体之间的冲突,在奶树下被模拟表演了。......

2024-01-21

假设在一个32位处理器中,存储器域的0xF000-0000~0xF7FF-FFFF这段物理地址空间与PCI总线的地址空间存在映射关系。图3-1 存储器域与PCI总线域的映射关系当PCI设备使用DMA机制访问存储器域地址空间时,处理器系统同样需要将存储器域的地址空间反向映射到PCI总线地址空间。本章采用图3-1的映射关系,虽然增加了映射复杂度,却便于读者深入理解存储器域到PCI总线域之间的映射关系。......

2023-10-20

PCI总线树的枚举由pci_scan_child_bus函数完成,该函数的主要作用是分配PCI总线树的PCI总线号,而并不初始化PCI设备使用的BAR空间。subordinate总线号记载当前PCI总线树中最后一个PCI总线号,因此只有完成了对PCI总线树的枚举后,才能获得该参数。值得注意的是,在Linux系统中,许多PCIe设备并没有提供该结构。PCI总线规范规定了获取BAR空间的标准实现方法。......

2023-10-20

而桥设备的主要作用是管理下游的PCI总线,并转发上下游总线之间的总线事务。PCI总线规范将PCI主从设备统称为PCI Agent设备。PCI规范也没有规定如何设计HOST主桥。在PCI总线中,还有一类特殊的设备,即桥设备。本书重点介绍PCI桥,而不介绍其他桥设备的实现原理。PCI桥的出现使得采用PCI总线进行大规模系统互连成为可能。其中对PCI设备配置空间的访问可以从上游总线转发到下游总线,而数据传送可以双方向进行。......

2023-10-20

而这个PCI桥的Secondary Bus在接收Dock设备的请求时仍然使用正向译码方式。PCI桥使用的正向译码方式与PCI设备使用的正向译码方式有所不同。值得注意的是,PCI总线并没有规定HOST主桥使用正向还是负向译码方式接收这个存储器读写总线事务,但是绝大多数HOST主桥使用正向译码方式接收来自下游的存储器读写总线事务。......

2023-10-20

相关推荐