【摘要】:1)异步串行通信的通信协议包括软协议和硬协议。异步通信的硬协议则是通信双方通过联络线进行通信的,即“请求发送”和“数据就绪”一对联络线。图7-31 用两片74HC574实现单片机与DSP并行通信的接口电路图7-31中使用接口芯片是两片锁存器74HC574,分别用于单片机向DSP及DSP向单片机交换数据的锁存。74HC574为高速的CMOS芯片,兼具TTL的高速与CMOS的低功耗的优点。

在弧焊电源数字控制系统中,可以实现焊接工艺的网络化管理与控制,实现外部PC机给定最佳的焊接参数,可以实现弧焊电源数字控制系统的软件更新与在线升级等。因此,通信技术是弧焊电源数字控制中的重要技术之一,不仅如此,在双控制器数字控制系统中,也存在着控制器之间的通信技术问题。本节仅对单片机与DSP的通信技术进行简单介绍。

单片机和DSP双控制系统与单一DSP控制系统相比,其综合处理能力更强,存储的焊接参数和焊接控制程序更多,功能更强,控制速度更快,但系统比较复杂。单片机和DSP双系统控制的关键之一是单片机与DSP之间的通信技术。这是因为只有可靠地通信、传送数据,系统才能有效地进行控制。

数字化弧焊电源的单片机和DSP构成主从式硬件系统;单片机作为主机,而DSP则作为从机。主机可以控制从机的复位、运行和挂起;从机在主机的控制下完成所分担的工作。

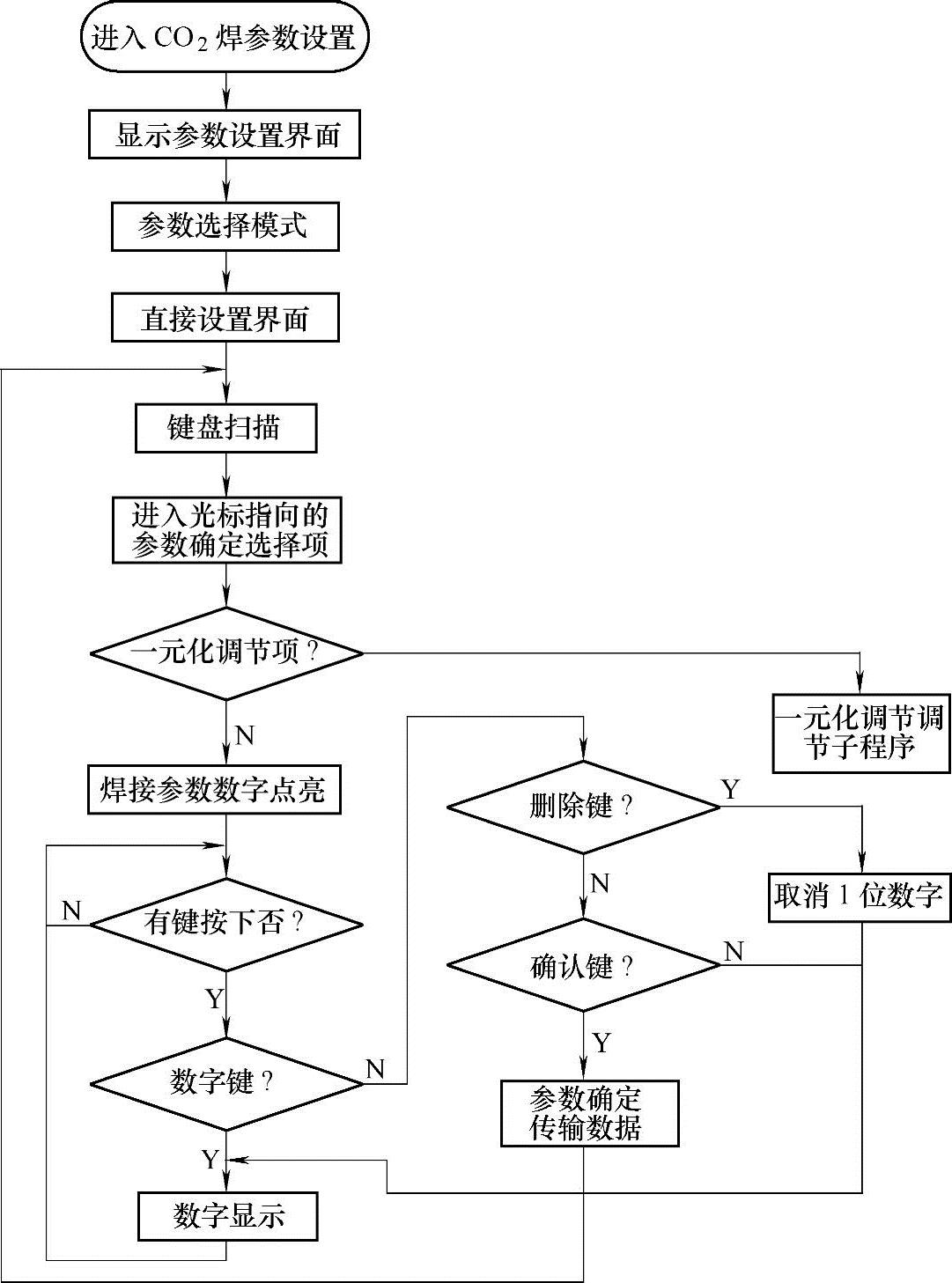

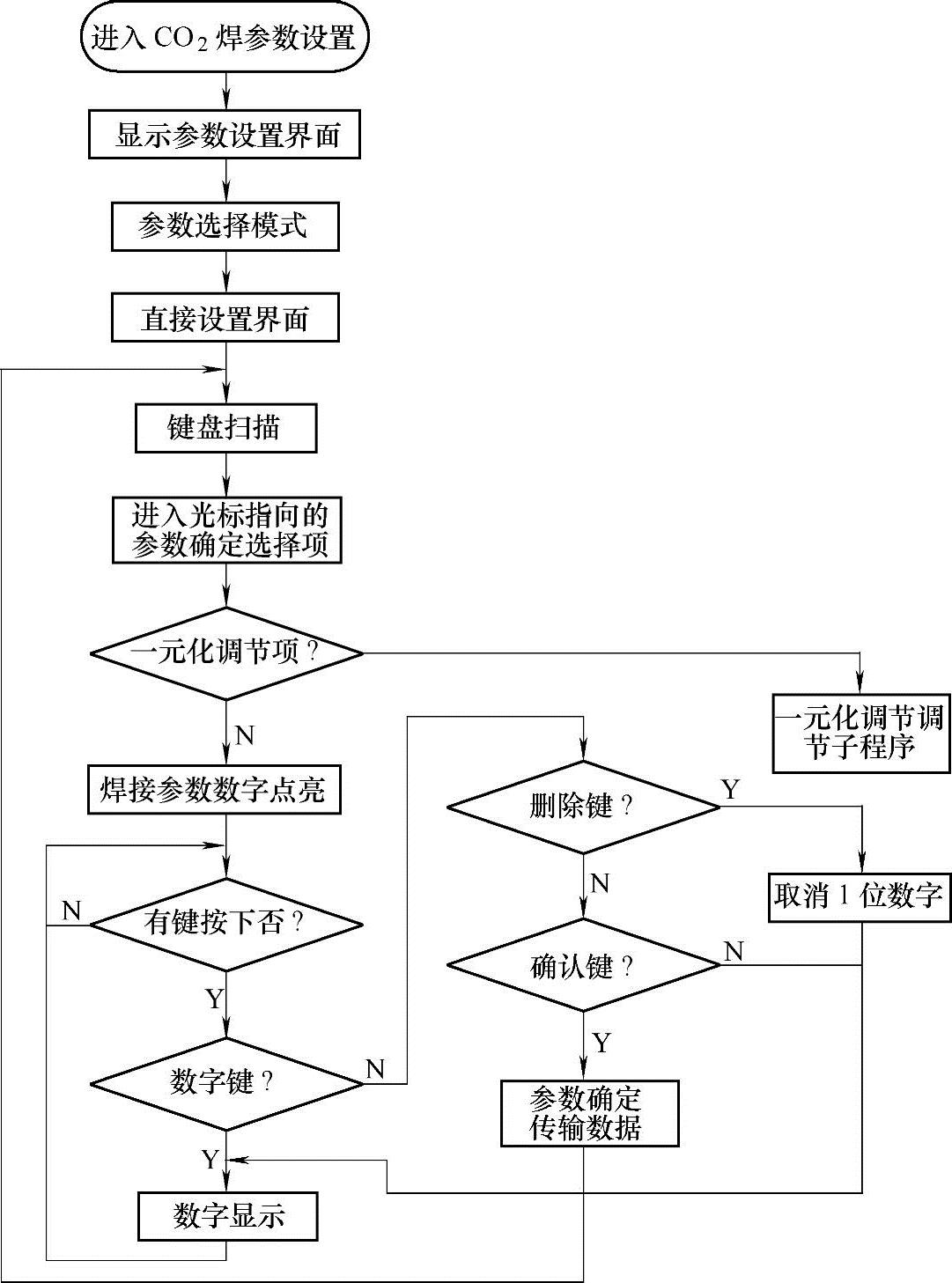

图7-29 CO2焊接人机交互程序流程图

主从式系统中,实现双机通信的方式主要有以下几种:

(1)串行通信 串行通信是利用处理器本身提供的串行口或在芯片内的基础上用软件或硬件开发一个串行口实现双机通信。该方式比较简单,适合于双机通信量不大的场合。

串行通信又分为异步串行通信和同步串行通信。

1)异步串行通信的通信协议包括软协议和硬协议。软协议异步通信的数据传递是按照“帧”的形式传递的。所谓“帧”就是带有格式信息的数字字符,每个数据字符的格式为一个起始位,一个或两个停止位,可选的奇偶校验位和地址位。通信双方事先约定数据字符的格式,并可随时进行数据发送和接收。软协议的异步通信只需两根通信线(即发送信号线和接收信号线)就能方便地完成通信。

异步通信的硬协议则是通信双方通过联络线进行通信的,即“请求发送”和“数据就绪”一对联络线。

TMS320LF2407A DSP的串口通信模块的寄存器是8位的,其串行通信口是一个标准的通用异步通信接口。其接收器和发送器是双缓冲的,每个都有它自己的独立使能和中断位,两者均可以独立工作,或者在全双工模式下工作。

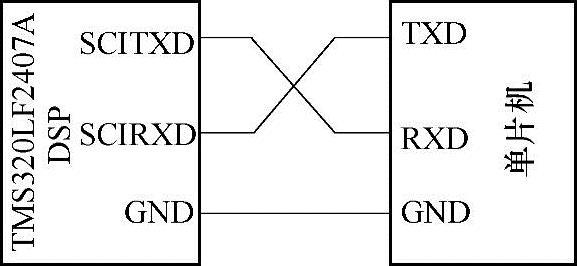

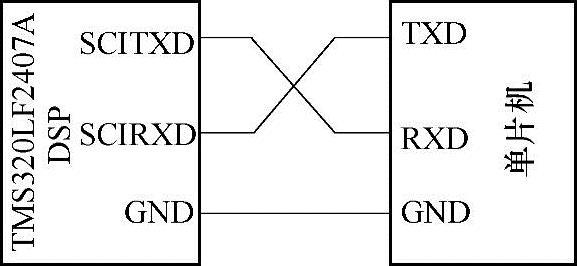

图7-30所示是单片机与DSP之间采用异步串行通信的连线图。在该系统中,单片机与TMS320LF2407A DSP之间的通信采用了软协议的串行异步数字通信方式,单片机的发送端TXD和接收端RXD分别与DSP的接收端SCIRXD和发送端SCITXD相连,而且单片机与DSP共“地(GND)”。

图7-30 单片机与DSP的通信连线

由于单片机和TMS320LF2407A DSP的接收器和发送器可以由中断控制,因此可以采用中断方式进行单片机与DSP的通信控制。

2)同步串行通信协议基于通信双方约定同一通信时间、同一通信频率,在同步时钟的作用下,数据以串行的方式从一个控制器传递到另一个控制器。在这种方式下,无论接收器还是发送器均至少需要三根信号线,即时钟信号线、数据接收信号线及数据发送信号线。

有的TMS32OLF240×型DSP包含带4个引脚的串行外设接口(SPI)模块。SPI是一个高速、同步串行I/O口,通常SPI用于DSP处理器和外设及其他处理器之间的通信。

利用TMS320F(C)240×系列DSP的SPI口可以实现与单片机之间的同步串行通信,但目前在数字化弧焊电源的设计中很少采用。

(2)并行通信 并行通信是利用处理器的I/O功能,在单片机和DSP之间增加缓冲器或锁存器实现双机通信。与串行通信方式相比,该方式的通信效率稍高些。

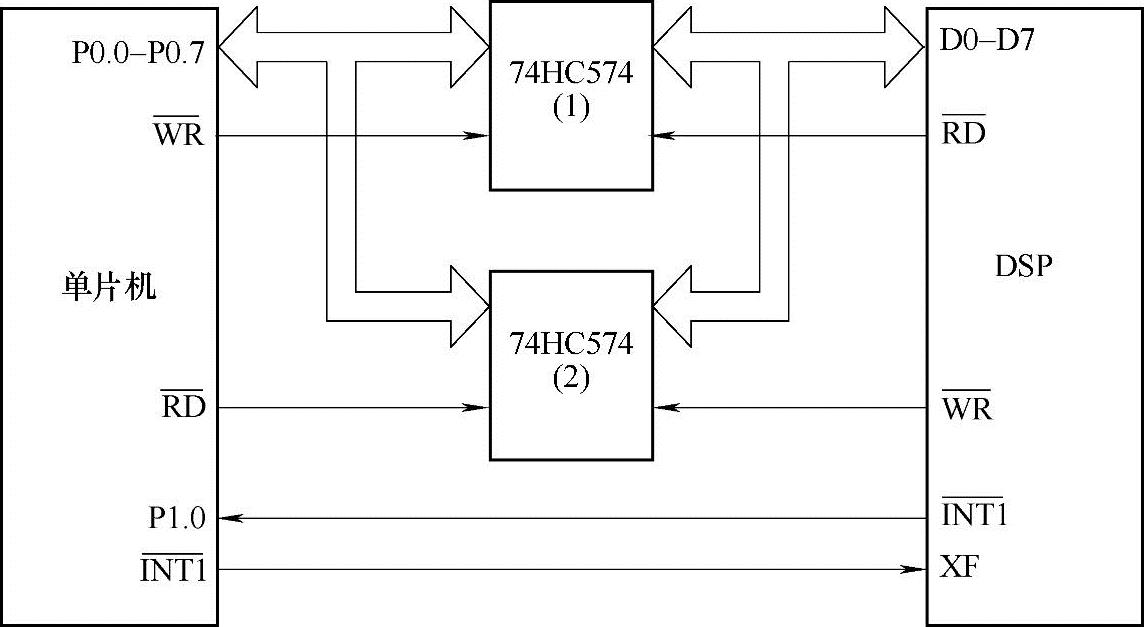

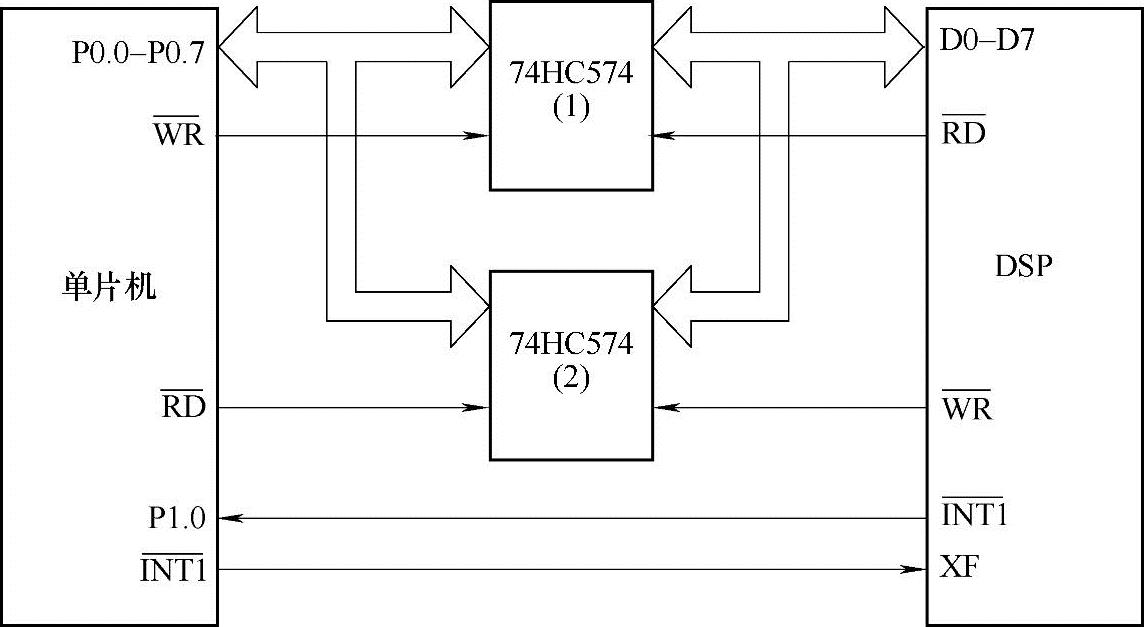

1)可以采用简单的TTL芯片实现的并行通信。用TTL芯片实现单片机系统与DSP系统之间进行并行通信的接口电路如图7-31所示。

图7-31 用两片74HC574实现单片机与DSP并行通信的接口电路

图7-31中使用接口芯片是两片锁存器74HC574,分别用于单片机向DSP及DSP向单片机交换数据的锁存。74HC574为高速的CMOS芯片,兼具TTL的高速与CMOS的低功耗的优点。

单片机→DSP:单片机将数据锁存至74HC574(1),通过P1.0向DSP申请中断,DSP响应中断将数据读入。

DSP→单片机:DSP将数据锁存至74HC574(2),然后通过XF向单片机申请中断,单片机响应中断将数据读入。

这种通信方式接口电路简单,价格低,体积小巧,适合通信距离短、数据传输速率不高的系统。

2)用双端口RAM实现的并行通信。双端口RAM作为一种特殊的RAM芯片,在高速数据采集处理系统中得到广泛的应用。它具有两个独立的端口,各自均有一套独立的数据总线、地址总线和控制总线,允许两个端口独立地对存储器中的任何单元进行存取操作。当两个端口同时对存储器中的同一单元进行存取操作时,可由其内部仲裁逻辑决定优先权。即当两组地址总线完全相同时,片内总线仲裁逻辑向后访问的一方发出等待信号,使该方进入等待,另一方访问结束之后等待信号撤销,等待方继续访问这一地址。双口RAM的特殊结构使得双机可以方便快速地进行数据交换,大大提高了双CPU之间的并行处理能力。

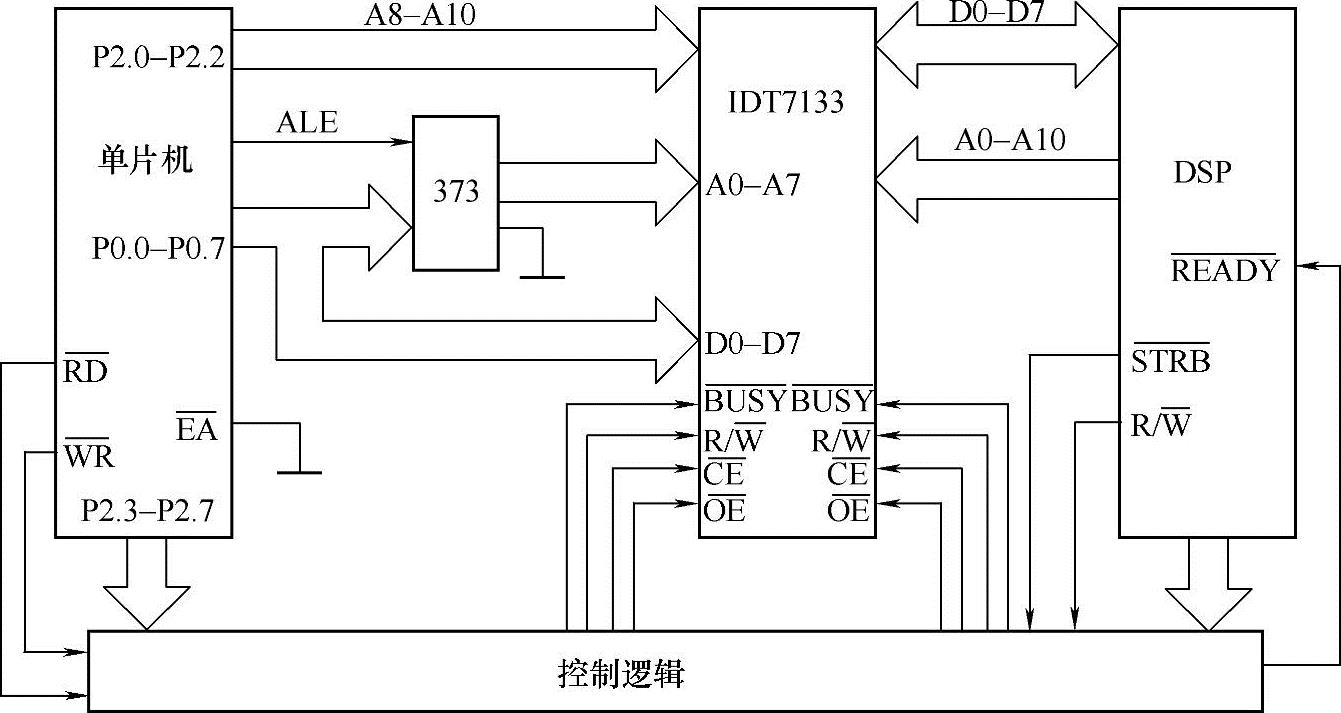

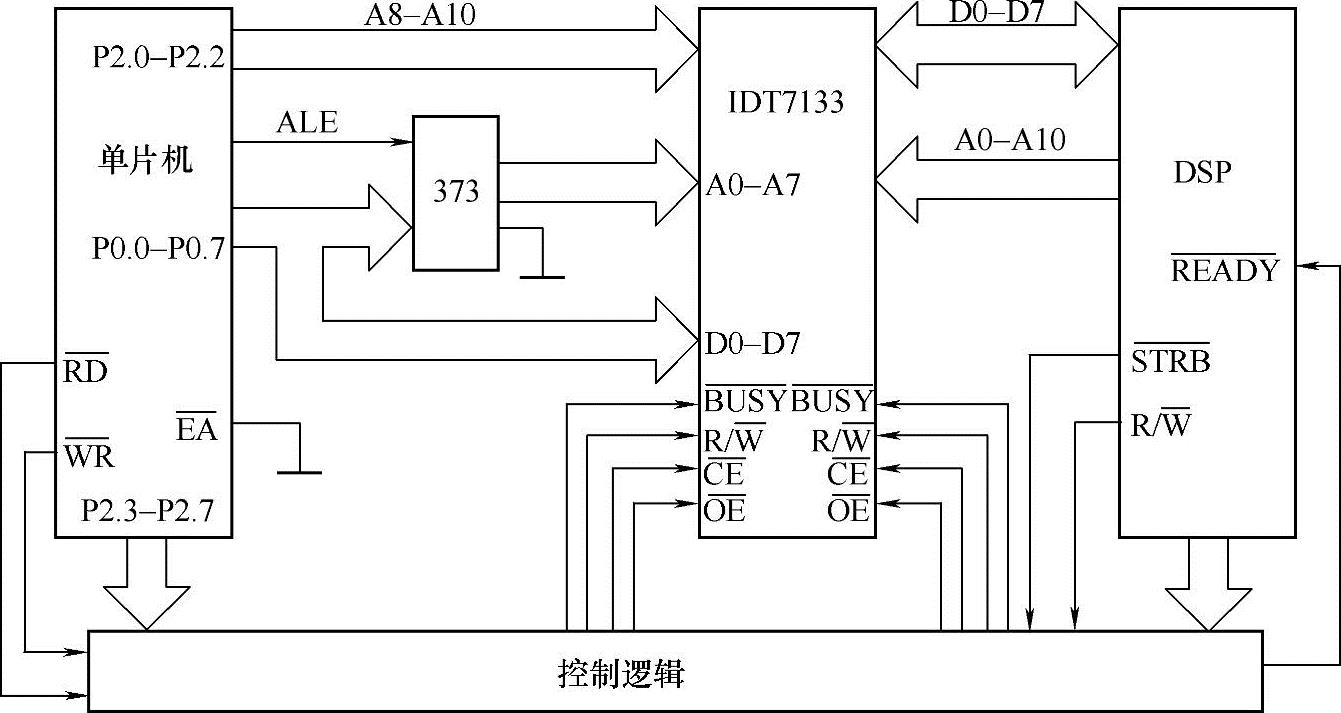

图7-32所示是采用IDT(Integrated Device Technology)公司的IDT7133双口RAM实现的双机并行通信接口电路图。IDT7133是高速2K×16位的双口RAM,它提供的地址线、控制线及I/O线是完全独立的两个接口,可支持对器件的任何存储空间进行的完全异步的读写操作。当双口RAM的两个接口同时对存储器的同一单元进行操作时,IDT7133的忙逻辑(BUZY)将会有一个硬件的指示,允许其中的一个端口先进行操作,而用BUSY指示将另一个端口置于等待状态,直到另一个端口完成相应的操作。如果在接到BUSY信号时,已经进行写操作,那么IDT7133的内部机制可以阻止写操作的继续进行,以保证数据传输的准确性。此种接口电路可加速数据传输速率,而且可以简化总线结构,又具有体积小、功能强等优点,适合近距离、大量和快速交换数据的系统。

图7-32 用双口RAM实现单片机与DSP之间并行通信的接口电路

(3)共享存储器方式 共享存储器方式又可以分成两种:一种是主机和从机不能同时访问共享存储器;另一种是主机和从机可以同时访问共享存储器(当然不能同时访问同一个单元)。前一种共享存储器方式通常是利用DSP提供的DMA功能,而后者则采用双端口存储器(RAM)来实现。

相关推荐