1.系统的组成根据系统的主要技术指标和功能,本系统为一个8路数据实时采集系统,系统选用AT89C52单片机为主机。由于AT89C52片内具有8KB的程序存储器,所以系统不需要外部扩展程序存储器。2.系统的工作原理图10-16系统总体结构框图本系统设计采用定时采样控制方式进行工作,每隔0.5s对8路模拟量进行巡回采集1次。图10-19DAC0832的电压输出电路图打印机的选择在单片机系统中,经常选用微型打印机,如PP40、GP16等。......

2023-11-17

1.DSP工作的基本原理与系统结构

DSP是一种特殊的单片机,其工作的基本原理与普通的单片机是一致的。其工作过程无非是从一个指定的区域(存储器、I/O接口等)读取数据,利用这些数据并且按照一定的控制算法进行计算,并将计算的最终结果通过输出端口对被控对象进行控制。在数字化逆变弧焊电源系统的DSP控制中,可以利用DSP直接输出所需的PWM信号,对弧焊逆变器中的功率半导体开关器件的通断进行控制,从而获得所需的输出电流或电压。

DSP控制采用了数据总线和地址总线,数据和地址信息分别在两条总线上流动。挂在这两条总线上的模块有DSP的中央处理单元(CPU)、程序存储器、数据存储器以及内部外设等功能模块。程序存储器包括芯片内部存储器和外部存储器。程序存储器存储人为编写的程序代码,使得DSP控制器能够按照人的意志进行相应的工作。CPU根据程序的流程控制数据和地址总线的占用情况,同时进行一些相关的运算。数据存储器用于存储计算、控制过程中所要使用的数据,如初始化数据、计算中间结果和最终结果等。片内外设为集成在片内的与芯片外部进行数据交换的功能模块,如数字I/O、PWM输出以及通信等。

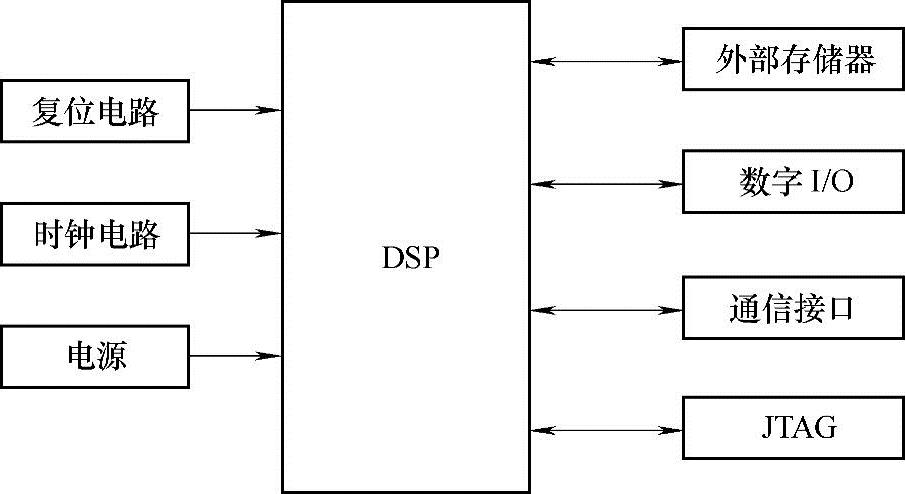

DSP控制系统包括硬件系统和软件系统。图7-3所示是一个典型的DSP控制硬件系统结构框图。由图可见,一般典型的DSP硬件系统包括复位电路、时钟电路、电源、外部存储器、数字I/O接口、仿真(JTAG)接口以及各种通信接口电路。

图7-3 典型的DSP控制系统框图

2.最小硬件系统

DSP最小硬件系统包括DSP芯片、复位电路、时钟电路、电源等。

(1)DSP系统的电源 DSP芯片一般需要+5V或+3.3V直流电源供电。多数DSP芯片为+3.3V直流电源供电,如TMS320LF2407A。由于DSP芯片的外围电路往往需要+5V直流电源,因此DSP控制系统一般需要+5V和+3.3V直流电源。

用于DSP系统的电源,一般要采用DC/DC变换,即对整流器获得的直流电压进行隔离与稳压处理。可以采用一些专用的升/降压DC/DC变换器件,获得所需的电源电压。同时还要对控制电路板的布局、布线提出一定要求,在模拟电源(VDD)和数字电源(VCC)之间、模拟地(AGND)和数字地(DGND)之间加滤波电容,减少噪声干扰。

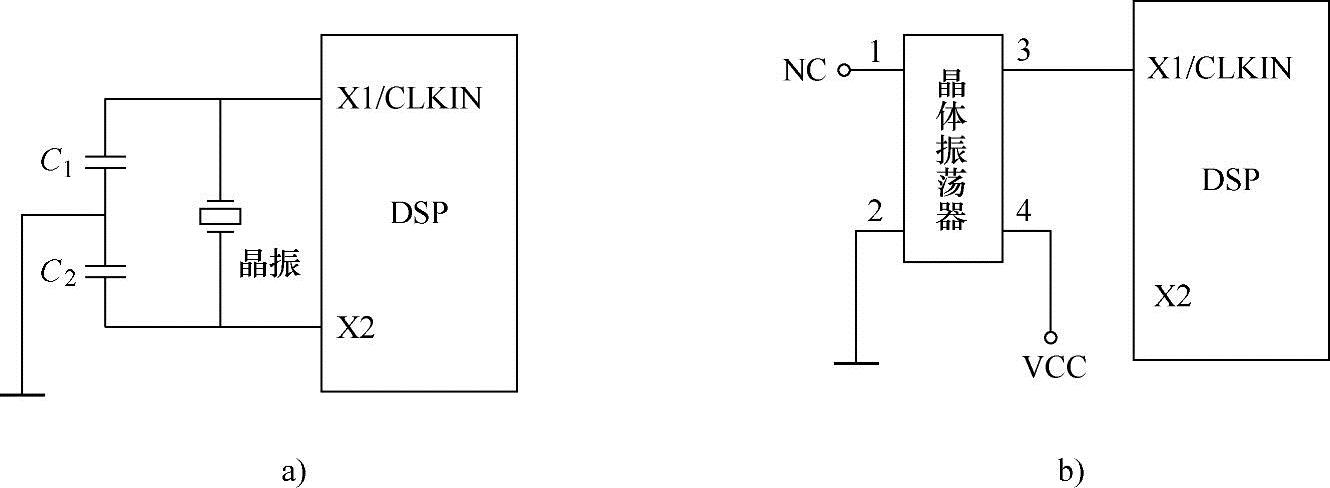

(2)时钟电路 给DSP芯片提供时钟一般有两种方法。一种是利用DSP芯片内部所提供的晶振电路,在DSP芯片的X1/CLKIN和X2之间连接一个晶振可启动内部振荡器,如图7-4a所示。另一种方法是将外部晶体振荡器直接连接X1/CLKIN引脚,X2悬空,如图7-4b所示。

图7-4 时钟电路

a)内部振荡电路 b)外部振荡器电路

需要注意的是,DSP的工作频率是在其内部利用锁相环(PLL)将外部晶振频率进行倍频处理后的频率。

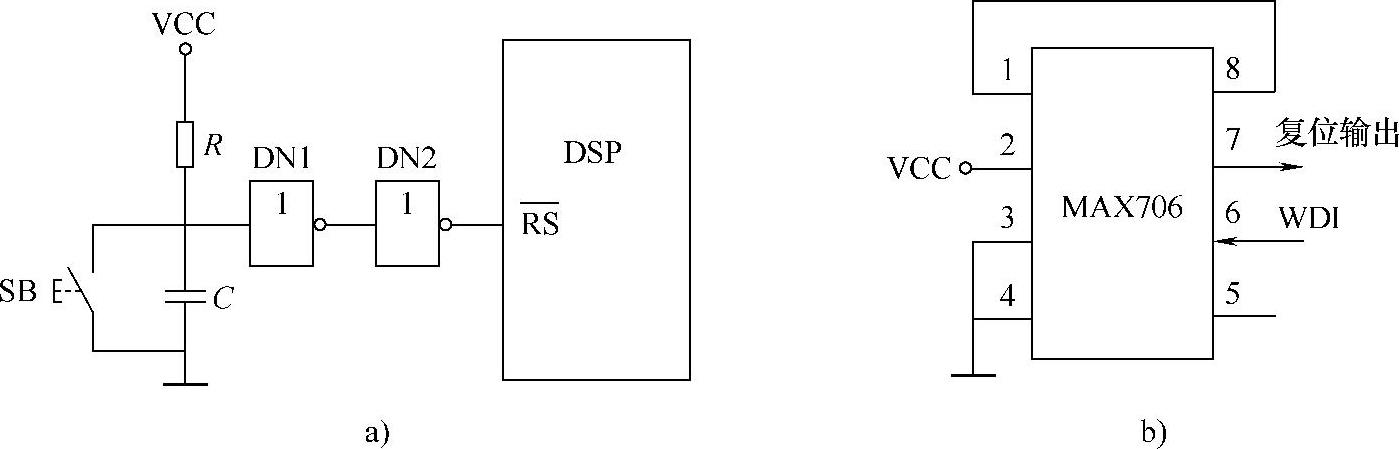

(3)复位电路 DSP复位信号有两种:上电复位和手动复位。一般是将上电复位和手动复位信号直接送到DSP的复位输入引脚 。图7-5a给出了一种带有上电延迟复位和手动复位功能的复位电路。

。图7-5a给出了一种带有上电延迟复位和手动复位功能的复位电路。

如图7-5a所示,在电源刚接通的瞬间,非门DN1的输入端为低电平,非门DN2输出端也为低电平,则DSP的复位端 为低电平,DSP处于复位状态。电源接通后,电源VCC通过电阻R向电容C充电,待电容C上的电压达到一定值时,非门DN2向DSP的复位端输出高电平信号,使DSP系统处于工作状态。在工作过程中,需要DSP系统复位时,按下人工复位按钮SB,电容C通过SB放电,使DSP的复位端变为低电平,DSP处于复位状态;松开SB,电源VCC通过电阻R向电容C充电,待电容C上的电压达到一定值时,DSP的复位端变为高电平,DSP系统处于工作状态。

为低电平,DSP处于复位状态。电源接通后,电源VCC通过电阻R向电容C充电,待电容C上的电压达到一定值时,非门DN2向DSP的复位端输出高电平信号,使DSP系统处于工作状态。在工作过程中,需要DSP系统复位时,按下人工复位按钮SB,电容C通过SB放电,使DSP的复位端变为低电平,DSP处于复位状态;松开SB,电源VCC通过电阻R向电容C充电,待电容C上的电压达到一定值时,DSP的复位端变为高电平,DSP系统处于工作状态。

在复位电路中,除了上电自动复位和人工复位的功能以外,往往还应具有监视系统运行并在系统发生故障或死机时,能够进行自动复位的功能。其基本原理就是通过电路提供一个用于监视系统运行的监视线,当系统正常运行时,应在规定的时间内给监视线提供一个高低电平发生变化的信号;如果在规定时间内,这个信号不发生变化,自动复位电路就认为系统运行不正常并重新对系统进行复位操作。根据此原理,可以采用555定时器及计数器等器件,设计相应的自动复位电路,或采用专用的自动复位电路集成芯片(如MAX706)构成自动复位电路(见图7-5b)。该复位电路称为具有监视(Watchdog)功能的自动复位电路。

图7-5 复位电路

a)上电与手动复位电路 b)具有Watchdog功能的复位电路

3.接口电路

DSP控制系统除了具有最小硬件系统外,还具有外围接口电路,如数字I/O端口、模数转换(ADC)接口、仿真(JTAG)接口以及与其他处理器之间的各种通信接口等。本节仅简介仿真JTAG接口、外部存储器SRAM接口。其他接口请参考相关的DSP接口设计的书籍。

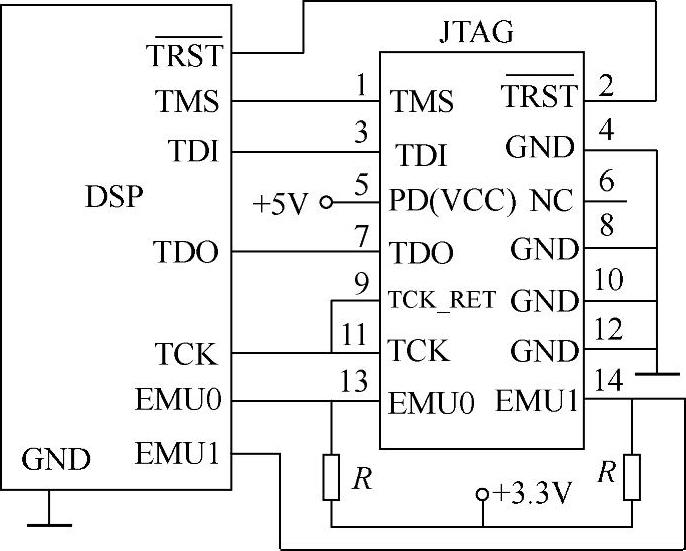

(1)DSP与JTAG接口 同其他的单片机应用系统一样,DSP控制系统必须具有仿真器的标准接口,通过这个接口,可以将用户的DSP系统控制板与PC机连接,应用安装在PC机上的专用开发软件,在线编制和调试用户的软件程序。

图7-6给出了DSP控制系统的JTAG接口与控制板中DSP芯片连接的原理图。

如图所示,JTAG接口模块引脚的功能如下:EMU0与EMU1引脚需要3.3V上拉;GND引脚是仿真器与DSP用户系统的共“地”信号连线;PD(VCC)引脚要连接控制板上+5V电源;TCK为测试时钟引脚,该信号来自仿真器;TCK_RET为测试时钟返回引脚;TDI为测试数据输入引脚;TDO为测试数据输出引脚;TMS为测试模式选择引脚;TRST为测试复位引脚。

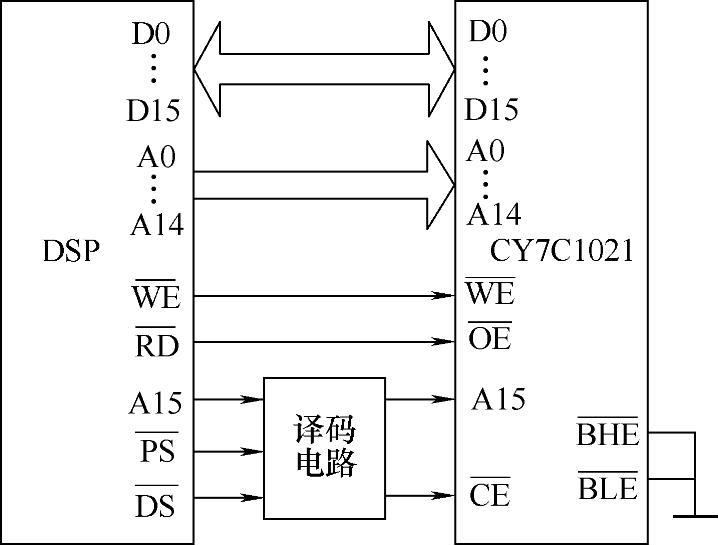

(2)DSP与外部存储器SRAM接口 因为在TMS320LF2407A DSP芯片内部具有1.5K字的程序/数据RAM、544字的DARAM和2K字的SARAM,以及32K字的Flash程序存储器,所以一般的控制系统无须在片外扩展程序和数据存储器。但是,在控制系统的开发阶段,在DSP芯片外部扩展一个片外的程序存储器以存储被调试的软件代码,可以避免对片内FLASH的频繁写入操作,从而可以节约开发时间,并且可以防止对片内FLASH的过度擦写而延长DSP芯片的寿命。另外,如果需要存储大量的控制数据,也需要外部存储器。

SRAM是DSP最常用的外部存储设备,它具有接口简单、读写速度快等优点。常用的SRAM有IDT7128、CY7C1024、CY7C1021等。

静态的CY7C1021是高性能16位的CMOS静态SRAM,对其可以进行几种模式的读与写的操作。例如:当输入信号 以及

以及 同时为低电平时,写选通该芯片。如果低字节使能位

同时为低电平时,写选通该芯片。如果低字节使能位 和高字节使能位

和高字节使能位 都为低电平时,低8位和高8位数据端口全部选通,即将来自I/O0~I/O15的数据写入到地址引脚A0~A15所指定的位置;当输入信号CE以及OE同时为低电平、而W

都为低电平时,低8位和高8位数据端口全部选通,即将来自I/O0~I/O15的数据写入到地址引脚A0~A15所指定的位置;当输入信号CE以及OE同时为低电平、而W 为高电平时,读选通该芯片。如果低字节使能位B

为高电平时,读选通该芯片。如果低字节使能位B 和高字节使能位

和高字节使能位 都为低电平时,低8位和高8位数据端口全部选通,存储器中指定位置中的数据将出现在I/O0~I/O15上。

都为低电平时,低8位和高8位数据端口全部选通,存储器中指定位置中的数据将出现在I/O0~I/O15上。

图7-7给出了CY7C1021SRAM与DSP连接的接口电路。

如图可见,该电路每次读、写操作的是整个16位数据。通过译码电路将64KB的SRAM空间可以分为两个地址区间(由地址的最高位A15确定),即数据区和程序区,具体区间的划分由用户的译码方法决定,DSP可方便地对SRAM进行读写操作。

图7-6 JTAG接口与控制板中DSP的连接图

图7-7 CY7C1021SRAM与DSP连接的接口电路

有关现代弧焊电源及其控制的文章

1.系统的组成根据系统的主要技术指标和功能,本系统为一个8路数据实时采集系统,系统选用AT89C52单片机为主机。由于AT89C52片内具有8KB的程序存储器,所以系统不需要外部扩展程序存储器。2.系统的工作原理图10-16系统总体结构框图本系统设计采用定时采样控制方式进行工作,每隔0.5s对8路模拟量进行巡回采集1次。图10-19DAC0832的电压输出电路图打印机的选择在单片机系统中,经常选用微型打印机,如PP40、GP16等。......

2023-11-17

硬件测试系统包含本项目所使用的硬件设备,主要包括传感器、信号调理器、数据采集设备和计算机等部分。物流包装材料无害化生产过程数据采集系统硬件设备主要包括塑料注塑成型机、计算机、数据采集卡、传感器、信号调理器等。通过数据采集卡获取数据是主要的渠道,系统采用了NI公司基于PCI总线的数据采集卡PCI6221以及USB接口的数据采集卡USB6221,采集卡集成了A-D转换和数字I/O等功能。图6-13 测试系统硬件设计方案表6-3 采集所用的各种传感器......

2023-07-02

图21-10 单片机最小系统电路单片机要正常工作还需要有晶振电路和复位电路,因为没有晶振电路的话,也就没有时钟周期,无法执行程序代码,单片机也就无法工作,单片机的晶振电路是一种典型电路,分为内部时钟方式和外部时钟方式两种,本设计采用的是内部时钟方式,时钟的晶振频率选择11.0592MHz,外接两个30p谐振电容。......

2023-11-04

曲轴系统由连杆、主和副、平衡轴轴承等组成的轴颈轴承和与此接合的轴承盖组成。曲轴轴颈轴承的负荷随活塞作用力大小和方向的改变而发生变化。图9-13 旋转轴承中产生油膜压力的两种形态1.摩擦系数连杆轴颈轴承的负荷和偏心线图如图9-14所示。连杆大头轴承的润滑油是通过旋转的曲轴内部通道供给,油路内的润滑油会产生离心力。......

2023-06-28

下面以图6-8所示的PROFIBUS-DP系统为例,介绍PROFIBUS系统的工作过程。这是一个由多个主站和多个从站组成的PROFIBUS-DP系统,包括2个1类主站、1个2类主站和4个从站。图6-8 PROFIBUS-DP系统实例系统从上电到进入正常数据交换工作状态的整个过程可以概括为以下四个工作阶段。LAS的形成即标志着逻辑令牌环初始化的完成。由DP从站提交的诊断数据包括符合标准的诊断部分以及此DP从站专用的外部诊断信息。图6-10 DP从站报告出现诊断报文的流程......

2023-11-22

图1-4典型液压系统的结构1—油箱;2—过滤器;3—液压泵;4—溢流阀;5—节流阀;6—换向阀; 7—油管;8—液压缸;9—工作台。常见的动力元件有液压泵和空气压缩机。在该液压系统中,电动机(原动机)带动液压泵3旋转,液压泵经过滤器2从油箱1中吸油。被液压泵施加压力后液压油经油管向上送至系统参与工作。油管7的作用则是约束液压油的流动,连接各个器件,组成完整的系统。......

2023-06-25

执行器包括变速杆锁止电磁阀N110、阀体电磁阀、起动/倒车灯继电器及电控系统诊断插头等。其作用是检测自动变速器的工作温度。制动信号还用于变矩器锁止离合器的释放,对于装有自动定速巡航装置的车辆,该信号用于解除定速巡航。各电磁阀的作用、类型、工作条件见表4-1-3。另外,在01N自动变速器中,手动阀用来控制B1、K2。......

2023-08-25

AT89S51是一款低功耗、高性能CMOS 8位单片机,可反复擦写1000次的Flash只读程序存储器。中断控制系统 89S51单片机具有5个中断源,两个中断优先级的中断控制系统,以满足控制应用的需要。时钟电路为单片机产生时钟脉冲序列。本设计中单片机的最小系统设计如图17-2所示。当其输出为1时,光耦合器6N137的OUTPUT脚输出为高电平。当其输出为1时,报警系统关闭。......

2023-11-04

相关推荐